2024年10月22日

Ī├Č\Įč╩¼└ŽĪ╩╚ŠŲ│öü×æēäĪ╦

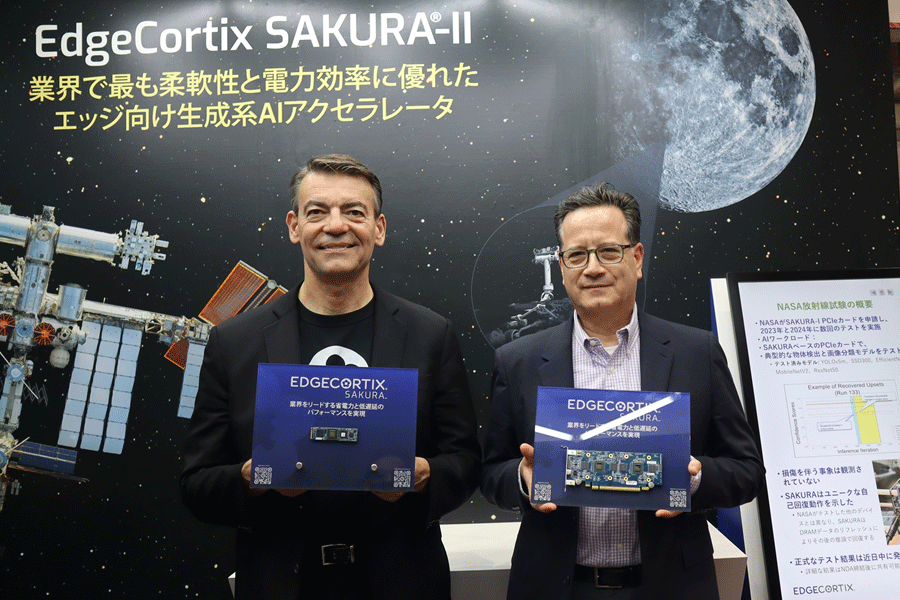

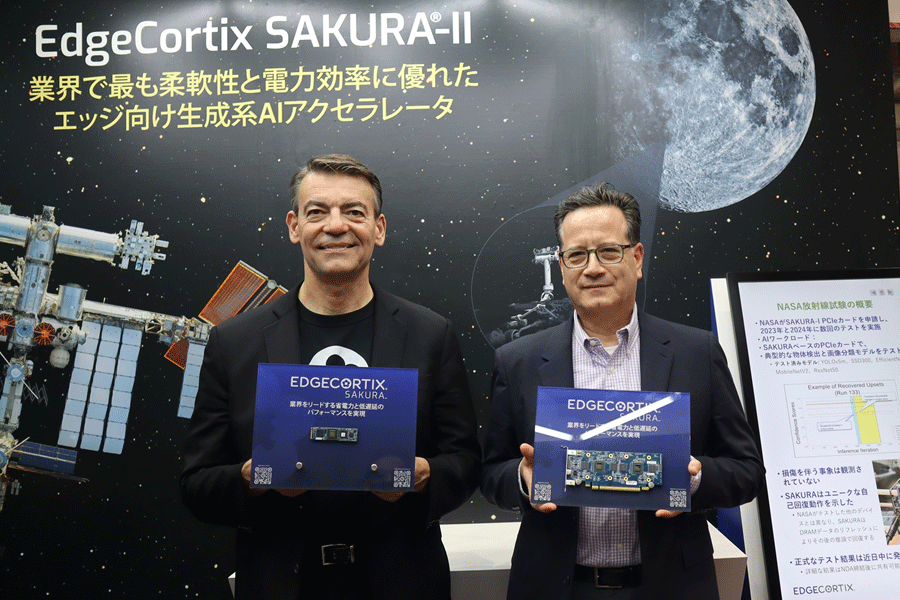

ź©ź├źĖżŪAIż“ŠW(w©Żng)├ōżĘżĶż”ż╚żżż”AIź┴ź├źūż“│½╚»żĘżŲżżżļ╣±ŲŌż╬ź╣ź┐Ī╝ź╚źóź├źūEdgeCortix╝ęĪ╩╗▓╣═½@╬┴1Ī╦ż╬ĪųSAKURA-IĪūż¼╝┬żŽĪó▒¦├Ķ┤─ČŁżŪżŌ╗╚ż©żļż│ż╚ż¼ż’ż½ż├ż┐ĪŻ└ĶĮĄ┼ņ»Bźėź├ź░źĄźżź╚żŪ│½╠¢żĄżņż┐2024╣±║▌Æņȧ▒¦├Ķ·tżŪŲ▒╝ęż¼£½żķż½ż╦żĘż┐ĪŻä▌Æņȧ▒¦├ĶČ╔Ī╩NASAĪ╦ż╬─_źżź¬ź¾żõźūź╚źĒź¾ż“╩³╝o(j©¼)żĄżņż┐┤─ČŁżŪĖ╬ŠŃżĘż╩ż½ż├ż┐ż╬ż└ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年10月16日

Ī├Č\Įč╩¼└ŽĪ╩╚ŠŲ│öü×æēäĪ╦

10źßĪ╝ź╚źļµć┼┘ż╩żķŲ╝└■ż╦żĶżļźĘźĻźóźļ┼┴┴„Å]┼┘ż¼16Gźėź├ź╚/╔├ż╚╣ŌÅ]ż╬źĘźĻź│ź¾×æSerDesĪ╩─Šš`ż½żķ╩┬š`╩č┤╣żóżļżżżŽżĮż╬ĄšĪ╦ź┴ź├źūż¼ź╬źżź║┤─ČŁż╬Ėʿʿżź»źļź▐źßĪ╝ź½Ī╝ż╦║╬├ōżĄżņż┐ĪŻżĮżņżŌź»źļź▐źßĪ╝ź½Ī╝3╝ęż¼║╬├ōżĘż┐ĪŻź┴ź├źūż“└▀╝ŖżĘż┐ż╬żŽźżź╣źķź©źļż╬Valens Semiconductor╝ęż└ĪŻŲ╝└■ż╦żĶżļźŪĪ╝ź┐┼┴┴„ż╬╣ŌÅ]Ų░║ŅżŪżŌź╬źżź║ż╦╔ķż▒ż╩żżĪŻż▐ż┐żĘżŲżŌĖ„źšźĪźżźąż╬┼ąŠņżŽżĄżķż╦äPżėżļż½żŌżĘżņż╩żżĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年10月 9日

Ī├Č\Įč╩¼└ŽĪ╩×æļ]Ī”ĖĪØhäóÅøĪ╦

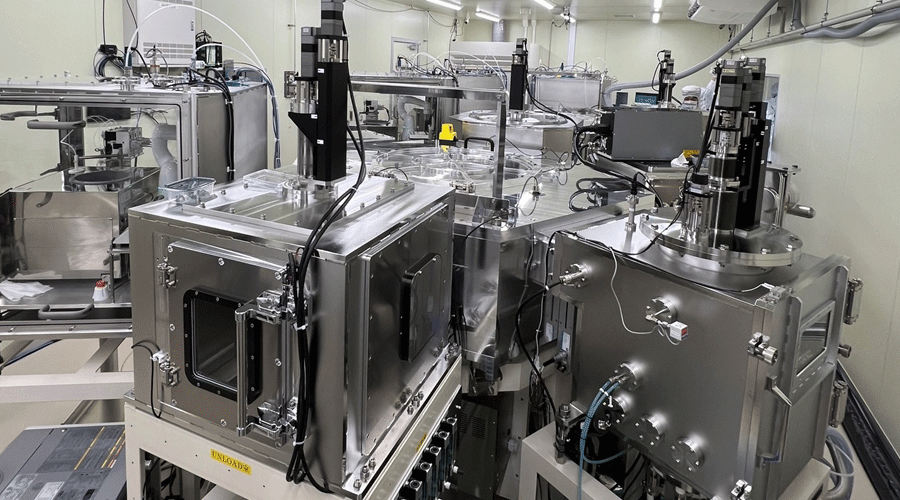

ŠÅČ╚Č\Įč┴Ē╣ńĖ”ē|ĮĻżŽĪóź┌źĒźųź╣ź½źżź╚╣Įļ]ż╬ģ╬═█┼┼├ėż╬╝┬├ō▓Įż╦Ė■ż▒ĪóśOŲ░║Ņ×æźĘź╣źŲźÓż“╗Ņ║ŅżĘż┐ĪŻź┌źĒźųź╣ź½źżź╚ģ╬═█┼┼├ėżŽĪó╩č┤╣Ė·╬©ż¼źĘźĻź│ź¾░╩æųż╬╣ŌżżĖ·╬©ż“┐āż╣╗Ņ║ŅżŽ¾Hżżż¼Īóźąźķż─żŁż¼Įj(lu©░)żŁżżż╚Č”ż╦ĪóĘą╗■╩č▓Įż¼Įj(lu©░)żŁż»╬¶▓ĮżĘżõż╣żżĪóĮj(lu©░)ĀC└čż¼žMżĘżżż╩ż╔ż╬╠õ¼öż¼æč└čż▀ĪŻŠ»żĘżŪżŌŠ}║ŅČ╚ż╦żĶżļ║Ņ×æżŪżŽż╩ż»śOŲ░ĄĪż╦żĶż├żŲźąźķź─źŁż“žō(f©┤)żķż╣┴└żżżŪäóÅøż“│½╚»żĘż┐Ī╩┐▐1)ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年9月13日

Ī├Č\Įč╩¼└ŽĪ╩×æļ]Ī”ĖĪØhäóÅøĪ╦

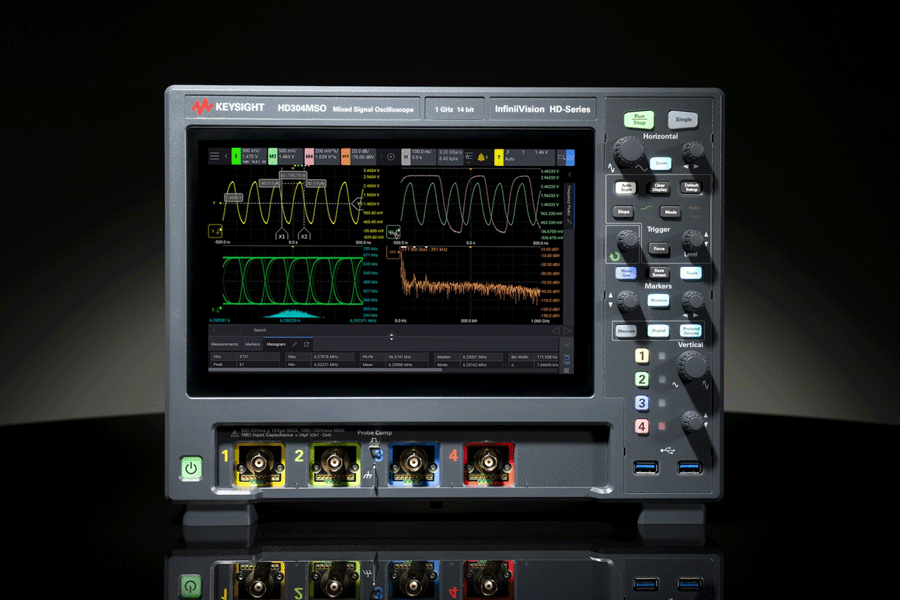

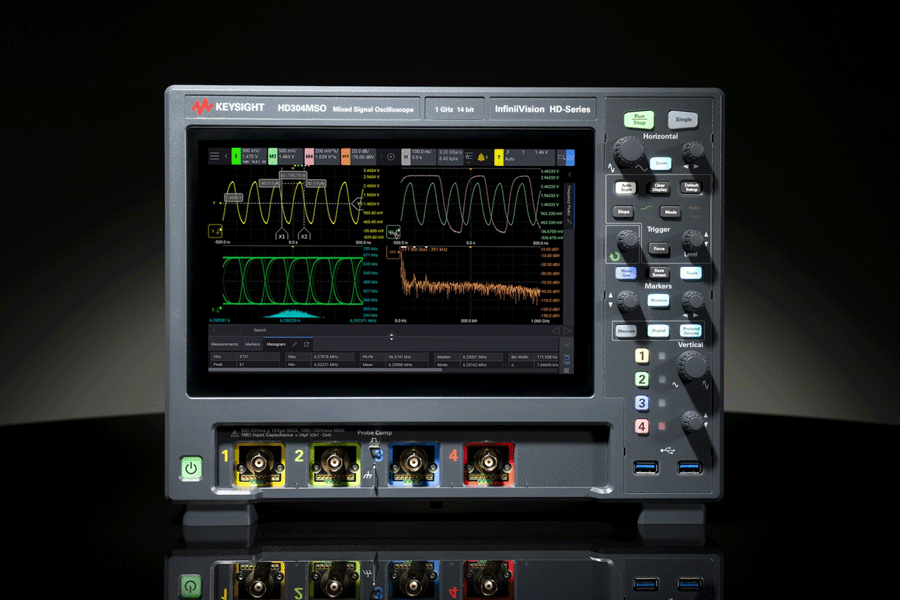

Keysight TechnologiesżŽĪó╝■āS┐¶┬ė░Ķ200MHz~1GHzĪ󟥟¾źūźĻź¾ź░źņĪ╝ź╚3.2GźĄź¾źūźļ/╔├ż╚żżż”2ź┴źŃź¾ź═źļ/4ź┴źŃź¾ź═źļż╬ź¬źĘźĒź╣ź│Ī╝źūĪ╩┐▐1Ī╦ż“137╦³▀ģż½żķ╚»ŪõżĘż┐ĪŻź¬źĘźĒź╣ź│Ī╝źūż╚żżż├żŲżŌFFTż“²Xż▒żņżąź╣ź┌ź»ź╚źķźÓźóź╩źķźżźČż╦ż╩żļæųĪó┐«ęÄ(gu©®)╚»Ö┌▀_(d©ó)żõźĒźĖź├ź»źóź╩źķźżźČĄĪē”żŌŲŌē┼żĘżŲż¬żĻĪó┼²╣ń▒R─Ļ▀_(d©ó)ż╚żŌżżż©żļż¼Īó╩¼▓“ē”ż¼╣Ōż»ź╬źżź║ż¼Č╦żßżŲ─ŃżżĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年8月22日

Ī├Č\Įč╩¼└ŽĪ╩╚ŠŲ│öü×æēäĪ╦

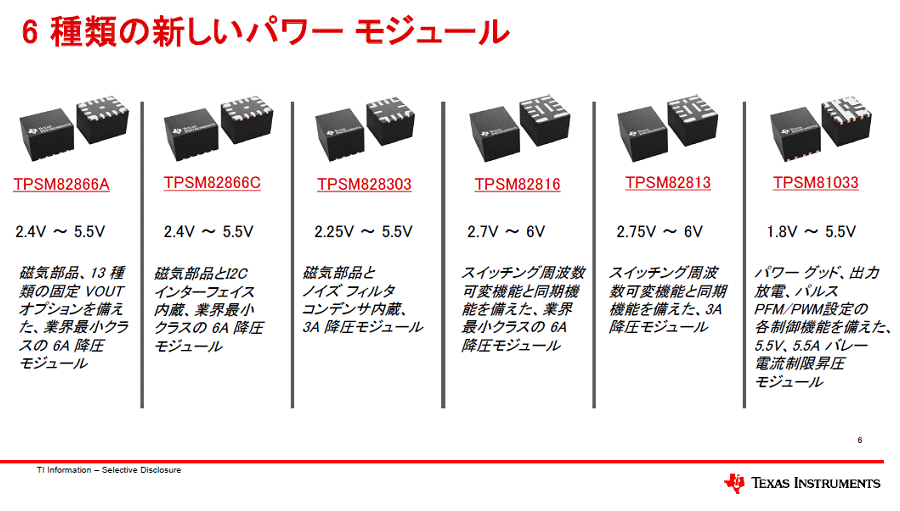

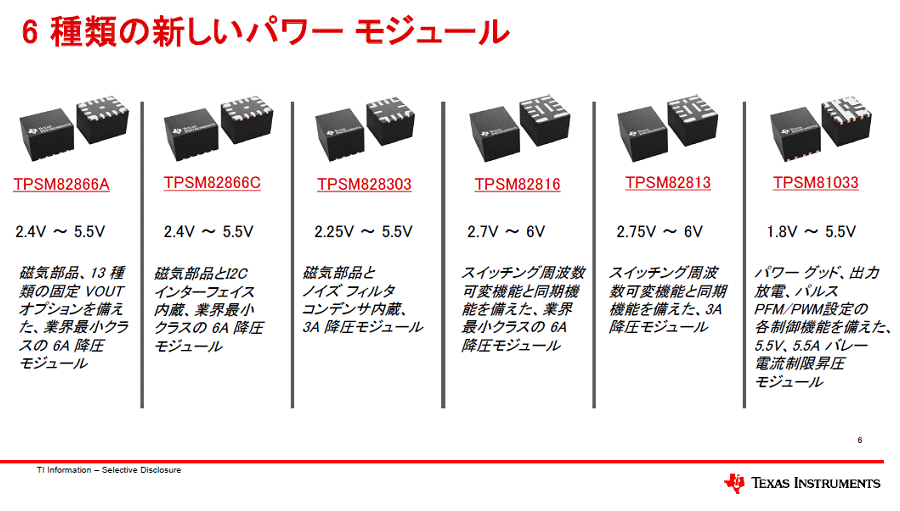

Texas InstrumentsżŽĪóPOLĪ╩Point of LoadĪ╦ż╚Ō}żążņżļ┼┼Ė╗├ōICż╚żĘżŲ╗╚ż”ĪóĮą╬ü6Aż╬Š«Ę┐┼┼Ė╗├ōźčź’Ī╝źŌźĖźÕĪ╝źļĪųMagPackĪūż“│½╚»Ī󟥟¾źūźļĮą▓┘ż“│½╗ŽżĘż┐ĪŻĮą╬ü6Aż╬DC-DCź│ź¾źąĪ╝ź┐żŪżĄż©ĪóĮj(lu©░)żŁżĄżŽ2.3mmĪ▀3mmĪ▀1.95mmĪ╩╣ŌżĄĪ╦ż╚ź▄Ī╝ź╔ż╦╝┬äóż╣żļĀC└čż¼Š«żĄżżĪŻż│ż╬ż┐żßź▄Ī╝ź╔ź╣ź┌Ī╝ź╣ż“Ń~Ė·ż╦╗╚ż”ż│ż╚ż¼żŪżŁżļĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年8月 7日

Ī├Č\Įč╩¼└ŽĪ╩×æļ]Ī”ĖĪØhäóÅøĪ╦

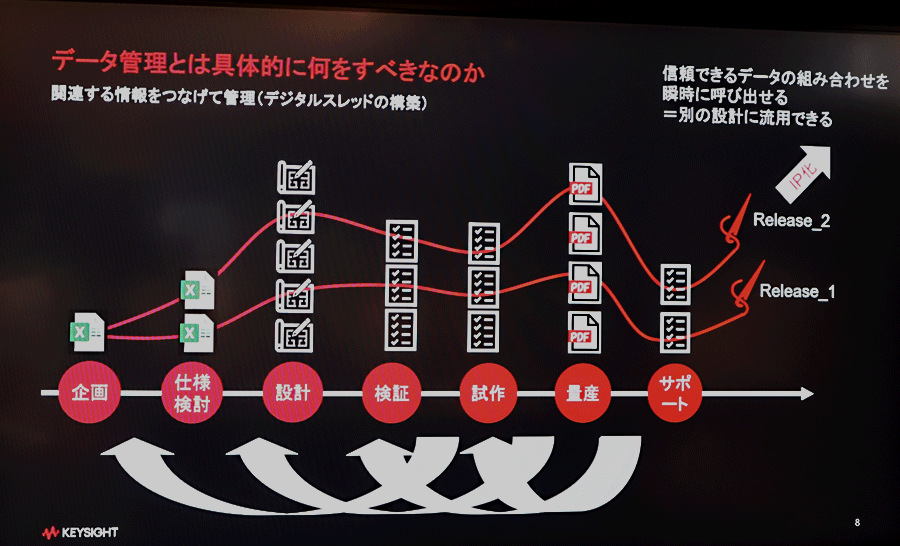

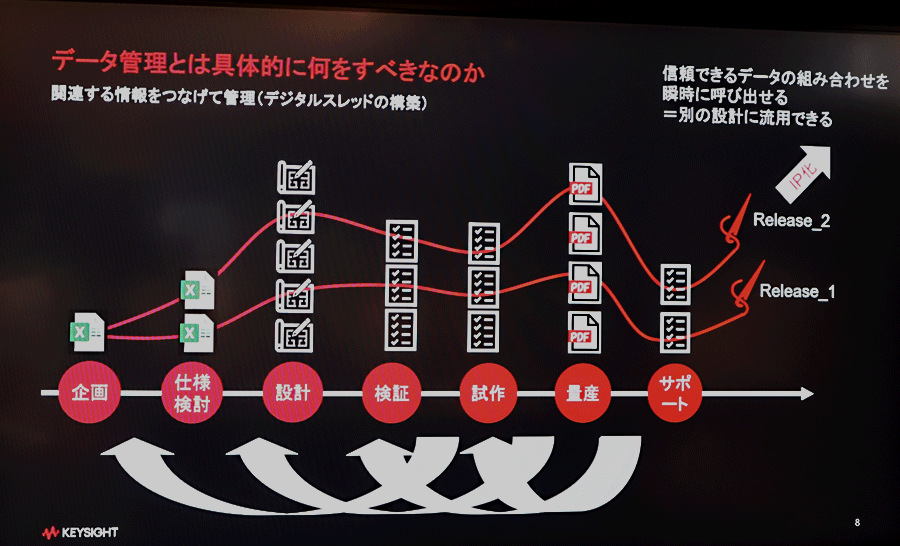

╚ŠŲ│öüż╬╣Ō╝■āSØŖ└ŁżõżĄż▐żČż▐ż╩źčźķźßĪ╝ź┐ØŖ└Łż“▒R─Ļż╣żļ╝Ŗ▒R▀_(d©ó)ż“└▀╝ŖĪ”×æļ]żĘżŲżżżļKeysight Technologyż¼Īó║ŻŃQżŪ10övų`ż╚ż╩żļźūźķźżź┘Ī╝ź╚·t┐ā▓±Keysight Worldż“┼ņ»BĪ”JPź┐ź’Ī╝ź█Ī╝źļ&ź½ź¾źšźĪźņź¾ź╣żŪ│½╠¢żĘż┐ĪŻż│ż│żŪVLSI └▀╝ŖźŪĪ╝ź┐ż╬źķźżźšźĄźżź»źļź▐ź═Ī╝źĖźßź¾ź╚żõź┴ź├źūźņź├ź╚ż╬└▀╝Ŗź─Ī╝źļĪó¼ś┼┼═Ų╬╠öĄ(sh©┤)╝░ż╦żĶżļź▄ź¾źŪźŻź¾ź░ź’źżźõĪ╝ż╬ØÖŪ╦ŽsĖĪØhż╩ż╔ż“Šę▓żĘżŲżżżļĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年7月26日

Ī├Č\Įč╩¼└ŽĪ╩╚ŠŲ│öü▒■├ōĪ╦

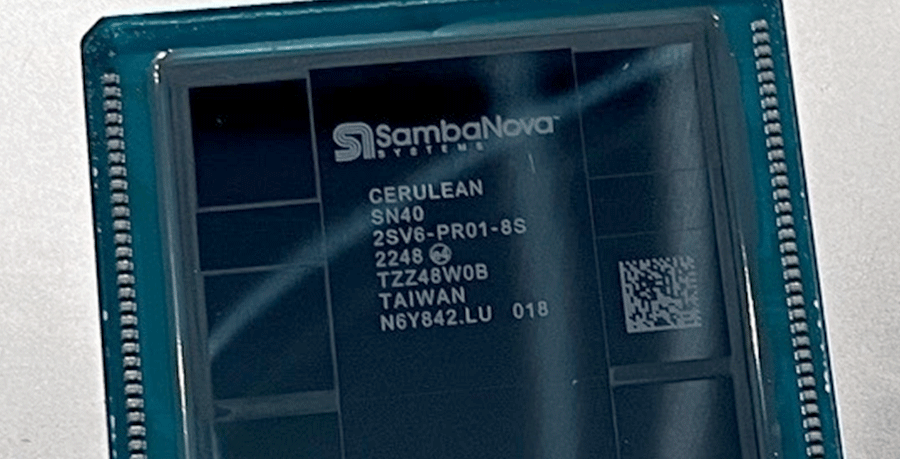

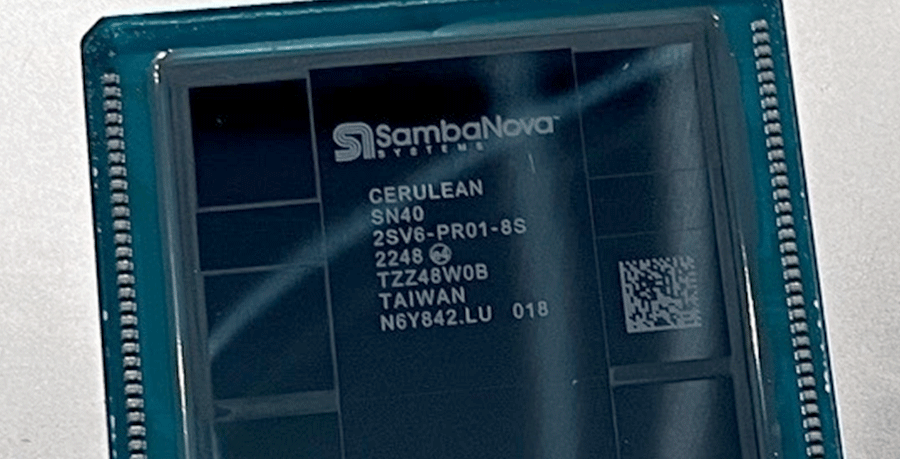

NvidiaŲ▒══ĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żõź¬ź¾źūźņź▀ź╣ż╩ż╔┤ļČ╚Ė■ż▒AIź┴ź├źūż╬├µżŪźŪĪ╝ź┐źšźĒĪ╝ź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż“└čČ╦┼¬ż╦ŠW(w©Żng)├ōż╣żļSambaNova╝ęż¼╝Ī└ż┬ÕAIż╚żżż”ż┘żŁĪó¾H┐¶ż╬└ņ├ōźŌźŪźļż“śOć·┼¬ż╦╝┬╣įżŪżŁżļź©Ī╝źĖź¦ź¾źŲźŻź├ź»AIż“ų`╗žżĘżŲżżżļż│ż╚ż¼ż’ż½ż├ż┐ĪŻ▐kż─ż╬AIź┴ź├źūżŪ¾H┐¶ż╬źŌźŪźļż“╝┬╣įżŪżŁżļĪŻŠ├õJ┼┼╬üżŽĮj(lu©░)╔²ż╦▓╝ż¼żļż│ż╚ż╦ż╩żļĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

![NvidiaĪóLSI┐Ę×æēä│½╚»ø]Į╠ż╦░ę╬üż“╚»Ä¦ż╣żļÖ┌└«AIĪųChipNeMoĪūż“Įo│½ NvidiaĪóLSI┐Ę×æēä│½╚»ø]Į╠ż╦░ę╬üż“╚»Ä¦ż╣żļÖ┌└«AIĪųChipNeMoĪūż“Įo│½](/assets_c/900px/240718-nvidiachipnemo.png)

2024年7月18日

Ī├Č\Įč╩¼└ŽĪ╩źŪźąźżź╣└▀╝Ŗ& FPDĪ╦

╚ŠŲ│öüŪõżĻæųż▓żŪŠå└«─╣żĘżŲżżżļNvidiażŽĪóÖ┌└«AIż“żŽżĖżßż╚ż╣żļAIź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╬GPUżõźĮźšź╚ź”ź©źóż“żĄż▐żČż▐ż╩▒■├ōż┤ż╚ż╦AIźĮźĻźÕĪ╝źĘźńź¾ż“─¾ČĪżĘżŲżżżļĪŻż│ż╬ż█ż╔LSI└▀╝Ŗ┤³┤ųż“ø]Į╠ż╣żļż┐żßĪóź┴ź├źū└▀╝Ŗż╬ż┐żßż╬Ö┌└«AIżŪżóżļLLMĪ╩Įj(lu©░)æä╠ŽĖ└ĖņźŌźŪźļĪ╦źóźĘź╣ź┐ź¾ź╚ChipNeMoĪ╩┐▐1Ī╦ż“│½╚»ĪóIC×æēä│½╚»ż╦╗╚ż├żŲżżżļż│ż╚ż“ĪųNTTPC GPU Day Ö┌└«AI┤╚ūż╬║ŪØi└■Īūż╬╣ų▒ķżŪĪó£½żķż½ż╦żĘż┐ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年7月 2日

Ī├Č\Įč╩¼└ŽĪ╩źūźĒź╗ź╣Ī╦

AIź│ź¾źįźÕĪ╝źŲźŻź¾ź░źčź’Ī╝ż¼ż▒ż¾░·żĘĪóźūźĒź╗ź╣ź╬Ī╝ź╔ż╬╚∙║┘▓ĮżŽ┴ßż▐ż├żŲżżżļĪóż╚TSMCźĘź╦źóźąźżź╣źūźņźĖźŪź¾ź╚Ę¾╔¹Č”Ų▒║Ū╣ŌČ╚ē»╝╣╣į└šŪżŪvż╬Kevin ZhangĢ■ż¼Įęż┘ż┐ĪŻż│żņżŽ6ĘŅ28Ų³ż╦▓Ż┘pżŪTSMC Technology Symposium Japanż“│½╠¢żĘż┐║▌ĪóźßźŪźŻźóĖ■ż▒Č\Įč└Ō£½▓±żŪĮęż┘ż┐żŌż╬ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

2024年6月19日

Ī├Č\Įč╩¼└ŽĪ╩╚ŠŲ│öü×æēäĪ╦

GaNżõSiCż╬żĶż”ż╩╣ŌÅ]ż╬źčź’Ī╝╚ŠŲ│öüżŽ└Łē”ż╬═ź░╠└ŁżŽ£½│╬ż╦żóżļżŌż╬ż╬Īóź╬źżź║żõź¬Ī╝źąĪ╝źĘźÕĪ╝ź╚Īóźóź¾ź└Ī╝źĘźÕĪ╝ź╚ĪóźĻź¾ź«ź¾ź░ż╩ż╔źūźĻź¾ź╚┤łæųżŪ╗╚żżż╦ż»żĄż¼╗─żļĪŻź╬źżź║ż“═▐ż©żļź╔źķźżźąICż¼ź½ź«ż“É█żļż│ż╚ż“ż╣żŪż╦┼┴ż©ż┐ż¼Ī╩╗▓╣═½@╬┴1Ī╦Īóź╔źķźżźąICż╚GaNźčź’Ī╝ź╚źķź¾źĖź╣ź┐ż“ĮĖ└čżĘż┐źŌźĖźÕĪ╝źļĪ╩┐▐1Ī╦ż“Texas Instrumentsż¼│½╚»żĘż┐ĪŻ

[ó¬¶öżŁż“Ų╔żÓ]

![NvidiaĪóLSI┐Ę×æēä│½╚»ø]Į╠ż╦░ę╬üż“╚»Ä¦ż╣żļÖ┌└«AIĪųChipNeMoĪūż“Įo│½ NvidiaĪóLSI┐Ę×æēä│½╚»ø]Į╠ż╦░ę╬üż“╚»Ä¦ż╣żļÖ┌└«AIĪųChipNeMoĪūż“Įo│½](/assets_c/900px/240718-nvidiachipnemo.png)