źžźŲźĒĮĖ└čż╬└Ķ├╝źčź├ź▒Ī╝źĖČ\Į迎ź╗ź▀ź│ź¾źĖźŃźčź¾ż╬ų`Č╠ż└ż├ż┐

ź╗ź▀ź│ź¾źĖźŃźčź¾2022żŪżŽĪó╚ŠŲ│öüźčź├ź▒Ī╝źĖź¾ź░ż╬źųĪ╝ź╣ż¼µ£öüż╬╚Š╩¼ŖZż»ż“žéżßĪóźūźĒź╗ź╣ż╬Øi╣®µćż└ż▒żŪżŽż╩ż»ĪóĖÕ╣®µćż╚ż╬┤ųż╦żóżļØŖż╦└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Č\Įčż╦ÅRų`ż¼ĮĖż▐ż├ż┐ĪŻ12ĘŅ15Ų³ż╦│½╠¢(h©żo)żĄżņż┐APCSĪ╩Advanced Packaging and Chiplet SummitĪ╦2022żŪżŽĪóIntelĪóTSMCĪóAMDż╩ż╔ż╬└Ķ├╝źčź├ź▒Ī╝źĖżžż╬ŲDżĻ┴╚ż▀ż¼ų`ż“░·żżż┐ĪŻ

┐▐1ĪĪ6Ū▄ż╬╣ŌĮĖ└čSoCż“║Ņżņżļ└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Č\Įč

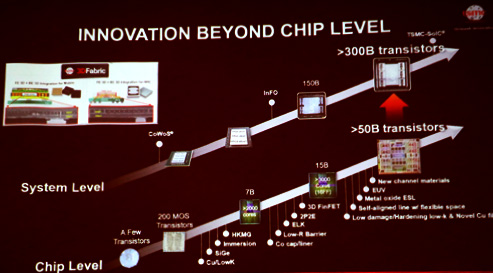

ź┴ź├źūźņź├ź╚ż“żŽżĖżßż╚ż╣żļ└Ķ├╝źčź├ź▒Ī╝źĖČ\Įčż╦└ż─cż╬ź╚ź├źūźūźņźżźõĪ╝ż┐ż┴ż¼ŲDżĻ┴╚żÓ║ŪĮj(lu©░)ż╬═²Įy(t©»ng)ż¼źŌź╬źĻźĘź├ź»żŪ║ŅżļżĶżĻżŌĪóżŌżŽżõ─Ńź│ź╣ź╚żŪ╣ŌĮĖ└čż╬SoC×æēäż¼║ŅżņżļżĶż”ż╦ż╩żļ▓─ē”└Łż╦żóżļĪŻTSMCż¼9ĘŅż╦│½żżż┐ĄŁŪvĖ■ż▒ż╬└Ō£½▓±żŪżŽĪóźŌź╬źĻźĘź├ź»ż└ż╚500▓»ź╚źķź¾źĖź╣ź┐ż“ĮĖ└čżŪżŁżļ╗■┤³ż╦Īó└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Č\Įčż└ż╚żĮż╬6Ū▄ż╬3000▓»ź╚źķź¾źĖź╣ź┐ż╬SoC×æēäż“║Ņżņżļż╚żĘżŲżżż┐Ī╩┐▐1Ī╦ĪŻ║Żövż╬ź╗ź▀ź│ź¾źĖźŃźčź¾ż╬APCS 2022ż╦┼ąŠņżĘż┐TSMCż╬ēää®Ī”┐«═Ļ└Łż¬żĶżė└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Č\Įčż╚źĄĪ╝źėź╣├┤┼÷ż╬VPżŪżóżļJohn HeĢ■(hu©¼)żŽĪó┐▐1ż╚Ų▒══ż╩┐▐ż“├ōżżĪó1000▓»ź╚źķź¾źĖź╣ź┐ż╬╗■┬Õż╦żŽ1├¹ź╚źķź¾źĖź╣ź┐ż“ĮĖ└čżŪżŁżļĪóż╚10Ū▄ż╬╣ŌĮĖ└čSoCż¼żŪżŁżļż╚└Ō£½żĘż┐ĪŻ└Ķ├╝źčź├ź▒Ī╝źĖČ\ĮčżŪżŽĪóźŌź╬źĻźĘź├ź»ż╩ź┴ź├źūż╚żŽ░Ńżżźņź┴ź»źļźĄźżź║ż╦żĶżļĀC└čż╬öU(ku©░)Ė┬ż“£pż▒ż╩żżĪŻż│ż╬ż┐żß╣ŌĮĖ└č▓Įż¼▓─ē”ż╚ż╩żļĪŻ

└Ķ├╝źčź├ź▒Ī╝źĖżŽźżź¾ź┐Ī╝ź▌Ī╝źČź┘Ī╝ź╣ż╬Č\ĮčżŪżóżĻĪóź┴ź├źūźņź├ź╚ż╬└▄¶öż╦żŽ╠õ¼öż¼¾Hż»Īóż▐ż┐╩Ż╗©ż╩źņź┤ź▓Ī╝źÓżŪżŌżóżļĪóż╚HeĢ■(hu©¼)żŽĖņż├żŲżżżļĪŻ┤łż¼Įj(lu©░)żŁżżż█ż╔│õżņżõż╣ż»ż╩żĻĪóŲ³╦▄ż╬║Ó╬┴źßĪ╝ź½Ī╝ż╚ż╬ź│źķź▄ż¼’L(f©źng)ż½ż╗ż╩żżĪŻź│źķź▄ż╦żĶż├żŲ─Ńżż╩Ōé╬ż▐żĻż“╣Ōżßżļż│ż╚ż¼żŪżŁżļż╚Ė└ż”ĪŻ║ŪĮj(lu©░)ż╬å▄ż▀żŽĪóż╔ż”żõż├żŲÖ┌ŠÅ└Łż“æųż▓Īó╩Ōé╬ż▐żĻż“Ė■æųżĄż╗żļż½żŪżóżļĪŻźņź┤ź▓Ī╝źÓż╚Ų▒══Īó└▄¶öŗ╩¼ż“║YØŹ▓ĮżĘĪó└┌żĻ╩¼ż▒żõ║Ó╬┴ż¼ź╬ź”źŽź”ż╦ż╩żļż╚żĘżŲżżżļĪŻ

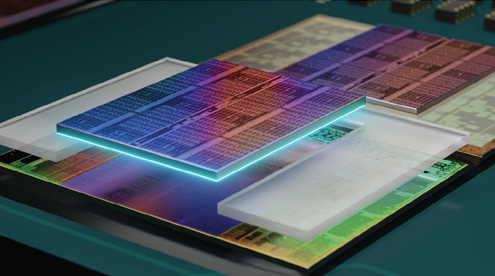

╣ŌĮĖ└č▓ĮżŪżŽØŁ─ś┼¬ż╦CPUżõGPUĪóDSPĪóźßźŌźĻż╩ż╔══Ī╣ż╩źūźĒź╗ź├źĄżõövŽ®ż“ĮĖ└čż╣żļźžźŲźĒż╩ĮĖ└čČ\Įčż╦ż╩żļĪ╩┐▐2Ī╦ĪŻIntel╝ęźšź¦źĒĪ╝ż╬Ravi MahajanĢ■(hu©¼)żŽĪóźžźŲźĒĮĖ└čż¼─_═ūż╦ż╩żĻĪóDTCOĪ╩Design Technology Co-OptimizationĪ╦ż½żķźĘź╣źŲźÓ┼¬ż╩╣═ż©ż╬STCOĪ╩System Technology Co-OptimizationĪ╦ż“┐╩żßĪ╩╗▓╣═½@╬┴1Ī╦Īóźčź├ź▒Ī╝źĖżõźĮźšź╚ź”ź©źóĪóź┴ź├źūż╬║Ū┼¼▓Įż¼─_═ūż╦ż╩żļĪŻżĮż╬ż┐żßż╦UCIeż╬żĶż”ż╩║YØŹæä│╩ż“┐╩żßżŲżżż»ż│ż╚ż╦ż╩żļż╚żżż”ĪŻ

┐▐2ĪĪAMDż╬╣ŌĮĖ└čSoCż╦żŽ3D-ICż¼╗╚ż’żņżŲżżżļĪĪĮąųZĪ¦AMD

UCIe 1.0żŪżŽĪó╬Ńż©żąźąź¾źūźįź├ź┴ż¼45µmż╚╚∙║┘ż╩æä│╩ż“UCIe-A8żõUCIe-A16Ī╩┐¶ÖC(j©®)żŽźčź├ź╔┐¶Ī╦ż╚żĘĪó║YØŹ┼¬ż╩źąź¾źūźįź├ź┴ż╬110µmż╬æä│╩ż“UCIe-S8żõUCIe-S16ż╩ż╔ż╚żĘżŲ┬Ęż©żŲżżż»ĪŻIntelż¼│½╚»żĘż┐Ponte Vecchio GPUźūźĒź╗ź├źĄż╦żŽ1000▓»ź╚źķź¾źĖź╣ź┐ż“ĮĖ└čżĘĪó47Ė─ż╬źóź»źŲźŻźųż╩ź┐źżźļĪ╩ź┴ź├źūźņź├ź╚Ī╦ż“╔▀żŁĄ═żßżŲż¬żĻĪóżĮżņżķż╬┤ųż╦└▄¶öż╦11Ė─ż╬EMIBźĘźĻź│ź¾źųźĻź├źĖż“╗╚ż├żŲżżżļż╚żżż”ĪŻ

IntelżŽźžźŲźĒĮĖ└čż╬└Ķ├╝źčź├ź▒Ī╝źĖżŪżŽĪóź└źż-ź└źż┤ųż╬Ū█└■ż“ر═²┴žżõźūźĒź╚ź│źļź╣ź┐ź├ź»ĪóźĮźšź╚ź”ź©źóźŌźŪźļż╩ż╔żŪ║YØŹ▓Įż╣żļż╚ĪóĘQ╝ęż╬ź┴ź├źūźņź├ź╚ż“ź▀ź├ź»ź╣&ź▐ź├ź┴żŪį~├▒ż╦└▄¶öżŪżŁżļżĶż”ż╦ż╩żļż╚Č”ż╦Īóźčź├ź▒Ī╝źĖŲŌŗż╦PCIeżõCXLż╩ż╔ż╬╣ŌÅ]źżź¾ź┐Ī╝źšź¦źżź╣ż“╗╚ż©żļżĶż”ż╦ż╩żĻĪó¤²▓├▓┴├═ż╬╣Ōżżź½ź╣ź┐źÓ×æēäż¼▓─ē”ż╦ż╩żļż╚żĘżŲżżżļĪŻ

źžźŲźĒĮĖ└čż╬└Ķ├╝źčź├ź▒Ī╝źĖČ\Įčż╦╬üż“Ų■żņżļżŌż”▐kż─ż╬═²Įy(t©»ng)ż¼ĪóźŌź╬źĻźĘź├ź»ż╩ź©źĻźóź╣ź▒Ī╝źĻź¾ź░Ī╩╗▓╣═½@╬┴2Ī╦ż¼28ŃQż┤żĒż╦żŽČÉŽ┬żĘżŲżĘż▐ż”ż½żķż└Īóż╚AMDż╬Technology Ī§Product Engineering├┤┼÷źĘź╦źóVPż╬Mark FuselierĢ■(hu©¼)żŽĮęż┘żŲżżżļĪŻż╩ż╝ČÉŽ┬ż╣żļż╬ż½ĪŻ3╝ĪĖĄżŪż╬ĀC└čź╣ź▒Ī╝źĻź¾ź░żŪżŽźßź┐źļż╬RCź╣ź▒Ī╝źĻź¾ź░żĘż┼żķż»ż╩żĻĄK▒Ųūxż“Ą┌ż▄ż╣żĶż”ż╦ż╩żļż½żķż└ż╚żĘżŲżżżļĪŻżĮż╬╗■żŽżŌżŽżõCuŪ█└■żŽ╗╚ż©ż║Īó╣Ō▓┴ż╩CoĪ§RuŪ█└■ż╦żĶż├żŲ°BŃ^ż“▓╝ż▓żļż╚żżż├ż┐╣®╔ūż¼ØŁ═ūż╦ż╩żļż╚żżż”ĪŻź┴ź├źūźņź├ź╚ż╬└Ķ├╝źčź├ź▒Ī╝źĖżŽź│ź╣ź╚┼¬ż╦żŌŃ~ŠW(w©Żng)ż└ż╚żĘżŲżżżļĪŻ

ż┐ż└żĘĪóź┴ź├źūźņź├ź╚ż╦żĶżļ└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░Č\ĮčżŪżŽ╠õ¼öżŽ¾HżżĪŻ▐kż─żŽÕXż╬╠õ¼öżŪżóżĻĪóżŌż”▐kż─żŽ┼┼Ė╗└▀╝Ŗż╬╠õ¼öż└ż╚AMDż╬FuselierĢ■(hu©¼)żŽÅBż╣ĪŻÕXż╦żĶżļ╠õ¼öż╚żĘżŲ║ŪŖZ╔ŌæųżĘżŲżżżļż╬ż¼╚Š┼─źąź¾źūż╦ż¬ż▒żļź©źņź»ź╚źĒź▐źżź░źņĪ╝źĘźńź¾ż└Ī╩╗▓╣═½@╬┴3Ī╦ĪŻFuselierĢ■(hu©¼)żŽĪóÕXż╬źżź¾ź┐Ī╝źšź¦źżź╣ż╬╠õ¼öż¼─_═ūż└ż╚╗ž╝~ż╣żļĪŻź┴ź├źūŲŌŗż╬ź©źņź»ź╚źĒź▐źżź░źņĪ╝źĘźńź¾ż╬╠õ¼öżŪżŽż╩żżĪŻż┐ż╚ż©ĪóKGDĪ╩Known Good DieĪ╦ż└ż╚żĘżŲżŌÕX└▀╝Ŗż╬ĄKżżź┴ź├źūżõź┴ź├źūźņź├ź╚ż“3╝ĪĖĄ└č┴žż╣żļżĶż”ż╦ż╩żļż╚Īóź█ź├ź╚ź╣ź▌ź├ź╚ż¼żóżņżąæų▓╝ż╬ź┴ź├źūż╦ĄK▒Ųūxż“Ą┌ż▄żĘ║Ų└▀╝Ŗż╚ż╩żļĪŻ

żĄżķż╦┼┼Ė╗ČĪĄļżŪżŽźčź’Ī╝ż“ż╔ż”ČĪĄļż╣żļż½Īóż╔ż”źņź«źÕźņĪ╝ź╚ż╣żļż½Īóż╚żżż”╠õ¼öżŌżóżļĪŻ└Ķ├╝źčź├ź▒Ī╝źĖżŪżŽśOĮy(t©»ng)┼┘ż¼Įj(lu©░)żŁżżż┐żßĪó┼┼Ė╗└▀╝Ŗż¼žMżĘżżĪŻż│ż╬└ĶĪó1ź┴ź├źūż╬źąź├ź»źĄźżź╔ż╦┼┼Ė╗ČĪĄļźķźżź¾ż“└▀ż▒żļż│ż╚ż¼─¾░ŲżĄżņżŲżżżļż¼Īóźņź«źÕźņĪ╝ź┐ż“ź¬ź¾ź┴ź├źūż╣żļØŁ═ūż¼żóżļż└żĒż”ż╚FuselierĢ■(hu©¼)żŽĖ└ż”ĪŻ

╗▓╣═½@╬┴

1. ĪųimecĪóĪžźÓĪ╝źóż╬╦Īō¦żŽż│żņż½żķżŌ┘Vż▐żķż╩żżĪ┘ĪóSTCOżŪA2└ż┬Õż▐żŪ¶öż»ĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2022/11/09)

2. ĪųTSMCĖ”ē|Ī┴▓±µ^Ė┬─ĻFreeWebinarĪ╩9/28Ī╦ĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2022/10/04)

3. Mutschler, A. S., "3D-IC Reliability Degrades with Increasing Temperature", Semiconductor Engineering (2022/12/14)