IntelĪóXeonźūźĒź╗ź├źĄż╬źóź»ź╗źķźņĪ╝ź┐FPGAż“¶öĪ╣źĻźĻĪ╝ź╣

IntelżŽĪó║ŪŖZFPGAżŪŲł└¬ż“ż½ż▒Īó┴Ļ╝ĪżżżŪź╦źÕĪ╝ź╣źĻźĻĪ╝ź╣ż“╚»╔ĮżĘżŲżżżļĪŻ8ĘŅ30Ų³ż╦żŽ10nmż╬Agilex FPGAĪ╩┐▐1Ī╦ż“Ė┬─ĻĖ▄Ąęż╦Įą▓┘ż“╗ŽżßĪó8ĘŅæųĮ▄ż╦żŽFPGA┼ļ║▄źóź»ź╗źķźņĪ╝ź┐ź½Ī╝ź╔Ī╩┐▐2Ī╦ż“źĻźĻĪ╝ź╣żĘż┐ĪŻČ”ż╦Īó▒ķōQż¼─_żż├ō²ŗżŪżŌCPUż╬╔ķ▓┘ż“Ę┌žō(f©┤)żĄż╗żļż┐żßż╦FPGAż“╗╚ż├ż┐źóź»ź╗źķźņĪ╝ź┐ż╚żĘżŲŲ»ż»ĪŻ

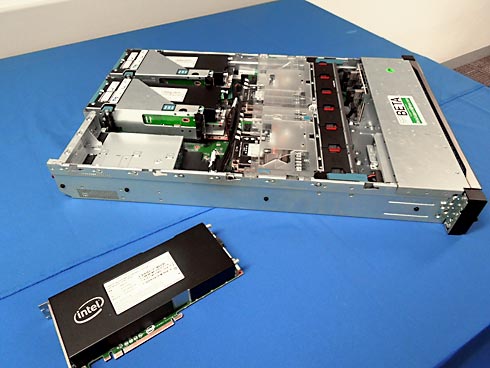

┐▐1ĪĪIntelĮķż╬10nmFPGAż“Įą▓┘ĪĪĮąųZĪ¦Intel Corp.

┐▐2ĪĪIntelż╬FPGA┼ļ║▄źóź»ź╗źķźņĪ╝ź┐ź½Ī╝ź╔(▓╝ż╬▌üżżźŌźĖźÕĪ╝źļŗ╩¼)

Intelż╬Agilex FPGAżŽ10nmźūźĒź╗ź╣żŪ║Ņ×æżĘż┐║Ū└Ķ├╝ż╬FPGAżŪĪóCPUż╬XeonźūźĒź╗ź├źĄż“▌öż”źóź»ź╗źķźņĪ╝ź┐ż╚żĘżŲ╗╚ż’żņżļĪŻż╣żŪż╦MicrosoftżõColorado EngineeringĪóMantaro NetworksĪóSilicomż╩ż╔ż╦Įą▓┘żĘ╗ŽżßżŲżżżļĪŻż│ż╬Intel AgilexźšźĪź▀źĻFPGAżŽĪóIntelż╬╝┬äóČ\ĮčEMIBĪ╩embedded multi-die interconnect bridgeĪ╦ż╬æųż╦3D SiPĪ╩silicon in packageĪ╦żŪ╣Į└«żĄżņżŲżżżļĪŻż│ż╬źžźŲźĒź┴ź├źūż“1źčź├ź▒Ī╝źĖż╦ĮĖ└čż╣żļSiPČ\Į迎źóź╩źĒź░ICżõźßźŌźĻĪóź½ź╣ź┐źÓź│ź¾źįźÕĪ╝źŲźżź¾ź░Īóź½ź╣ź┐źÓI/OĪóIntelż¼āA╝²żĘż┐eASICż“ĮĖ└čżŪżŁżļĪŻżĘż½żŌFPGAżŪ╣Į└«żĄżņż┐źŪźĖź┐źļövŽ®ż“eASICż╬ź╣ź╚źķź»ź┴źŃĪ╝ź╔ASICż╦ź╣źÓĪ╝ź║ż╦öĪ╣į▓─ē”ż╩żĶż”ż╩ØŹ×óż“┐╩żßżŲżżżļĪŻ

ż│ż╬ź┴ź├źūż╬└Łē”żŽĪóż│żņż▐żŪ║Ū╣Ōż╬Stratix 10 FPGAż╚╚µż┘żŲ40%└Łē”ż¼╣ŌżżĪŻżóżļżżżŽŲ▒żĖ└Łē”ż╩żķ40%Š├õJ┼┼╬üż¼─ŃżżĪŻ║ŪĮj(lu©░)ż╬└Ķ┐╩└ŁżŽĪó║ŻĖÕ╚»╔ĮżĄżņżļCXLĪ╩Compute Express LinkĪ╦ż“źĄź▌Ī╝ź╚żĘżŲżżżļ┼└ż└ĪŻCXLźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“╗╚ż©żąĪ󟣟џ├źĘźÕż╚źßźŌźĻź│źęĪ╝źņź¾źĘż“Ęeż┴ż╩ż¼żķ╝Ī└ż┬Õż╬XeonźūźĒź╗ź├źĄż╚└▄¶öżŪżŁżļżĶż”ż╦ż╩żļĪŻ

ĖĮėXż╬Stratix 10żŽĪóźĄĪ╝źąĪ╝ż╬źóź»ź╗źķźņĪ╝ź┐ź½Ī╝ź╔PAC D5005ż“ź│ź¾źįźÕĪ╝ź┐źßĪ╝ź½Ī╝HPEĪ╩Hewlett Packard EnterpriseĪ╦ż╬źĄĪ╝źąĪ╝ĪųPE Proliant DL 380 Gen 10ĪūźĄĪ╝źąĪ╝ż╦┼ļ║▄żĄżņĪóĮą▓┘żĄżņż┐ĪŻźĄĪ╝źąĪ╝ŲŌż╬ź╣źĒź├ź╚ż╦║╣ż╣ż└ż▒żŪ╗╚ż©żļż’ż▒ż└ż¼ĪóFPGAż“ź½ź╣ź┐ź▐źżź║ż╣żļż┐żßż╬│½╚»┤─ČŁżŪżóżļźóź»ź╗źķźņĪ╝źĘźńź¾Ī”ź╣ź┐ź├ź»żŌ─¾ČĪż╣żļĪŻż│ż╬│½╚»┤─ČŁżŪżŽXeonźūźĒź╗ź├źĄż╚FPGAż╬╬ŠöĄ(sh©┤)ż“źūźĒź░źķź▀ź¾ź░żŪżŁżļĪŻ

ż│żņż▐żŪż╬Intelż╬FPGA Arria 10 PACżŪżŽ└Łē”żõ┼┼╬üĖ·╬©ż¼’BżĻż╩żżĪóźĻźóźļź┐źżźÓżŪ╝┬╣įżŪżŁżļźėźŪź¬ź╚źķź¾ź╣ź│Ī╝ź│Ī╝źŪź├ź»żõAIĪ╩źŪźŻĪ╝źūź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»Ī╦ż“╗╚ż├ż┐▓╗╠mż╬źŲźŁź╣ź╚▓Įż╩ż╔ż╦Ė■ż»ĪŻ▓╗╠mż╬źŲźŁź╣ź╚▓ĮżŪżŽźŪĪ╝ź┐ż“▐k┼┘ż╦ż╔ż├ż╚┴„żĻ╣■żÓŲ░║Ņż¼żóżļż┐żßGPUżĶżĻżŌ└Łē”ż¼╣Ōżżż╚żĘżŲżżżļĪŻ╬Ńż©żąGPUż└ż╚16źėź├ź╚ż╬╔ŌŲ░Š«┐¶┼└▒ķōQżĘż½żŪżŁż╩żżż╚ż│żĒż“ĪóFPGAż“╗╚ż©żą8źėź├ź╚ż╬┼D┐¶▒ķōQżõĪó╠ĄŠGż╩ź╝źĒ▒ķōQż“žō(f©┤)żķż╣ź╣źčĪ╝ź╣└Łż“╣Ōżßżļż╩ż╔ĪóźŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░ż╦┼¼żĘż┐övŽ®ż╬║Ū┼¼▓Įż¼żŪżŁżļĪŻ