XilinxĪó5G┤├ŽČ╔Ī”ź╣źŌĪ╝źļź╗źļĖ■ż▒ż╦Zynq UltraScależ╬RF╚Ūż“├ō┴T

XilinxżŽ5Gż╬┤├ŽČ╔ż╦Ė■ż▒ż┐SoCż╬Zynq UltraScależ╦RF├ōźŪźĖź┐źļź┘Ī╝ź╣źąź¾ź╔övŽ®ż“ĮĖ└čżĘż┐┐ʿʿżSoCźŪźąźżź╣(┐▐1)ż╬źĒĪ╝ź╔ź▐ź├źūż“╚»╔ĮżĘż┐ĪŻŲ³╦▄żŪżŌ3.7GHz┬ėż╚4.5GHz┬ėĪ󿬿Ķżė28GHz┬ėż¼┴Ēē»Š╩ż╬╝■āS┐¶│õżĻ┼÷żŲż╚żĘżŲ»éż▐ż├ż┐ĪŻXilinxż╬ż│ż╬ź┴ź├źūżŽĪ󟥟ų6GHzż“ź½źąĪ╝żĘĪóźŪźĖź┐źļ╩č╔³─┤ĖÕż╬źŪźĖź┐źļövŽ®żŌ┼ļ║▄żĘżŲż¬żĻĪóźŌźąźżźļ├╝¼Źż╦ŖZżżź©ź├źĖ┤├ŽČ╔Ė■ż▒ż╚ż╩żļĪŻ

┐▐1ĪĪźĮźšź╚ź”ź©źóźūźĒź░źķź▐źųźļż╬CPUż╚źŽĪ╝ź╔ź”ź©źóźūźĒź░źķź▐źųźļż╬FPGAż“īÖ├ōżĘż┐╠Ą└■ż╬źūźķź├ź╚źšź®Ī╝źÓź┴ź├źūĪĪĮąųZĪ¦Xilinx

Xilinxż╬Zynq UltraScależŽĪóFPGAövŽ®ż“×óż©ż┐SoCź┴ź├źūżŪżóżĻĪó5GżŪ╦▄│╩┼¬ż╦╗╚ż’żņżļżĶż”ż╦ż╩żĒż”MIMOĪ╩Multiple Input Multiple OutputĪ╦źóź¾źŲź╩ż╚źėĪ╝źÓźšź®Ī╝ź▀ź¾ź░ĮĶ═²ż╦░ę╬üż“╚»Ä¦ż╣żļĪŻź©ź├źĖż╦ŖZżż┤├ŽČ╔żõź╣źŌĪ╝źļź╗źļż╦ĮjżŁż╩▌xŠņż¼żóżļż█ż½ĪóCATVżõź▒Ī╝źųźļźŌźŪźÓż╩ż╔ż╬źĻźŌĪ╝ź╚PHYź╬Ī╝ź╔ĪóżóżļżżżŽÆņȧĄĪż“╝{└ūż╣żļźšź¦Ī╝ź║ź╔źóźņźżźņĪ╝ź└Ī╝żõĄżō■─┤Øhż╩ż╔ż╬├ō²ŗżŌżóżļż╚żżż”ĪŻ

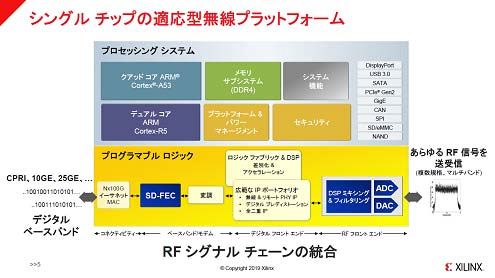

RF-SoCż╬RFż½żķź┘Ī╝ź╣źąź¾ź╔ĮĶ═²ż╦ż½ż▒żŲ┤╦▄┼¬ż╩╣═ż©öĄżŽĪóżŪżŁżļż└ż▒źŪźĖź┐źļĮĶ═²żŪ┐╩żßżŲżżż»ż│ż╚ż└(┐▐1)ĪŻRF┐«ęÄż“£p┐«żĘż┐ĖÕĪóż╣ż░ż╦A-D╩č┤╣żĘżŲźŪźĖź┐źļ▓ĮżĘĪóDSPż╬└čŽ┬▒ķōQż╦żĶż├żŲź▀źŁźĘź¾ź░Ī󿥿ķż╦źŪźĖź┐źļźšźŻźļź┐źĻź¾ź░ż“╣įżżĪóź┘Ī╝ź╣źąź¾ź╔┐«ęÄż“įużļĪŻżĮż╬ĖÕżŽźŪźĖź┐źļżŪż╬║╣╩╠▓Įżõźóź»ź╗źķźņĪ╝źĘźńź¾ż╩ż╔ż╬źŪźĖź┐źļ▒ķōQż“╣įż”ĪŻ┴„┐«ż╬Šņ╣ńżŽż│ż╬Ąšż└ż¼Īó10Gźėź├ź╚Ethernetżõ25GEż╩ż╔ż╬╣ŌÅ]źŪźĖź┐źļ┐«ęÄż“┴„┐«ż╣żļŠņ╣ńż╦żŽĪóźĮźšź╚ź”ź©źó─Ļ▒Iż╦żĶżļØiöĄĖĒżĻÖÄ┘ćČ\ĮčSD-FECövŽ®ż“ĘążŲĖĒżĻÖÄ┘ćżĘż┐ż╬ż┴ĪóźŪźĖź┐źļ╩č─┤ż“ż½ż▒ĪóżĮżĘżŲ╠Ą└■IPżõźĻźŌĪ╝ź╚PHY IPż╩ż╔żõĪóźūźņźŪźŻź╣ź╚Ī╝źĘźńź¾övŽ®żŪ┴„┐«┐«ęÄż“═Įżß┘ćżĘżżĘ┴żŪ£pż▒żķżņżļżĶż”ż╦┐«ęÄż“▌ö┘ćżĘżŲż¬ż»ĪŻ┴„┐«ż╬ż┐żßż╬ź▀źŁźĘź¾ź░żõźšźŻźļź┐źĻź¾ź░ż“╣įżżĪóD-A╩č┤╣żĘżŲźčź’Ī╝źóź¾źūż½żķ┴„żĻĮąż╣ĪŻ

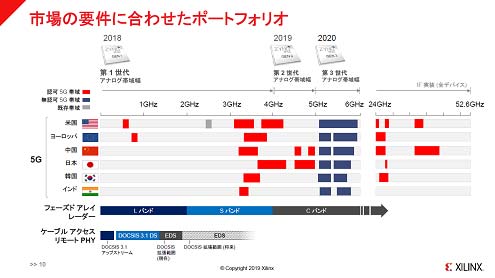

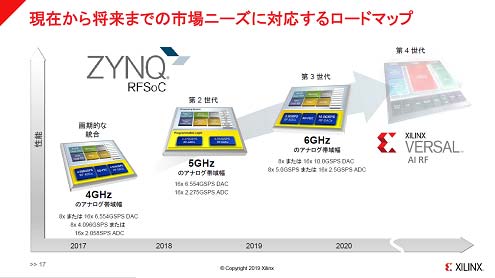

║“ŃQ╚»╔ĮżĘż┐ŗī1└ż┬Õż╬Zynq UltraScale RF-SoCżŽĪó║ŪĮj╝■āS┐¶┬ė4GHzżŪżóż├ż┐ĪŻ┴Ēē»Š╩ż╬╝■āS┐¶│õżĻ┼÷żŲż╬3.7GHz┬ėĪ╩3.6Ī┴4.2GHzĪ╦ż╦żŽŠ»żĘ╔į╦■ż¼╗─ż├ż┐ĪŻżĮż│żŪ║ŻövĪó║ŪĮj╝■āS┐¶ż¼5GHzż╬ŗī2└ż┬ÕZU RF-SoCż“źĄź¾źūźļĮą▓┘żĘż┐(┐▐2)ĪŻż│żņżŽ2019ŃQ6ĘŅż╦×æēä▓Įż“═Į─ĻżĘżŲżżżļĪŻż│ż╬ź┴ź├źūż╩żķĪó3.7GHz┬ėż└ż▒żŪżŽż╩ż»Īó4.5GHz┬ėĪ╩4.4Ī┴4.9GHzĪ╦ż╦żŌ×┤▒■żŪżŁżļĪŻØŹź▀źĻāSż╬28GHz┬ėĪ╩27Ī┴29.5GHzĪ╦ż╦┤žżĘżŲżŽĪó╝■āS┐¶ź└ź”ź¾ź│ź¾źąĪ╝ź┐żŪ28GHz┬ėż½żķ3.7GHzżóżļżżżŽ4.5GHzż╦═Ņż╚żĘżŲż½żķź┘Ī╝ź╣źąź¾ź╔ĮĶ═²ż“╣įż”ż┐żßĪóŗī2└ż┬Õż▐żŪż╬ź┴ź├źūżŪżóżņżąĪóŲ³╦▄ż╬╝■āS┐¶żŽź½źąĪ╝żŪżŁżļĪŻż┐ż└żĘĪó5~6GHzż╬╠╚ß×╔į═ūż╬╝■āS┐¶┬ėżŌ└ż─cĘQ├ŽżŪ╣═╬Ėż╦Ų■żņżķżņżŲżżżļż┐żßĪóŗī3└ż┬Õż╬ZU RF-SoCżŪ║ŪĮj╝■āS┐¶6GHzż╬ź┴ź├źūżŌ2020ŃQż╦═Į─ĻżĄżņżŲżżżļĪŻ

┐▐2ĪĪĘQ╣±ż╬5G╝■āS┐¶┬ėĪĪĮąųZĪ¦Xilinx

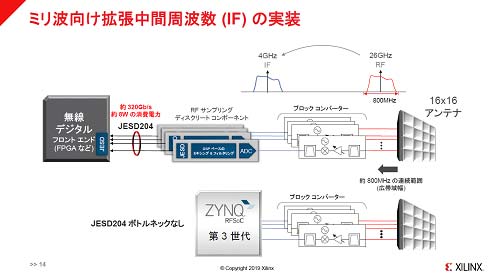

ŗī2└ż┬ÕĪóŗī3└ż┬Õēäż╚żŌ16Ī▀16żóżļżżżŽ8Ī▀8ż╬MIMOźóź¾źŲź╩ż“┴„£p┐«żŪżŁżļżĶż”ż╦ż╣żļż┐żßĪóA-D/D-Aż╬źŪĪ╝ź┐ź│ź¾źąĪ╝ź┐ż“8Ė─żóżļżżżŽ16Ė─ĮĖ└čżĘżŲżżżļĪŻż▐ż┐ĪóźŪĪ╝ź┐źņĪ╝ź╚ż“żŌż├ż╚æųż▓żļż┐żßż╦╩Ż┐¶ż╬źąź¾ź╔ż“╠Jż═żŲ╣ń└«ż╣żļźŁźŃźĻźóźóź░źĻź▓Ī╝źĘźńź¾Č\Įčż¼╗╚ż’żņżļż¼Īóż│żņż╦×┤żĘżŲżŌŲ¾ż─ż╬źŁźŃźĻźó╝■āS┐¶ż“ĮĶ═²żŪżŁżļżĶż”ż╦ż╣żļż┐żßĪóź▀źŁźĘź¾ź░ż╚źšźŻźļź┐źĻź¾ź░övŽ®ż“źšźņźŁźĘźųźļż╦╣Į└«żŪżŁżļĪŻ

ż▐ż┐Īóź▀źĻāSżŪżŽ╝■āS┐¶ż“╩č┤╣ż╣żļź└ź”ź¾ź│ź¾źąĪ╝ź┐ż“─╠żļĪŻA-Dź│ź¾źąĪ╝ź┐ż½żķźŪźĖź┐źļż╦╩č┤╣żĘż┐ĖÕĪó╩č─┤żĄżņż┐źŪźĖź┐źļ┐«ęÄż½żķź┘Ī╝ź╣ź┘ź¾ź╔┐«ęÄż▐żŪż│żņż▐żŪżŽJESD204źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“─╠żĘżŲ└▄¶öżĘżŲżżż┐ż¼Īó│░¤²ż▒ż└ż├ż┐ż┐żßĪó320Gźėź├ź╚/╔├ż╬╩┬š`┐«ęÄĮĶ═²ż└ż▒żŪ8WżŌż╬┼┼╬üż“Š├õJżĘżŲżżż┐Ī╩┐▐3Ī╦ĪŻżĘż½żĘŗī3└ż┬Õż╬ź┴ź├źūż└ż╚Īóż│ż│żŌ1ź┴ź├źūżŪ╝┬ĖĮżŪżŁżļż┐żßĪóŠ├õJ┼┼╬üżŽżĄż█ż╔╗\ż©ż╩żżĪŻ

┐▐3ĪĪź▀źĻāSżŪżŌ╝■āS┐¶ż“ź└ź”ź¾ź│ź¾źąĪ╝ź┐żĘż┐ĖÕżŽZU RF-SoCż“żĮż╬ż▐ż▐╗╚ż©żļĪĪĮąųZĪ¦Xilinx

ź▀źĻāS├ōżŪżŽĪóź▐ź├źĘźųMIMOżŽ╔į▓─’Lż╦ż╩żļż┐żßĪóŗēä┼└┐¶żŽż╔ż”żĘżŲżŌ╗\ż©żŲżĘż▐żżż¼ż┴ż└ĪŻź▄Ī╝ź╔żõźĘź╣źŲźÓż╬Š«Ę┐▓Įż╬ż┐żßż╦╣ŌĮĖ└č▓ĮżŽØŁ┐▄ż╦ż╩żļĪŻXilinxż╬ZU RF-SoCż╦żŽµ£żŲ│╚─ź└Łż¼żóżĻĪóæų░╠Ė▀┤╣└ŁżŌżóżļż┐żßĪóø]┤³┤ųżŪź╣źÓĪ╝ź║ż╦æų░╠ĄĪ¹|ż“▌xŠņż╦Įąż╣ż│ż╚ż¼żŪżŁżļĪŻżĄżķż╦ŗī4└ż┬Õż╬ź┴ź├źūż╚ż╩żļż╚ĪóRFżŌAIövŽ®żŌĮĖ└čż╣żļ7nmźūźĒź╗ź╣ż╬VERSALĪ╩╗▓╣═½@╬┴1Ī╦ż╦ż╩żļ(┐▐4)ĪŻ

┐▐4ĪĪĮø═Ķż╦×óż©ż┐źĒĪ╝ź╔ź▐ź├źūĪĪĮąųZĪ¦Xilinx

╗▓╣═½@╬┴

1. XilinxĪó«Ć╣ŌĄķ2.5D-LSIż╬µ£╦Ųż“£½żķż½ż╦ (2018/10/12)