AMDĪó┤░µ£ż╩źßźŌźĻź│źęĪ╝źņź¾źĘż╬║ŪĮķż╬HSAźóĪ╝źŁźŲź»ź┴źŃ×æēäż“╚»Ūõ

AMDżŽĪóźčźĮź│ź¾ż½żķ┴╚ż▀╣■ż▀źĘź╣źŲźÓżžż╬▒■├ōż╦╬üż“Ų■żņżŲż¬żĻĪó╣Ō└Łē”ż╩RźĘźĻĪ╝ź║┐Ę×æēäż╬APUĪųBald EagleĪū(┐▐1)ĪóGPUż╬ĪųAdelaarĪūż“Īóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļżŪ║“Į®╩¾╠OżĘż┐żĶż”ż╦(╗▓╣═½@╬┴1)Īó═Į─Ļ─╠żĻźĄź¾źūźļĮą▓┘ż╣żļĪŻ

┐▐1ĪĪAMDż╬┐ĘĘ┐APUĪųBald EagleĪūĪĪ╝å▀ģ╣┼▓▀ż╚ż█ż▄Ų▒żĖĮjżŁżĄ

ż│ż│żŪĪóAPUżŽźóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄĪóGPUżŽź░źķźšźŻź├ź»ź╣źūźĒź╗ź├źĄż╬ŠSżŪżóżļĪŻBald Eagleż╬┴└ż”├ō²ŗżŽĪóźóź▀źÕĪ╝ź║źßź¾ź╚Ī╩źčź┴ź¾ź│żõźčź┴ź╣źĒĪ╦Īó░Õ┬äĄĪ▀_ż╬▓ĶćĄĮĶ═²ĪóźŪźĖź┐źļźĄźżź═Ī╝źĖĪó╣®Č╚öUĖµżõśOŲ░▓Įż╩ż╔Īó╣Ō└Łē”ż╩ź░źķźšźŻź├ź»ź╣ĄĪē”ż“═ūĄßżĄżņżļ╩¼╠ŅżŪżóżļĪŻ

└Łē”żŽĪóż│żņżĶżĻ╚∙║┘ż╩×æēäżĶżĻżŌ╣ŌżżĪŻAMD Embedded Solutionsŗ╠ńProduct Management & MarketingŗźŪźŻźņź»ź┐żŪżóżļKamal KhouriĢ■(┐▐2)żŽĪų3Dź░źķźšźŻź├ź»ź╣└Łē”żŽĒö╣ńż╣żļIntelż╬źūźĒź╗ź├źĄHaswellżĶżĻżŌ║ŪĮj44%żŌ╣Ōż»ĪóØi└ż┬Õż╬×æēäż╚╚µż┘żļż╚║ŪĮj55%╣ŌżżĪŻŲ▒══ż╦▒ķōQē”╬üżŽHaswellż╚╚µż┘żļż╚║ŪĮj46%ĪóØi└ż┬Õ×æēäż╚żŽ║ŪĮj66%╣ŌżżĪūż╚Įęż┘żļĪŻ

┐▐2ĪĪAMD Embedded Solutionsŗ╠ńProduct Management & MarketingŗźŪźŻźņź»ź┐żŪżóżļKamal KhouriĢ■

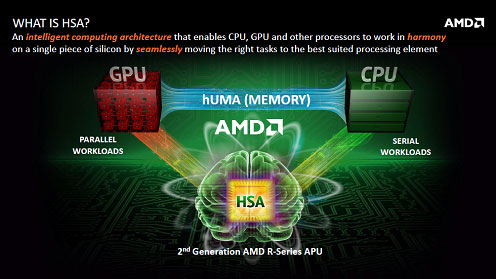

Intelż╬HaswellżŽ22nmż╬FinFETźūźĒź╗ź╣żŪĪóAMDż╬Bald EagleżŽ28nmźąźļź»CMOSźūźĒź╗ź╣żŪżóżļĪŻŠ’╝▒żŪżŽ╚∙║┘▓Įż╣żļöĄż¼└Łē”żŽæųż¼żļżŽż║ż└ż¼ĪóKhouriĢ■żŽHaswellżĶżĻżŌ└Łē”ż¼╣Ōżż═²Įyż“ĪóHSAĪ╩Heterogeneous System ArchitectureĪ╦źóĪ╝źŁźŲź»ź┴źŃĪ╩╗▓╣═½@╬┴2Ī╦ż“║╬żĻŲ■żņż┐ż┐żßĪóż╚└Ō£½ż╣żļĪŻ

HSAżŽĪóCPUż╚GPUż“ĮĖ└čż╣żļAPUż╦Ė■żżż┐źóĪ╝źŁźŲź»ź┴źŃżŪżóżĻĪóCPUż╚GPUż╬źßźŌźĻżŽ┤░µ£ż╦ź│źęĪ╝źņź¾ź╚ż╦Č”Ń~żĄżņżŲżżżļĪŻ╬Ńż©żąCPUżŪźĘźĻźóźļż╩źĖźńźųż“ĪóGPUżŪźčźķźņźļż╩źĖźńźųż“╝┬╣įżĄż╗żļŠņ╣ńż╦żŽĪóźßźŌźĻż╬ź│źęĪ╝źņź¾źĘż¼┤░µ£ż╦ż╚żņżŲżżż╩ż»żŲżŽĪó²ŗ├µżŪĪų┬įż├ż┐Īū(źĒź├ź»)ż“żĘż╩ż▒żņżąż╩żķż║ĪóĖ▀żżż╬żõżĻż╚żĻż╦╗■┤ųż¼ż½ż½ż├żŲżĘż▐ż”ĪŻCPUż╚GPUż¼ź¬ź¾ź┴ź├źūżŪżŌź¬źšź┴ź├źūĪ╩PCIźąź╣Ī╦żŪżŌź│źęĪ╝źņź¾źĘżŽŲ▒══ż╦─_═ūż└ż├ż┐ĪŻHSAżŪżŽĪóhUMAż╚Ō}żųźąź╣ż“ŠW├ōż╣żļĪŻż╣ż┘żŲż╬źßźŌźĻȧ┤ųżŪźßźŌźĻż╬░╠Åøż“╗žż╣ź▌źżź¾ź┐ż“╗╚ż”ż│ż╚żŪĪóCPUż╚GPUżžż╬┐ČżĻ╩¼ż▒ż“źŽĪ╝ź╔ź”ź©źóż¼źĄź▌Ī╝ź╚ż╣żļż╬ż└ż╚ĪóKhouriĢ■żŽĮęż┘żļĪŻ

ź▐źļź┴ź│źóżõCPUż╚GPUĪóDSPż╩ż╔░█ż╩żļź│źóĪóŲ▒¹|ż╬ź│źóż╩ż╔żŌ┤▐żßżŲµ£żŲż╬źūźĒź╗ź├źĄź│źóż¼źßźŌźĻż“Č”Ń~żŪżŁżļ╗┼┴╚ż▀ż╦ż╩ż├żŲżżżļż│ż╚żŪĪó╣ŌÅ]└Łē”ż“įużŲżżżļĪŻżĄżķż╦ĪóHSAżŪżŽĪóOpenCLż“╗╚ż├żŲźūźĒź░źķź▀ź¾ź░ż╣żļŠņ╣ńżŪżŌĪóźßźŌźĻźŪĪ╝ź┐ż╬źĒź├ź»ż“╣═ż©ż╩ż»żŲżŌż╣żÓż╚żżż”ĪŻ

┐▐3ĪĪHSAźóĪ╝źŁźŲź»ź┴źŃżŪ┤░µ£ż╩źßźŌźĻź│źęĪ╝źņź¾źĘż“╝┬ĖĮĪĪĮąųZĪ¦AMD

AMDżŽż│ż╬×æēäż╬ż█ż½ż╦żŌGPU├▒öüż╬AdelaarżŌźĄź¾źūźļĮą▓┘ż╣żļĪŻżĄżķż╦Īó─ŃŠ├õJ┼┼╬üź┐źżźūż╬GźĘźĻĪ╝ź║APUĪųSteppe EagleĪūż╩ż╔żŌŖZżżż”ż┴ż╦╚»╔Įż“═Į─ĻżĘżŲżżżļĪŻ

╗▓╣═½@╬┴

1. ┴╚ż▀╣■ż▀źĘź╣źŲźÓż╦ż╩żėż»AMD/IPextreme/MentorĪ┴EuroAsia2013ż½żķ(2) (2013/11/06)

2. ╩Ż╗©ż╩SoCż“į~├▒ż╦└▀╝Ŗż╣żļż┐żßż╬ź─Ī╝źļż“║YØŹ▓ĮżĘżĶż”Ī▌HSAż¼Ō}żėż½ż▒ (2013/9/13)