Š«Ę┐Ī”─Ń▓┴│╩Ī”─ŃŠ├õJ┼┼╬üż╬FPGAż¼Įń─┤ż╦└«─╣

4ĘŅĪóGlobalpress Connection╝ń╠¢(h©żo)ż╬euroasiaPRESS 2014ż¼źĘźĻź│ź¾źąźņĪ╝żŪ│½ż½żņż┐ĪŻż│ż│┐¶ŃQĪóŠ«Ę┐Ī”─Ń▓┴│╩FPGAż╦źšźŻź├ź╚ż╣żļ▌xŠņż¼żóżĻĪóäPżėżŲżżżļż│ż╚ż“╩¾żĖżŲżŁż┐(╗▓╣═½@╬┴1)ĪŻLattice Semiconductorż╚SilegożŽĪó─Ń▓┴│╩Ī”─ŃŠ├õJ┼┼╬üĪ”Š«Ę┐▓Įż╦ż│ż└ż’żĻż╩ż¼żķĪóT2MĪ╩ź┐źżźÓź─Ī╝ź▐Ī╝ź▒ź├ź╚Ī╦ż“║Ū─_═ū▓▌¼öż╦ĘŪż▓żŲżżżļĪŻ

┐▐1ĪĪLatticeż╬Ęeż─3¹|╬Óż╬╝ń╬ü×æēäĪĪiCE40(║Ė)ĪóMachXOS3(├µ▒¹)ĪóECP5(īÜ)ĪĪĮąųZĪ¦Lattice Semiconductor

LatticeżŽĪóź╣źįĪ╝ź╔ż╚Įė╔꿥Ī╩Speed & AgilityĪ╦ż“źŌź├ź╚Ī╝ż╚żĘżŲĪó┐¶Ø▓ź╗ź¾ź╚Ąķż╬Š«Ę┐ż╬iCE40źĘźĻĪ╝ź║ż╚Īó5Ī┴15ź╔źļĄķż╬ECP5×æēäĪóżĮż╬├µ┤ų2Ī┴5ź╔źļĄķżŪI/O┼÷ż┐żĻż╬▓┴│╩ż¼║ŪżŌ─ŃżżMachXOS3×æēäźĘźĻĪ╝ź║ż╦╬üż“Ų■żņżŲżŁż┐Ī╩┐▐1Ī╦ĪŻĪų1ź╔źļż╦żŌ╦■ż┐ż╩żżFPGAĪ╩iCE40ż╩ż╔Ī╦żŽĪó▓»├▒░╠żŪ╚╬Ūõż╣żļ×æēäżŪżóżĻĪóFPGAż╬ź▐ź»ź╔ź╩źļź╔ż╚╣═ż©żŲżĶżżĪūż╚Ų▒╝ęCEOż╬Darin BillerbeckĢ■(hu©¼)Ī╩┐▐2Ī╦żŽĖ└ż”ĪŻ

┐▐2ĪĪ Lattice╝ęCEOż╬Darin BillerbeckĢ■(hu©¼)

║ŻövĪóLatticeż¼╚»╔ĮżĘż┐FPGAżŽĪó╣Ō└Łē”ż╦║Ū┼¼▓ĮżĘż╩ż¼żķŠ«Ę┐▓Įż“░▌Ęeż╣żļECP5×æēäĪŻ10mmĪ▀10mmż╬Š«żĄż╩źūźķź╣ź┴ź├ź»źčź├ź▒Ī╝źĖż╦200░╩æųż╬I/Oźįź¾ż“Ū█ÅøżĘĪó8╦³5000Ė─ż╬LUTĪ╩look up tableĪ╦źĒźĖź├ź»ź©źņźßź¾ź╚ż╚SERDESĪ╩─Š╩┬š`╩č┤╣Ī╦źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“ĮĖ└čżĘżŲżżżļĪŻ3.25Gbpsż╬╣ŌÅ]źżź¾ź┐Ī╝źšź¦Ī╝ź╣żŪŠ├õJ┼┼╬üżŽ0.25Wµć┼┘ż╦╝²żßżŲżżżļĪŻ╣ŌÅ]źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż╚żĘżŲĪóLVDSżõDDR3ĪóPCI ExpressĪóGigabit Ethernetż╩ż╔ż╦×┤▒■żĘĪó3.25Gbpsż“│╬Ū¦żĘżŲżżżļĪŻ

▒■├ōż╚żĘżŲżŽĪóź╣źŌĪ╝źļź╗źļż╩ż╔ż╬Ę╚┬ė┤├ŽČ╔├ōż╦źŪźĖź┐źļźšźĒź¾ź╚ź©ź¾ź╔ASIC/ASSPż╬ź│ź¾źčź╦ź¬ź¾ź┴ź├źūż╚żĘżŲ╗╚ż”ĪŻ─╠┐«├ōż╬Ų╚śOźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“└▀ż▒ż┐żĻĪóź┘Ī╝ź╣źąź¾ź╔źŌźŪźÓżõźóź╩źĒź░źšźĒź¾ź╚ź©ź¾ź╔ż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż╩ż╔ż“LUTż╩ż╔żŪ║ŅżĻĮążĘż┐żĻż╣żļż│ż╚żŪ║╣╩╠▓ĮżŪżŁżļĪŻźŪźĖź┐źļźšźĒź¾ź╚ź©ź¾ź╔ż╬ASIC/ASSPż╦żŽĪóDUC/DDCĪ╩digital up conversion / digital down conversionĪ╦żõĪóźčź’Ī╝źóź¾źūż╦Ų■╬üż╣żļāSĘ┴ż“öU(ku©░)Ė┬ż╣żļCFRĪ╩Crest Factor ReductionĪ╦ż╩ż╔ż╬övŽ®ż“ŲŌē┼żĘżŲżżżļż┐żßĪóECP5ż╦żŌżĮżņżķż╦×┤▒■ż╣żļövŽ®ż“ĮĖ└čżĘżŲżżżļĪŻ

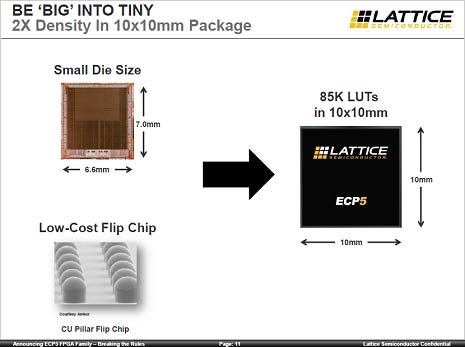

źūźĒź╗ź╣żŽ40nmż└ż¼Īó28nmż╬┬Š╝ę×æēäż╚╚µż┘żŲŠ«Ę┐ż╦żŪżŁżļż╚żżż”ĪŻ85kż╬LUTżŪżŽŪ█└■ż¼į~├▒ż╦ż╩żĻ║Ū┼¼▓ĮżŪżŁżļż┐żßż╚żĘżŲżżżļĪŻż▐ż┐DSPżŌĮĖ└čżĘżŲż¬żĻĪóźėźŪź¬ź│Ī╝źŪź├ź»żõźżźßĪ╝źĖ┐«ęÄ(gu©®)ĮĶ═²źūźĒź╗ź├źĘź¾ź░ĄĪē”ż“╝┬ĖĮżĘżõż╣żżĪŻź┴ź├źūźĄźżź║żŽ7.0mmĪ▀6.6mmżŪĪóCuźįźķĪ╝ż“Ę┴└«żĘż┐źšźĻź├źūź┴ź├źūżŪ╝┬äóż╣żļĪ╩┐▐3Ī╦ĪŻDiamondż╚Ō}żų│½╚»ź─Ī╝źļżõĪóIP/źĻźšźĪźņź¾ź╣└▀╝Ŗź─Ī╝źļĪóźŽĪ╝ź╔ź”ź©źó│½╚»ź▄Ī╝ź╔ż“├ō┴TżĘżŲżżżļĪŻ

┐▐3ĪĪ40nmźūźĒź╗ź╣żŪżŌŠ«żĄż╩FPGAĪĪĮąųZĪ¦Lattice Semiconductor

╣Į└«▓─╩čż╬ź▀ź»ź╣ź╚źĘź░ź╩źļ×æēä

żŌż”1╝ęż╬SilegożŽĪóż│żņż▐żŪźŪźŻź╣ź»źĻĪ╝ź╚żõ║YØŹźĒźĖź├ź»ż╩ż╔ż╬ŗēäż“ÅøżŁ┤╣ż©żļźėźĖź═ź╣ż“╣įż├żŲżŁż┐ĪŻĪų║ŻżŽŗī2źšź¦Ī╝ź║ż╦Ų■ż├ż┐Īūż╚Ų▒╝ęź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷VPż╬John McDonaldĢ■(hu©¼)(┐▐4ż╬║Ė)żŽĮęż┘żļĪŻØŖż╦Ų▒╝ęż¼╬üż“Ų■żņżŲżŁż┐ź▀ź»ź╣ź╚źĘź░ź╩źļźóźņźżż╬GreenPAKźĘźĻĪ╝ź║ż“CMICĪ╩Configurable Mixed-signal ICĪ¦źĘĪ╝ź▀ź├ź»ż╚╚»▓╗Ī╦ż╚ć@¤²ż▒ĪóĄĪē”ż“║ŅżĻ─Šż╣ż│ż╚ż╬żŪżŁżļ×æēäż╚░╠Åø¤²ż▒ż┐ĪŻ

┐▐4ĪĪSilego╝ęź▐Ī╝ź▒źŲźŻź¾ź░VPż╬John McDonaldĢ■(hu©¼)(║Ė)ż╚ź▐Ī╝ź▒źŲźŻź¾ź░źŪźŻźņź»ź┐ż╬Nathan JohnĢ■(hu©¼)

┐▐5żŪżŽĪóźūźĒź░źķź▐źųźļż╩╚ŠŲ│öü×æēäż“ĮĖ└č┼┘ż╬╣ŌżżĮńż╦FPGAĪóź▐źżź│ź¾ĪóCMICż╚┐ā(j©®)żĘż┐ĪŻFPGAżŽźŽĪ╝ź╔ź”ź©źóż“źūźĒź░źķźÓżŪ╩čż©żļż╬ż╦×┤żĘżŲĪóź▐źżź│ź¾żŽźĮźšź╚ź”ź©źóż“źūźĒź░źķźÓż╣żļż│ż╚żŪ╩čż©żļźŪźąźżź╣żŪżóżĻĪóCMICżŽź▐źżź│ź¾żĶżĻżŌį~├▒ż╦źŽĪ╝ź╔żŪĄĪē”ż“śOĮy(t©»ng)ż╦╩čż©żķżņżļźŪźąźżź╣ż╚░╠Åø¤²ż▒żŲżżżļĪŻ

┐▐5ĪĪSilegoż╬×æē俎ź▐źżź│ź¾żĶżĻżŌį~├▒ż╦źūźĒź░źķźÓżŪżŁżļĪĪĮąųZĪ¦Silego

GreenPAKżŽĪó╔įĦ╚»└ŁźßźŌźĻż“┤╦▄ż╚ż╣żļźūźĒź░źķź▐źųźļż╩ź▀ź»ź╣ź╚źĘź░ź╩źļICżŪĪó│½╚»ź─Ī╝źļż╦Ø{▌^ż╣żļż╚Īóż█ż¾ż╬┐¶╩¼żŪźūźĒź░źķźÓ╣Į└«żŪżŁżļż╚żżż”ĪŻ4źėź├ź╚żóżļżżżŽ8źėź├ź╚ż╬ź▐źżź│ź¾żõź░źļĪ╝źĒźĖź├ź»Īóźņź┘źļźĘźšź┐Ī╝ĪóźĻź╗ź├ź╚┐«ęÄ(gu©®)Īó┼┼░ĄźŌź╦ź┐Ī╝ż╩ż╔ż╬ĄĪē”ż“1ź┴ź├źūż╦┼ļ║▄ż╣żļĪŻź▐źżź│ź¾ż╬öU(ku©░)ĖµĄĪē”żŽź╣źŲĪ╝ź╚ź▐źĘź¾żŪ╝┬ĖĮż╣żļĪŻżŌż┴żĒż¾Īó“£═Ķż╬źŪźŻź╣ź»źĻĪ╝ź╚żõ║YØŹźĒźĖź├ź»ż╬ĮĖ└č▓ĮżŌ▓─ē”żŪżóżļĪŻ║ŪŠ«ż╬ICżŽGreenPAK3Ī╩SLG46110VĪ╦żŪĪóICźčź├ź▒Ī╝źĖżŽ1.6mmĪ▀1.6mmĪ▀0.55mm(Ė³)ż╬12źįź¾STQFNź┐źżźūżŪżóżļĪŻ

ż│ż╬ICż╦żŽźóź╩źĒź░ŗēäĪóźŪźĖź┐źļźĒźĖź├ź»ĪóźūźĒź░źķź▐źųźļż╩Ū█└■ĪóźšźņźŁźĘźųźļż╩I/OĪó╚»┐Č▀_(d©ó)Īó╔įĦ╚»└ŁźßźŌźĻż¼ĮĖ└迥żņżŲżżżļĪŻż│żņż█ż╔Š«żĄż╩źūźĒź░źķź▐źųźļźŪźąźżź╣żŽ┘T║▀żĘż╩żżż╚żżż”ĪŻ╔įĦ╚»└ŁźßźŌźĻż╦żŽ─Ńź│ź╣ź╚ż╦ż╣żļż┐żßOTPĪ╩One time programĪ╦ż“║╬├ōżĘżŲżżżļĪŻ├▒▓┴żŽĪó100╦³Ė─ĻP(gu©Īn)Ų■╗■żŪ12ź╗ź¾ź╚(12▀ģ)ż╚ŖWżżĪŻ

ż│żņż█ż╔ż▐żŪż╦Š«żĄż╩ŗēäż¼ØŁ═ūż╚żĄżņżļ╩¼╠ŅżŽĪ󟔟¦źóźķźųźļ├╝¼Źżõź╣ź▐Ī╝ź╚źšź®ź¾ż╩ż╔ĪóŠ«Ę┐▓Įż╬═ūĄßż¼Ėʿʿżż╚ż│żĒżŪżóżļĪŻĄĪē”ż╚żĘżŲĪóźĻź╗ź├ź╚öU(ku©░)Ėµżõ┼┼Ė╗ż╬źĘĪ╝ź▒ź¾ź╣Īóźąź├źŲźĻźŌź╦ź┐Ī╝Ī󟔟®ź├ź┴ź╔ź├ź░ź┐źżź▐Ī╝Īóź┐źżź▀ź¾ź░┐«ęÄ(gu©®)╚»Ö┌▀_(d©ó)ż╩ż╔ż¼żóżļĪŻ└▀╝Ŗź─Ī╝źļGPAK DesignerźĮźšź╚ż╚└@├ō│½╚»ź▄Ī╝ź╔ż“├ō┴TżĘżŲżżżļĪŻ

┐▐6ĪĪCMICż╬ŪõżĻæųż▓żŽż│ż│1Ī┴2ŃQŠå╗\żĘżŲżżżļĪĪĮąųZĪ¦Silego

ż│ż╬GPAKźšźĪź▀źĻżŽ4ŃQØiż╦║ŪĮķż╬×æēäż“Įą▓┘żĘżŲ░╩═ĶĪó╩Å╝ŖżŪ10▓»Ė─Įą▓┘ż“ĄŁŹ{żĘż┐ż╚żżż”ĪŻØŖż╦Īó2013ŃQż╬Įą▓┘┐¶żŽ4▓»2000╦³Ė─ż╚Šå╗\ĪóŪõżĻæųż▓żŌäPżėż┐(┐▐6)ĪŻ├µ╣±żŪż╬┤Ų£åź½źßźķ├ōż╚źŌźąźżźļź┐źųźņź├ź╚├ōż╦Ūõżņż┐ż╚żĘżŲżżżļĪŻ0.18µmCMOSźūźĒź╗ź╣żŪ└▀╝ŖĪó×æļ]żŽźšźĪź”ź¾ź╔źĻż╦░══ĻżĘżŲżżżļĪŻ

╗▓╣═½@╬┴

1. ┐ʿʿż▌xŠņ│½¹£ż¼▓─ē”ż╦ż╩ż├ż┐FPGAČ╚─cĪóź┴źŃź¾ź╣ż╚Č╝░ęż¼Č”┘T(2) (2010/05/19)