┐ʿʿż▌xŠņ│½¹£ż¼▓─ē”ż╦ż╩ż├ż┐FPGAČ╚─cĪóź┴źŃź¾ź╣ż╚Č╝░ęż¼±é┘T(2)

FPGAźėźĖź═ź╣ż¼╩č╦ŲżĘżŲżŁżŲżżżļĪŻØiövĪóä▌źČźżźĻź¾ź»ź╣ż╚źóźļźŲźķż╚żżż”2äėż╬Ų░żŁż“Šę▓żĘż┐ż¼Īó║ŻövżŽźĒĪ╝ź©ź¾ź╔▌xŠņż╦┐ʿʿż▒■├ōż¼ĮążŲżŁżŲżżżļż╬ż“Ė½żŲżżż»ĪŻ╝┬żŽż│ż│ż¼┐ʿʿż▌xŠņż╦ż╩ż├żŲżżżļĪŻ

źķźŲźŻź╣ż╬źĘźńĪ╝ź¾Ī”źķźżźĻĪ╝Ģ■(īÜ)ż╚ź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷VPż╬ź└ź░Ī”źŽź¾ź┐Ī╝Ģ■

żĘż½żĘĪóź▓Ī╝ź╚æä╠Žż¼1╦³░╩▓╝ż╬Š«żĄż╩æä╠ŽżŪżŌFPGAż╚żĘżŲ╗╚ż©żļ▒■├ōż¼ĮążŲżŁż┐ĪŻżĘż½żŌźųźņź├ź╔ź▄Ī╝ź╔┬Õż’żĻżŪżŽż╩żżĪŻżĮż╬ż▐ż▐▒■├ō×æēäż╦╗╚ż©żļź┴ź├źūżŪżóżļĪŻ╬Ńż©żąĪóżżż’żµżļź░źļĪ╝źĒźĖź├ź»żõ£pŲ░ŗēäż“ż▐ż╚żßżļż╚żżż”▒■├ōż¼żóżļĪŻż│żņż▐żŪżŽLSIż╬ĮĖ└č┼┘ż“æųż▓żŲżŌĪó£pŲ░ŗēäżõź░źļĪ╝źĒźĖź├ź»ż╩ż╔ż¼╗─żĻĪóż│żņżķż¼┴T│░ż╚ĮjżŁż╩╝┬äóĀC└čż“žéżßżŲżŁż┐ĪŻ£pŲ░ŗēäżĮż╬żŌż╬żŽŠ«żĄżżż¼╝┬äóżĘż┐ĀC└迎żĮżņż█ż╔Š«żĄż»ż╩ż├żŲżżż╩żżż│ż╚ż¼¾HżżĪŻ╬Ńż©żą°BŃ^żõź│ź¾źŪź¾źĄż“20Ė─╝┬äóżĘż┐┤łżŽ┐¶cm╩┐öĄż╦Ą┌żųż│ż╚ż¼żóżļĪŻż╗ż├ż½ż»1608żõ0804ż╚żżż├ż┐«ĆŠ«Ę┐ż╬ŗēäż“╗╚ż├żŲżŌ╝┬äóĀC└čż¼Š«żĄż»ż╩żķż╩ż▒żņżą▓┐ż╦żŌż╩żķż╩żżĪŻż│żņż“ż’ż║ż½1Ī┴2mm│čż╬ĮjżŁżĄż╬╚ŠŲ│öüFPGAź┴ź├źūżŪÅøżŁ┤╣ż©żļż│ż╚ż¼żŪżŁżļĪŻźķźŲźŻź╣ź╗ź▀ź│ź¾ź└ź»ź┐żõĪóźĘźņź┤źŲź»ź╬źĒźĖĪ╩Silego TechnologyĪ╦żŽż│ż│ż╦ĮjżŁż╩▌xŠņż¼żóżļż╚Ė½żŲżżżļĪŻ

2010ŃQż╬ŗī1╗═╚Š┤³ż╦ż¬ż▒żļźķźŲźŻź╣ż╬ŪõżĻæųż▓żŽĪó2009ŃQŗī4╗═╚Š┤³ż╬Č╚└ėżĶżĻżŌ28%╗\ż╬7040╦³ź╔źļż╦ż╩żĻĪóĮŃŠW▒ūżŽ1110╦³ź╔źļż╚ż╩ż├ż┐ĪŻż│ż╬Ūõæų╣ŌżŽĪó2008ŃQż╬źņź┘źļĪ╩6000╦³ź╔źļĪ╦żĶżĻżŌ╣ŌżżĪŻż│żņżŽŲ▒╝ęż╬×æēä└’ŠSż“źŽźżź©ź¾ź╔ż½żķźĒĪ╝ź©ź¾ź╔ż▐żŪ╔²╣Łż»Š}²Xż▒żŲżżż┐żŌż╬ż“ź▀ź├ź╔źņź¾źĖż╩żżżĘźĒĪ╝ź©ź¾ź╔ż╦ĮĖ├µż╣żļż│ż╚ż╦╩čż©żŲżŁż┐ż│ż╚ż¼┴šĖ∙żĘż┐ĪŻĪų╔įČĘżŪźµĪ╝źČĪ╝ż¼źĒĪ╝ź│ź╣ź╚ż“╝{ĄßżĘżŲźĒĪ╝ź│ź╣ź╚Ī”źĒĪ╝ź©ź¾ź╔Š”ēäż“ĄßżßżŲżŁż┐ż┐żßż╦Īóż’żņż’żņżŽ└«─╣żĘż┐Īūż╚Ų▒╝ę╣Ō╠®┼┘źĮźĻźÕĪ╝źĘźńź¾├┤┼÷ż╬VPĘ¾źĖź¦ź═źķźļź▐ź═źĖźŃĪ╝ż╬źĘźńĪ╝ź¾Ī”źķźżźĻĪ╝Ģ■żŽĖ└ż”ĪŻ

źķźŲźŻź╣żŽżŌżŽżõ╔įČĘØiż╬ŪõżĻæųż▓ż“«Ćż©ż┐

źķźŲźŻź╣żŽźšźķź├źĘźÕźßźŌźĻĪ╝ż“ŲŌē┼żĘĪóLUTĪ╩źļź├ź»źóź├źūźŲĪ╝źųźļĪ╦ż“┤╦▄├▒░╠ż╚ż╣żļFPGAźßĪ╝ź½Ī╝ż└ĪŻ╠Ą└■ż¬żĶżėŃ~└■ż╬─╠┐«źżź¾źšźķżõĪóź╗źŁźÕźĻźŲźŻż╚┤Ų£åźĘź╣źŲźÓż╬żĶż”ż╩ŠÅČ╚├ōż╦żŽź▀ź├ź╔źņź¾źĖż╬×æēäż“─¾ČĪż╣żļĪŻĘ╚┬ėĄĪ▀_żõķ]ŠĮźŲźņźėż╩ż╔░cÖ┌ĄĪ▀_ż╬į~├▒ż╩─┤┼Dż“╣įż”ż┐żßż╬×æēäż╚Īóź░źļĪ╝źĒźĖź├ź»żõ£pŲ░ŗēäż“ż▐ż╚żßżļż┐żßż╬×æēäż“źĒĪ╝ź©ź¾ź╔▌xŠņż╦Ė■ż▒żŲżżżļĪŻLUT┐¶żŪżżż©żą1╦³░╩▓╝ż╬źĒźĖź├ź»ż“źĒĪ╝ź©ź¾ź╔ż╚─Ļ▒IżĘżŲżżżļĪŻźšźķź├źĘźÕźßźŌźĻĪ╝żŽ╬Ńż©żą┼┼╗ęĄĪ▀_ż╬┼┼Ė╗ż“ź¬ź¾żĘż┐żķ║tĪó╬®ż┴æųż¼żļżĶż”ż╦ØŁ═ūż╩źĘĪ╝ź▒ź¾ź╣żõ╠┐╬ßż╩ż╔ż“│╩Ū╝żĘżŲż¬ż»ż┐żßż╦╗╚ż”ĪŻ

╬Ńż©żąĪóķ]ŠĮźŲźņźėżõźŪźĖź┐źļź½źßźķż╬▒■├ōżŪżŽ┤╦▄┼¬ż╩▓ĶćĄĮĶ═²żŪżŽż╩ż»ĪóĄĪē”ż“╝{▓├żĘż┐żĻ╩čż©ż┐żĻż╣żļżĶż”ż╩╝■╩šövŽ®ż╦FPGAż“╗╚ż”ĪŻ┐¦▌ö┘ćżõź╣ź»źĻĪ╝ź¾źĄźżź║ż╬╚µ╬©ż╩ż╔ż╬╩čśŗż╦─Ńź│ź╣ź╚żŪ╗╚ż©żążĮżņż█ż╔ĮjżŁż╩ź▓Ī╝ź╚┐¶żŽ═ūżķż║ĪóżÓżĘżĒLUTż“ź┘Ī╝ź╣ż╦żĘżŲżżżļż┐żßį~├▒ż╦źūźĒź░źķź▀ź¾ź░żŪżŁżļĪŻ│½╚»ź─Ī╝źļżŽ╣ŌĄķĖ└ĖņżõźūźĒź░źķź▀ź¾ź░Ė└ĖņżŽ═ūżķż╩żżĪŻį~├▒ż╩GUIźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“╗╚ż├żŲĪó▓ĶĀCż“Ė½ż╩ż¼żķövŽ®ż“└▀╝Ŗż╣żļż┐żßĪó─Ńź│ź╣ź╚żŪż┴żńż├ż╚żĘż┐övŽ®ż╬╩čśŗż¼żŪżŁżļż╚żżż”▒■├ōż“┴└ż”ĪŻ╬Ńż©żą4000ZEźĘźĻĪ╝ź║ż╬×æēäż└ż╚Īó┬įĄĪ╗■┼┼╬«ż¼10”╠Aż╚─Ńż»ĪóŲ░║Ņ┼┼░ĄżŽ1.6Vż╚─Ńżż┼┼░ĄżŪżŌŲ░║Ņż╣żļż┐żßŠ├õJ┼┼╬üż“▓╝ż▓żļż│ż╚ż¼żŪżŁżļż┐żßĘ╚┬ėĄĪ▀_ż╦Ė■ż»ĪŻ

ICż╬źĄźżź║ż¼ż’ż║ż½4mm│čż╬64ź▄Ī╝źļż╬BGAĪĪ4000ZE

▓├ż©żŲĪó┼┼Ė╗├ōICĪóż╣ż╩ż’ż┴źčź’Ī╝ź▐ź═źĖźßź¾ź╚ICĪ╩PMICż╚żŌżżż”Ī╦żŌźūźĒź░źķźÓ▓─ē”żŪĪó▐k╚╠┼¬ż╩źóź╩źĒź░ż╬DC-DCź│ź¾źąĪ╝ź┐ż“źŪźĖź┐źļöUĖµż╣żļż┐żßż╬PMICźĘźĻĪ╝ź║ĪóPower Manger IIżŌżóżļĪŻ╬Ńż©żą×æēä686żŽ0.72Vż½żķŲ░║ŅżĘĪó605żŽ¾H┐¶ż╬┼┼Ė╗źņĪ╝źļż“źŌź╦ź┐Ī╝ż╣żļĪŻźżź¾źŲźļż╬źūźĒź╗ź├źĄź┴ź├źūż╬żĶż”ż╦Īó╬Ńż©żą1.0ż½żķ1.2Vż▐żŪ0.01Vż║ż─║┘ż½ż»┼┼░Ąż“æųż▓▓╝ż▓ż╣żļżĶż”ż╩▒■├ōż╦Ė■ż»ĪŻż▐ż┐SoCż╬żĶż”ż╩ĮjżŁż╩źĘź╣źŲźÓź┴ź├źūżŪżŽ╩Ż┐¶ż╬┼┼Ė╗ż“╗╚ż”ż¼Īóż│żņżķż╬┼┼Ė╗źņĪ╝źļż“źŌź╦ź┐Ī╝ż╣żļż╬ż╦żŌ╗╚ż©żļĪŻ

źķźŲźŻź╣żŽź▀ź├ź╔źņź¾źĖż½żķźĒĪ╝ź©ź¾ź╔ż▐żŪź½źąĪ╝żĘż╩ż¼żķżŌźĒĪ╝ź©ź¾ź╔ż╦║ŻĖÕźšź®Ī╝ź½ź╣ż╣żļż╚żżż”ĪŻż│żņż╦×┤żĘżŲĪóźĘźņź┤Ī╩SilegoĪ╦╝꿎źĒĪ╝ź©ź¾ź╔ż└ż▒┼░öf┼¬ż╦źšź®Ī╝ź½ź╣ż╣żļĪó2001ŃQ└▀╬®ż╬┐ĘČĮFPGAźßĪ╝ź½Ī╝ż└ĪŻźĘźņź┤żŽĪóźĘźĻź│ź¾ż╚╗ęČĪż╬ż¬żŌż┴żŃżŪżóżļźņź┤ż“┴╚ż▀╣ńż’ż╗ż┐Si+Legoż½żķ▓±╝ęć@ż“¤²ż▒ż┐żĶż”ż╦Īóźņź┤źųźĒź├ź»ż╬żĶż”ż╦┴╚ż▀╬®żŲżŲ└▀╝ŖżŪżŁżļżĶż”ż╩źĒźĖź├ź»×æēäż“Ęeż─ĪŻź»źĒź├ź»öUĖµICżŪ╝┬└ėż╬żóżļŲ▒╝ęż└ż¼ĪóOTPĪ╩One-time programmableĪ╦ROMź┘Ī╝ź╣ż╬FPGAźĘźĻĪ╝ź║żŪżóżļGreenPak×æēäż╦▓├ż©Īóźßź┐źļź▐ź╣ź»żŪźūźĒź░źķźÓż╣żļGreenSak×æēäż“║ŪŖZźĻźĻĪ╝ź╣żĘż┐ĪŻGreenPakż¼PROMź┘Ī╝ź╣ż╩ż╬ż╦×┤żĘżŲĪóGreenSakżŽź▐ź╣ź»ROMź┘Ī╝ź╣ż╚żżż”Ślż└ĪŻ

GreenPakż╬övŽ®źųźĒź├ź»

Č”ż╦ź▀ź»ź╣ź╚źĘź░ź╩źļż╬ź▓Ī╝ź╚┐¶ż╬Š»ż╩żżFPGAżŪĪóź░źļĪ╝źĒźĖź├ź»żõźņź┘źļźĘźšź┐Īó┼┼Ė╗źĻź╗ź├ź╚ż╩ż╔ż╬żżż’żµżļżĮż╬┬Šż╬övŽ®ż“ź»źĻĪ╝ź¾źóź├źūż╣żļż╬ż╦╗╚ż”ĪŻ10┐¶Ė─ż╬ICżõ£pŲ░ŗēäż“żŁżņżżż╦╩ęż┼ż▒żŲ1ź┴ź├źūż╦ż▐ż╚żßżŲżĘż▐ż¬ż”Īóż╚żżż”▒■├ōżŪżóżļĪŻźūźĻź¾ź╚┤łövŽ®ż“Ė½żļż╚ĪóŠ«żĄż╩ICżõ£pŲ░ŗēäż¼╔wż▐ż├żŲżżżļĀC└迎░Ų│░Īóżąż½ż╦ż╩żķż╩żżĪŻż│żņżķż“ż’ż║ż½2mm│čż╬ź┴ź├źūżŪż▐ż╚żßżŲżĘż▐ż©żąĄĪ▀_ż╬Š«Ę┐▓Įż¼┐▐żņżļĪŻĪų8Ė─ż╬źņźĖź╣ź┐ż“╗╚żżż┐żżż╚żżż”żĶż”ż╩├ō²ŗż¼żĶż»żóżĻĪóż│ż│ż╦▌xŠņż¼żóżļĪūż╚Ų▒╝ęź╗Ī╝źļź╣Ī”ź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷VPż╬źĖźńź¾Ī”ź▐ź»ź╔ź╩źļź╔Ģ■Ī╩John McDonaldĪ╦żŽĖ└ż”ĪŻ

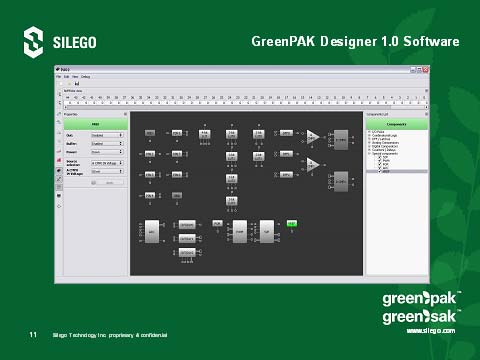

GreenPak/SakźĘźĻĪ╝ź║żŽĪóż╚żŌż╦╣ŌĄķźūźĒź░źķź▀ź¾ź░Ė└ĖņżŽ═ūżķż╩żżæųĪóź╣ź»źĻĪ╝ź¾ż“Ė½ż╩ż¼żķŗēäż“╩┬ż┘żŲövŽ®ż“╣Į└«żĘżŲżżż▒żļĪžźņź┤Ī┘öĄ╝░ż╬GUIźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż╦ż╩ż├żŲżżżļĪŻż│ż╬ż┐żßĪó└▀╝Ŗż¼į~├▒ż└ĪŻövŽ®ż╬ŗēäŠ╩¾Īó└▄¶öŠ╩¾ż“┤░└«żĄż╗ż┐żķĪóźĘźņź┤ż╦Š}┼Žż╗żąĪóźßź┐źļź▐ź╣ź»ż╬Green/SakżŪżĄż©Īó4ĮĄ┤ųżŪźĘźĻź│ź¾ż¼ĮążŲż»żļż╚żżż”ĪŻ

ż│ż”żżż├ż┐į~├▒ż╩└▀╝ŖövŽ®öĄ╝░żŽĪó8źėź├ź╚ż╬źóź╩źĒź░övŽ®║«║▄ż╬ź▐źżź»źĒź│ź¾ź╚źĒĪ╝źķżŪżóżļźĄźżźūźņź╣╝ęż╬pSoC×æēäż╚Ų▒żĖż└ĪŻ╝┬żŽĪóźĖźńź¾Ī”ź▐ź»ź╔ź╩źļź╔Ģ■ż╬Øi╬“żŽĪ󟥟żźūźņź╣ż╦żŌźĄźżź┐źżźÓĪ╩SiTimeĪ╦ż╦żŌżżż┐ż╚żżż”ĪŻźĄźżź┐źżźÓż╬MEMSż╦żĶżļź»źĒź├ź»öUĖµICżŌźĘźņź┤ż╬Ēö╣ń×æēäż└ĪŻ

ŗēäż“źķźżźųźķźĻż½żķź╔źķź├ź░żĘ±T└■ż╣żļż╚övŽ®ż“└▀╝ŖżŪżŁżļź─Ī╝źļ

Č”ż╦ź│ź¾ź┌źŲźŻź┐×æē俎8źėź├ź╚żóżļżżżŽ16źėź├ź╚ż╬ź▐źżź│ź¾ż└żĒż”ż¼ĪóĪųź▐źżź│ź¾żŽź│ź¾ź╚źĒĪ╝źķĄĪē”ż╦─_┼└ż¼Åøż½żņĪó└Łē”ż¼Ė┬żķżņżŲżżżļĪūż╚źķźŲźŻź╣ż╬źĘźńĪ╝ź¾Ī”źķźżźĻĪ╝Ģ■żŽĮęż┘żļĪŻĪųźŽĪ╝ź╔ź”ź©źóövŽ®├µ┐┤ż╬FPGAż╬öĄż¼└Łē”żŽĮążĘżõż╣żżĪŻżĘż½żŌź▐źżź│ź¾żŽCĖ└Ėņż╩ż╔żŪź│Ī╝ź╔ż“Į±żŁźóź╗ź¾źųźĻż╣żļØŁ═ūż¼żóżļĪūż╚żĘżŲżżżļĪŻ