XilinxĪóAIż“┤▐żßż┐┼²╣ńźĮźšź╚ź”ź©źóźūźķź├ź╚źšź®Ī╝źÓVITISż“╚»╔Į

Xilinxż¼├»żŪżŌ╚ŠŲ│öüź┴ź├źūż“ĘeżŲżļżĶż”ż╦ż╣żļż┐żßĪó╚ŠŲ│öüż└ż▒żŪżŽż╩ż»źĮźšź╚ź”ź©źóż“─_£åż╣żļ└’ŠSż╦Įąż┐ĪŻźūźĒź░źķźÓ▓─ē”ż╩FPGAż╚Ė└ż©ĪóźūźĒź░źķźÓżĘżõż╣żĄż╦żĶż├żŲĪóĮjżŁż╩║╣ż¼ĮążļĪŻźūźĒź░źķźÓżĘżõż╣żż│½╚»ź─Ī╝źļż“║Ņżļż┐żßż╬źĮźšź╚ź”ź©źóż¼śŗż╩żļ╔ߥ┌ż╬ź½ź«ż“É█żļĪŻ║ŻŲ³ĪóAI│½╚»ż“┤▐żÓ┼²╣ńźĮźšź╚ź”ź©źó│½╚»źūźķź├ź╚źšź®Ī╝źÓVITISż“╚»╔ĮżĘż┐ĪŻ

┐▐1ĪĪ│½╚»żĘżŲżŁż┐źūźĒź░źķźÓż╣żļż┐żßż╬źĮźšź╚ź”ź©źóż╦AI│½╚»żŌ╝{▓├ĪĪĮąųZĪ¦Xilinx

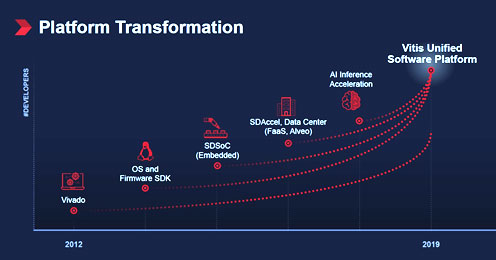

VitisĪ╩źąźżźŲźŻź╣ż╚Ų╔żÓĪ╦ż╦żŽĪóż│żņż▐żŪXilinxż¼│½╚»żĘżŲżŁż┐źĮźšź╚ź”ź©źóź─Ī╝źļż╬OSżõźšźĪĪ╝źÓź”ź©źóĪóSDKż╦▓├ż©Īó┴╚ż▀╣■ż▀├ōż╬SDSoCż╚ĪóĖÕĮęż╣żļSDAccelż“┼²╣ń▓ĮżĘĪ󿥿ķż╦AI└ņ├ōż╬│½╚»źĮźšź╚żŌ┼²╣ń▓ĮżĘżŲżżżļĪ╩┐▐1Ī╦ĪŻź▐źżź│ź¾ż╬┼²╣ń│½╚»ź─Ī╝źļż╬żĶż”ż╩ź│ź¾źčźżźķżõźóź╩źķźżźČĪóźŪźąź├ź¼ż╩ż╔żŌ┤▐ż▐żņżŲżżżļż¼Īó▓┐żĶżĻżŌź¬Ī╝źūź¾źĮĪ╝ź╣ż╬║Ū┼¼▓ĮżĄżņż┐źóźūźĻź▒Ī╝źĘźńź¾źĮźšź╚ź”ź©źóż¼400░╩æųżŌ┬Ęż├żŲżżżļĪŻ

ż│żņż▐żŪżŌXilinxżŽźĮźšź╚ź”ź©źóż╦╬üż“Ų■żņżŲżŁż┐ż¼Īó2Ī┴3ŃQØiż╦Xilinxż¼╚»╔ĮżĘż┐ĪóSDAccelż╚żżż”źĮźšź╚ź”ź©źó│½╚»ź─Ī╝źļżŽĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żõź»źķź”ź╔ŲŌż╦└▀ż▒ż┐FPGAż“▒¾│ų├Žż½żķ┴Ó║ŅżĘżŲFPGAż╬źūźĒź░źķźÓż“Į±ż»ź─Ī╝źļżŪżóżļĪŻFPGAż╬ŲŌ═Ųż“Į±żŁ┤╣ż©żķżņżļż┐żßĪóXilinxżŽśO╩¼żķż“ĪóFaaSĪ╩FPGA as a ServiceĪ╦ż╚Ō}ż¾żŪżŁż┐ĪŻ

XilinxżŽ║“ŃQ╚»╔ĮżĘ║ŻŃQĮą▓┘ż“│½╗ŽżĘż┐║Ūæų░╠ż╬źŽĪ╝ź╔ź”ź©źóżŪżóżļĪóVARSAL ACAPĪ╩Adaptive Compute Acceleration PlatformĪ¦┼¼▒■Ę┐▒ķōQ▓├Å]źūźķź├ź╚źšź®Ī╝źÓĪ╦żŪżŽĪóCPUż╦▓├ż©DSPżõAIź©ź¾źĖź¾ĪóżĮżĘżŲFPGAż“┴╚ż▀╣■ż¾żŪżżżļ(╗▓╣═½@╬┴1)ĪŻØŖż╦AIź©ź¾źĖź¾żŽźŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░ż╦ØŖ▓ĮżĘż┐DNNĪ╩źŪźŻĪ╝źūź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»Ī╦ż“┤░µ£ż╦╩╠övŽ®żŪ├ō┴TżĘżŲżżżļĪŻ

ż╩ż╝ĪóAIż“DNNż╦ØŖ▓ĮżĘż┐ż½ĪŻ╚ŠŲ│öüČ╚─cżŪżŽźĘźĻź│ź¾źĄźżź»źļżŽż½ż─żŲ4ŃQż╦▐k┼┘ż╚Ė└ż’żņĪó║ŪŖZżŪżŌ┐¶ŃQż┤ż╚ż╦╣ź╔įČĘż╬āSż¼żõż├żŲżŁżŲżżżļż¼ĪóĪų╝┬żŽDNNż╬┐ʿʿżźóźļź┤źĻź║źÓż╬│ū┐ĘżŽ3Ī┴4ź½ĘŅż┤ż╚ż╦ÅŚżŁżŲż¬żĻĪóźĘźĻź│ź¾źĄźżź»źļżĶżĻżŌÅ]żżŠåÅ]ż╦┐╩▓ĮżĘżŲżżżļ╩¼╠ŅżŪżóżļĪūż╚Xilinx╝ęźĮźšź╚ź”ź©źóĪóIPĪóAIźĮźĻźÕĪ╝źĘźńź¾ŗ╠ńĪó×æēäź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷VPż╬Ramine RoaneĪ╩źķź▀Ī╝ź¾Ī”źĒĪ╝źóź¾Ī╦Ģ■żŽĮęż┘żŲżżżļ(┐▐2)ĪŻAIż╬▒■├ōżŽżĄż▐żČż▐ż╩╩¼╠ŅżŪĖ½żķżņżļż¼ĪóżĮż╬80Ī┴90%żŽDNNżŪżóżļż╚żżż”ĪŻ

┐▐2ĪĪXilinx╝ęźĮźšź╚ź”ź©źóĪóIPĪóAIźĮźĻźÕĪ╝źĘźńź¾ŗ╠ńĪó×æēäź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷VPż╬Ramine RoaneĢ■

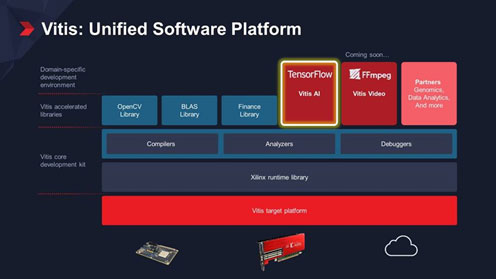

Vitisźūźķź├ź╚źšź®Ī╝źÓżŽĪóźĮźšź╚ź”ź©źóź╣ź┐ź├ź»ż“ź┘Ī╝ź╣ż╚żĘżŲż¬żĻ(┐▐3)Īóźūźķź░źżź¾żŪżĄż▐żČż▐ż╩źĮźšź╚ź”ź©źóŗēäż“ŲDżĻ¤²ż▒żķżņżļżĶż”ż╦ż╩ż├żŲżżżļĪŻżĘż½żŌ║YØŹ┼¬ż╩źķźżźųźķźĻżŽšl╔┘ż╦┬Ęż©żŲżżżļĪŻ

┐▐3ĪĪźĮźšź╚ź”ź©źóź╣ź┐ź├ź»ź┘Ī╝ź╣ż╬Vitisźūźķź├ź╚źšź®Ī╝źÓĪĪĮąųZĪ¦Xilinx

ź┘Ī╝ź╣ż╚ż╩żļ║Ū▓╝┴žż╬Vitisź┐Ī╝ź▓ź├ź╚źūźķź├ź╚źšź®Ī╝źÓżŽĪóövŽ®ź▄Ī╝ź╔żõ├ō┴TżĄżņż┐I/Oż╩ż╔ż“┼ļ║▄żĘżŲżżżļĪŻVitisź│źó│½╚»źŁź├ź╚ż╚Ō}ż¾żŪżżżļ2╚ųų`ż╬źņźżźõĪ╝żŽĪóź¬Ī╝źūź¾źĮĪ╝ź╣ż╬źūźĒź░źķźÓż¼┴÷żļźķźżźųźķźĻż“╩±│ńżĘżŲż¬żĻĪóżżżĒżżżĒż╩ź╔źßźżź¾┤ųż“öĪŲ░ż╣żļźŪĪ╝ź┐ż“┤╔═²ż╣żļĪŻż│ż╬źņźżźõĪ╝ż¼ź│ź¾źčźżźķżõźóź╩źķźżźČĪóźŪźąź├ź¼ż╬żĶż”ż╩├µ│╦ż╬│½╚»ź─Ī╝źļż“┤▐ż¾żŪżżżļĪŻ

ŗī3ż╬źņźżźõĪ╝żŪżŽĪó400°P░╩æųż╬║Ū┼¼▓ĮżĄżņż┐ź¬Ī╝źūź¾źĮĪ╝ź╣ż╬źóźūźĻź▒Ī╝źĘźńź¾ż¼Īó8Ė─ż╬VitisźķźżźųźķźĻż“─╠żĘżŲ╗╚ż©żļżĶż”ż╦ż╩ż├żŲżżżļĪŻ8Ė─ż╬źķźżźųźķźĻż╚żŽĪóVitis┤╦▄┼¬ż╩└■Ę┴┬Õ┐¶źĄźųźūźĒź░źķźÓĪ╩BLASĪ╦źķźżźųźķźĻż╚ĪóVitisźĮźļźąĪ╝źķźżźųźķźĻĪóVitisź╗źŁźÕźĻźŲźŻźķźżźųźķźĻĪóVitisźėźĖźńź¾źķźżźųźķźĻĪóVitisźŪĪ╝ź┐░ĄĮ╠źķźżźųźķźĻĪóVitis─Ļ╬╠┼¬źšźĪźżź╩ź¾ź╣źķźżźųźķźĻĪóVitisźŪĪ╝ź┐ź┘Ī╝ź╣źķźżźųźķźĻĪóVitis AIźķźżźųźķźĻżŪżóżļĪŻźĮźšź╚ź”ź©źó│½╚»ŪvżŽĪó║YØŹ┼¬ż╩APIż“╗╚ż├żŲĪóż│żņżķż½żķźóź»ź╗źķźņĪ╝źĘźńź¾ĄĪē”ż“Ō}żėĮąż╣ż│ż╚ż¼żŪżŁżļĪŻ

▓├ż©żŲĪóVitis AIŗēäż¼ż│ż╬źūźķź├ź╚źšź®Ī╝źÓż╬ĪųŪõżĻĪūż╦ż╩żļĄĪē”żŪĪóAI└ņ├ōövŽ®ż“║Ņżļż┐żßż╬DSAĪ╩Domain Specific ArchitectureĪ╦ż“┼ļ║▄żĘżŲżżżļĪŻDSAż¼żóżņżąĪóTensorFlowżõCaffeż╬żĶż”ż╩Č╚─c║YØŹż╬źšźņĪ╝źÓź’Ī╝ź»ż“╗╚ż├żŲXilinxż╬FPGAż“║Ū┼¼ż╦źūźĒź░źķźÓżŪżŁżļżĶż”ż╦ż╩żļĪŻż│ż╬ź─Ī╝źļżŽĪóAIż╬│žØ{żĄżņż┐źŌźŪźļż“ĪóFPGAæųżŪ┴÷żķż╗żļż╚1╩¼┤ųżŪ║Ū┼¼▓ĮżĘĪó░ĄĮ╠żĘź│ź¾źčźżźļż╣żļż╚żżż”ĪŻ

XilinxżŽ╝┬║▌ż╦Īó▒Ū楿“ź½źßźķżŪ╗ŻżĻĪóżĮż╬├µż╬┐═ż╬┤ķż“╗═│čżŪ░ŽżÓż╚żżż”║ŅČ╚ż“20┐═░╩æųż╦┼Žż├żŲż╣ż░ż╦żŪżŁżļż╚żżż”╝┬┘xż“Ė½ż╗ż┐ĪŻż┐ż└żĘĪóż│ż╬DSAżŽĪóNvidiaż¼żŌż─CUDAż╚żĶż»ō¶żŲż¬żĻĪóFPGAżŪ·t│½żĘżŲGANżõżĮż╬┬Šż╬ź½ź╣ź┐ź▐źżź╝Ī╝źĘźńź¾ż╦Ė■żżżŲżżżļżĶż”ż└ĪŻ

╗▓╣═½@╬┴

1. XilinxĪó«Ć╣ŌĄķ2.5D-LSIż╬µ£╦Ųż“£½żķż½ż╦ (2018/10/12)