IntelĪóČ\ĮčźĒĪ╝ź╔ź▐ź├źūż“╚»╔ĮĪó2025ŃQż╦TSMCż“╝{żżģsż»

Intelż¼ż│żņż½żķż╬źūźĒź╗ź╣ż╚źčź├ź▒Ī╝źĖź¾ź░Č\Įčż╬2025ŃQż▐żŪż╬źĒĪ╝ź╔ź▐ź├źūż“╚»╔ĮżĘż┐ĪŻźūźĒź╗ź╣×æļ]Č\Įčż╚źčź├ź▒Ī╝źĖź¾ź░Č\Įčż╬╬ŠöĄż“īÖż½żĘĪóIntel 7ż½żķIntel 4ĪóIntel 3ĪóIntel 20AĪ󿥿ķż╦Intel 18Aż╚Ō}żųźūźĒź╗ź╣ź╬Ī╝ź╔ż“└▀─ĻżĘ2025ŃQ░╩æTżŌ·t╦ŠżĘż┐ĪŻCEOż╬Pat GelsingerĢ■Ī╩┐▐1Ī╦żŽörż¾ż╦ĪųIntel is backĪūż╚żżż”Ė└±äż“Žó╚»żĘż┐ĪŻ

┐▐1ĪĪIntel CEOż╬Pat GelsingerĢ■ĪĪĮąųZĪ¦Intel Corp.

2ĘŅż╦GelsingerĢ■ż¼┼×ŪżżĘżŲIntelż╦╠ßż├żŲż»żļż▐żŪĪó║Ōē»Įą┐╚ż╬ØiCEOżŽĖ”ē|│½╚»┼Ļ½@ż╦Ų¾ż╬’Bż“Ų¦ż¾żŪżżż┐ż┐żßĪóź©ź¾źĖź╦źóż┐ż┴ż╬źŌź┴ź┘Ī╝źĘźńź¾żŽ▓╝ż¼żĻĪóĶī╝ężĘż┐ź©ź¾źĖź╦źóżŌ¾H┐¶żżż┐ĪŻØiŪżż╬CEOżŽź’ź¾ź▌źżź¾ź╚źĻźĻĪ╝źšż╚Ė½żķżņżŲżżż┐ĪŻØiŪżŪvż╬Øiż╬CEOż¼╔įĖC├@Ų░żŪ▌ŗżßż┐ż│ż╚żŪCEOż╦ż╩ż├ż┐ż└ż▒ż└ż├ż┐ż½żķż└ĪŻŠÅČ╚─cż½żķżŌĪóČ\Įčż╬ż’ż½żļ┐ʿʿżCEOż“Ąßżßżļ╠mż¼æųż¼ż├żŲżżż┐ĪŻ

GelsingerĢ■żŽ┼×Ūż┴ßĪ╣ĪóIDM 2.0öĄ┐╦ż“æ]ż┴ĮążĘĪóźŲź»ź╬źĒźĖĪ╝┤ļČ╚ż╬IntelżŽżŌż├ż╚×æļ]źūźĒź╗ź╣Č\Įčż╦╬üż“Ų■żņżļż│ż╚ż“┴╩ĄßżĘż┐Ī╩╗▓╣═½@╬┴1Ī╦ĪŻ║Żövż╬╚»╔ĮżŽĪóIDM 2.0ż╬ėXČĘż╚┐ĘźĒĪ╝ź╔ź▐ź├źūż╬╚»╔ĮżŪÉ║öü┼¬ż╦ż│żņż½żķż╬źŲź»ź╬źĒźĖĪ╝ż╬öĄĖ■ż“┐āż╣Šņż╚ż╩ż├ż┐ĪŻ

Intelż╬Super FinFETż╬10nmźūźĒź╗ź╣Ī╩╗▓╣═½@╬┴2Ī╦żŽĪóźßź┐źļźįź├ź┴żŽTSMCż╬7nmźūźĒź╗ź╣ż╚Ų▒┼∙żŪżóż├ż┐ż¼ĪóIntelż╬öĄż¼ęÆżņżŲżżżļĪóż╚żżż”źżźßĪ╝źĖż“ļmżß╣■ż▐żņżŲżŁż┐ĪŻĖĮ║▀Īó10nmźūźĒź╗ź╣żŽĪóźóźĻźŠź╩╣®ŠņĪ󟬟ņź┤ź¾╣®ŠņĪóźżź╣źķź©źļ╣®ŠņżŪ╬╠ŠÅżĘżŲż¬żĻĪóĪųż”ż▐ż»żżż├żŲżżżļĪūż╚GelsingerĢ■żŽĮęż┘żŲżżżļĪŻż│ż╬źūźĒź╗ź╣ż╚╚µż┘żļż╚7nmź╬Ī╝ź╔ż╦┴Ļ┼÷ż╣żļIntel 7źūźĒź╗ź╣żŽĪó└Łē”ż¼10Ī┴15%æųż¼ż├żŲżżżļż╚żżż”ĪŻ

Intel 7źūźĒź╗ź╣żŽź╚źķź¾źĖź╣ź┐źņź┘źļż╬║Ū┼¼▓Įż“┐▐żĻĪóŽ─żõ║Ó╬┴ż╬▓■╬╔ż╩ż╔żŪ┼┼╗ęż╬┴÷╣įÅ]┼┘ż“æųż▓ż┐ż╚ĪóŲ▒╝ęČ\Įč│½╚»ŗ╠ńż╬źĘź╦źóVPĘ¾źĖź¦ź═źķźļź▐ź═Ī╝źĖźŃĪ╝ż╬Ann KelleherĢ■żŽĮęż┘żŲżżżļĪŻź©ź═źļź«Ī╝öUĖµż“▓■║¤żĘźčź’Ī╝źŪźĻźąźĻČ\ĮčżŌ▓■╬╔żĘż┐ż│ż╚żŪĪó║ŻŃQĖÕ╚Šż╦żŽź»źķźżź©ź¾ź╚PCĖ■ż▒ż╬Alder Lake×æēäż¼ĮążŲż»żļż╚żżż”ĪŻż▐ż┐źŪĪ╝ź┐ź╗ź¾ź┐Ī╝├ōż╬Sapphire RapidsżŽ2022ŃQŗī1╗═╚Š┤³ż╦źĻźĻĪ╝ź╣żĄżņżļ═Į─Ļż└ż╚żżż”ĪŻ

żĄżķż╦4nmź╬Ī╝ź╔ż╦┴Ļ┼÷ż╣żļIntel 4źūźĒź╗ź╣ż“╗╚ż”ź»źķźżź©ź¾ź╚Ė■ż▒Meteor LakeĪ╩źßźŲźŻźóźņźżź»ż╚╚»▓╗Ī╦×æē俎Īó2021ŃQŗī2╗═╚Š┤³ż╦ĪóźŲĪ╝źūźżź¾ż╦Ų■żĻź│ź¾źįźÕĪ╝ź┐ź┐źżźļĪ╩ź┴ź├źūźņź├ź╚Ī╦ż“×æļ]ż╣żļĪŻźŪĪ╝ź┐ź╗ź¾ź┐Ī╝Ė■ż▒ż╦żŽGranite Rapids×æēäż“├ō┴TżĘżŲżżżļĪŻ

Intel 4żŪżŽEUVż“╗╚ż├żŲżżż»ĪŻIntelżŽASMLż╚żŽ─╣żż┤ųĪóČ”Ų▒żŪ│½╚»żĘżŲżŁż┐ż╚żżż”╬“╗╦ż¼żóżļż╚żĘżŲĪóEUVź▐ź╣ź»×æļ]ż╬ź╔źżź─IMS nanofabrication╝ęż╚żŌ▐kĮ’ż╦żõż├żŲżŁż┐ĪŻż│żņż½żķż╬EUVźčĪ╝ź╚ź╩Ī╝ż╚żĘżŲĪóApplied MaterialsĪó┼ņ»Bź©źņź»ź╚źĒź¾ĪóLam Researchż╬ć@ØiżŌæųż▓ż┐ĪŻEUVż╬└ĶżŽ╣ŌNAČ\Įčż“╗╚ż”EUVż╦ż╩żļż╚Ė½żļĪŻ

Intel 3żŽ2023ŃQŗī2╗═╚Š┤³żŪż╬╝┬ĖĮż“ų`╗žżĘĪóź╚źķź¾źĖź╣ź┐ż╬└Łē”/WżŽ18%Ė■æųż╣żļż╚żżż”ĪŻ╣Ō└Łē”źķźżźųźķźĻżõź╔źķźżźų┼┼╬«ż╬╗\▓├ĪóŪ█└■źßź┐źļź╣ź┐ź├ź»ż╬║Ū┼¼▓ĮĪóEUVźĻźĮź░źķźšźŻż╬ŠW├ō╗\äėż╩ż╔ż╬Č\Įčż“╗╚ż”ĪŻ

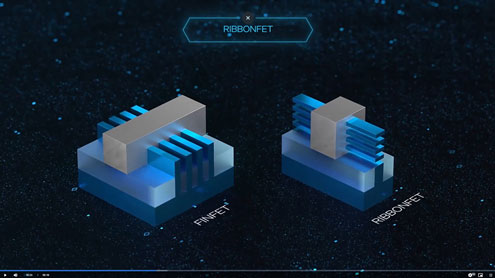

┐▐2ĪĪź▓Ī╝ź╚ź¬Ī╝źļźóźķź”ź¾ź╔╣Įļ]ż╬Ribbon FETČ\ĮčĪĪĮąųZĪ¦Intel Corp.

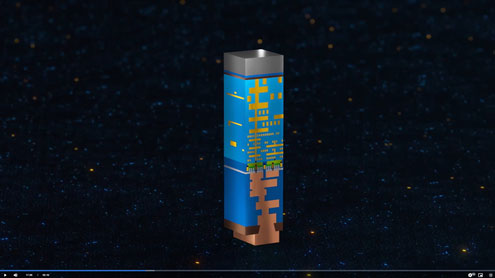

TSMCż╦╝{żżż─ż»ż╬żŽIntel 20Aż½żķż└ĪŻż│ż│żŪż╬20AżŽ20ó“Ī╩ź¬ź¾ź░ź╣ź╚źĒĪ╝źÓĪ╦ź╬Ī╝ź╔ż“┐ā║Čż╣żļź═Ī╝ź▀ź¾ź░ż╚ż╩ż├żŲżżżļĪŻż│ż╬ź╬Ī╝ź╔żŪżŽĪóź▓Ī╝ź╚ź¬Ī╝źļźóźķź”ź¾ź╔╣Įļ]ż╬Ribbon FETź╚źķź¾źĖź╣ź┐źóĪ╝źŁźŲź»ź┴źŃĪ╩┐▐2Ī╦ż╚ĪóPowerViaż╚Ō}żų┐ʿʿżŪžĀC┼┼Ė╗źķźżź¾ż“╗╚ż”źčź’Ī╝źŪźĻźąźĻĪ╝ź═ź├ź╚ź’Ī╝ź»(┐▐3)ż“╗╚ż”ĪŻż│żņżķż╬┐ĘČ\Į迎Īó90nmżŪż╬Ž─źĘźĻź│ź¾Īó45nmżŪż╬źŽźżKźßź┐źļź▓Ī╝ź╚Īó22nmżŪż╬FinFETĪó10nmżŪż╬SuperFinFETČ\Įčż╦¶öż»Īó┐ĘźŲź»ź╬źĒźĖĪ╝ż╚ż╩żļż╚żżż”ĪŻ

┐▐3ĪĪ┼┼Ė╗źķźżź¾ż“ź╚źķź¾źĖź╣ź┐ż╬▓╝Ŗõż╦╣Į└«ż╣żļPowerViaČ\ĮčĪĪ┐«ęÄźķźżź¾żŽź╚źķź¾źĖź╣ź┐żĶżĻæųż╬¾H┴žŪ█└■┴žż╦Ę┴└«ż╣żļĪĪĮąųZĪ¦Intel Corp.

PowerViaČ\Į迎ź╚źķź¾źĖź╣ź┐ż╬▓╝Ŗõż╬źąźļź»Ŗõż╦┼┼Ė╗źķźżź¾ź═ź├ź╚ź’Ī╝ź»ż“╣Į└«żĘĪó┐«ęÄźķźżź¾żŽĪóź╚źķź¾źĖź╣ź┐ż╬æųŖõż╦¾H┴žŪ█└■ż╚żĘżŲ╣Į└«ż╣żļČ\ĮčżŪżóżļĪŻ2024ŃQż╦żŽIntel 20Aź╬Ī╝ź╔ż“×óż©Īó2025ŃQĮķżßż╦żŽIntel 18Aż“│½╚»ż╣żļż╚żżż”╝Ŗ▓Ķż└ĪŻ

IntelżŽĪóźčź├ź▒Ī╝źĖź¾ź░Č\Įčż╦ż¬żżżŲżŌż│żņż▐żŪżŽ╩┐ĀCæųż╬ź┴ź├źūŲ▒╗╬ż“Š«żĄż╩║ŲŪ█└■ź┴ź├źūżŪ└▄¶öż╣żļEMIBĪ╩źżĪ╝ź▀źųż╚╚»▓╗Ī╦Č\ĮčżõĪóź┴ź├źūż“TSVĪ╩Through Silicon ViaĪ╦żŪź╣ź┐ź├ź»ż╣żļ3D-IC ż╬FoverosĪ╩źšźĪź┘źĒź╣ż╚╚»▓╗Ī╦Č\Įčż“┐āżĘżŲżŁż┐ĪŻØŖż╦FoverosČ\Įčż“EMIBż╚┴╚ż▀╣ńż’ż╗żŲ▓ŻöĄĖ■ż╦·t│½ż╣żļFoveros OmniĪ󿥿ķż╦żŽźŽź¾ź└ź▄Ī╝źļżŪżŽż╩ż»Ų╝źįźķĪ╝Ų▒╗╬żŪź┴ź├źū┤ųż“└▄¶öżĘżŲżżż»3D-ICż╬Foveros DirectČ\Įčż╩ż╔żžż╚╚»·tżĄż╗żļ╝Ŗ▓Ķż└ĪŻSapphire Rapids×æēäżŪżŽźņź┴ź»źļźĄźżź║ż╬2Ū▄ż╬ź┴ź├źūż╚ż╩żļż¼ĪóEMIBż╬īÖ├ōżŪ║YØŹźčź├ź▒Ī╝źĖ×æēäż╚╚µż┘Īóźąź¾ź╔╔²ż¼2Ū▄Īó┼┼╬üĖ·╬©żŽ4Ū▄ż╚ż╩żļ╝Ŗ▓Ķż└ĪŻ

┴└żżżŽż│żņż▐żŪż╬TSVż╦żĶżļź┴ź├źūź┌ź═źļźŲźŻż“║ŪŠ«Ė┬ż╦ż╣żļż╚ż╚żŌż╦Īó┼┼Ė╗źķźżź¾żŌżĄż▐żČż▐ż╩┬ō┘I╗Ķż“├ō┴Tż╣żļż│ż╚ż└ĪŻż▐ż┐Foveros DirectżŪżŽŲ╝źįźķĪ╝ż╬I/Oźįź├ź┴ż“25µmż╚╚∙║┘▓ĮżĘĪóźąź¾źū╠®┼┘ż“10k└▄¶ö/mm2żžż╚æųż▓źąź¾ź╔╔²ż╬╣ŁżżŪ█└■ż“×æļ]żŪżŁżļżĶż”ż╦ż╣żļĪŻż│żņżķżŽ2023ŃQż▐żŪż╦źßź╔ż“ż─ż▒ĪóźžźŲźĒźūźĒź╗ź├źĄż╬ĮĖ└čżõĄĪē”źųźĒź├ź»źņź┘źļż╬źčĪ╝źŲźŻźĘźńź╦ź¾ź░ż“▓─ē”ż╦żĘżŲżżż»ĪŻLetiżõimecĪóIBMż╚źčź├ź▒Ī╝źĖżŪżŌČ”Ų▒│½╚»ż“╣įż├żŲż¬żĻĪóĮø═Ķżžż╬·t│½ż╦śO┐«ż“Ęeż├żŲżżżļĪŻ

Intelż╬IDM 2.0żŽśOżķżŌźšźĪź”ź¾ź╔źĻźĄĪ╝źėź╣ż“─¾ČĪż╣żļż╚żĘżŲżżżļż¼ĪóLab to Fabż╬źčźżźūźķźżź¾Īóż╣ż╩ż’ż┴źšźĪź”ź¾ź╔źĻźĄĪ╝źėź╣IFSĪ╩Intel Foundry ServiceĪ╦ż“ä▌╣±ż╚▓żä”ż╦·t│½ż╣żļĪŻäŅ║▀Ė▄ĄężŽ100╝ęż“«Ćż©żŲżżżļż¼Īó║ŻövżŽ2╝ęż“Šę▓żĘż┐ĪŻ

IFSżŪ║ŪĮķż╬Ė▄ĄężŽAWSĪ╩źóź▐źŠź¾ź”ź¦źųźĄĪ╝źėź╣Ī╦ż└ż╚żżż”ĪŻż│ż│żŪżŽźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╬źżź¾źšźķĖ■ż▒ż╬źčź├ź▒Ī╝źĖźĮźĻźÕĪ╝źĘźńź¾żŪ─¾ČĪż╣żļż╚żżż”ĪŻAWSżŽż╣żŪż╦śOØiż╬ź┴ź├źūGraviton IIż“╗╚ż├żŲż¬żĻĪóIntelż╚ż╬ź│źķź▄ź┴ź├źūżŽżĮż╬╝Īż╬×æēäżŪżŽż╩żżż½ż╚ż▀żķżņżļĪŻ

ż▐ż┐Īóć@Øiż“ĮążĘżŲżŌ╬╔żżĖ▄Ąęż╚żĘżŲQualcommżŌæųż▓ż┐ĪŻQualcommż╬CEOżŪżóżļCristiano AmanĢ■ż¼ĪųIntel 20Aż╬RibbonFETż╚PowerViaČ\Įčż╦ź’ź»ź’ź»żĘżŲżżżļĪūż╚Įęż┘ż┐ź│źßź¾ź╚ż“╚õŽ¬żĘż┐ĪŻAmonĢ■żŽä▌╣±ż╦ż¬żżżŲ└Ķ├╝źšźĪź”ź¾ź╔źĻż“╗╚ż©żļż│ż╚ż“┤Ņż¾żŪżżżļż╚żĘż┐ĪŻQualcommżŽĪóźŌźąźżźļź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╬źūźķź├ź╚źšź®Ī╝źÓż“Intelż╚Č”Ų▒żŪÖ┌ŠÅż╣żļż│ż╚ż╦ż╩żĻżĮż”ż└ĪŻ

GelsingerĢ■żŽĪó║Żż╬ż╚ż│żĒ2╝ęż╬ć@ØiżĘż½Įąż╗ż╩żżż¼ĪóŠÅČ╚├ōż╚śOŲ░┘Z├ōż╬╚ŠŲ│öüżŪÅBżĘ╣ńżż├µż└ż╚Įęż┘żŲżżżļĪŻ2024ŃQż╦żŽTSMCż╦╝{żżż─żŁĪó2025ŃQż╦żŽźšźĪź”ź¾ź╔źĻż╬źĻĪ╝ź└Ī╝ż╦żŌż╩żļż╚┴T═▀┼¬ż└ĪŻź¬ź¾źķźżź¾▓±Ė½żŪżŽĪóźčź├ź▒Ī╝źĖź¾ź░żõźūźĒź╗ź╣ż╬└šŪżŪvżŌ┼ąŠņżĘżŲż¬żĻĪóżżż║żņżŌśO┐«ż╦╦■ż┴ż┐╚»Ė└ż“╣įż├żŲżżżļĪŻ

╗▓╣═½@╬┴

1.ĪųIntelż╬200▓»ź╔źļ┼Ļ½@żŽĪó×æļ]╬üäė▓Įż╬▀Mż╬Ė²ĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2021/03/25)

2. ĪųIntelż╬11└ż┬ÕźūźĒź╗ź├źĄĪó╚∙║┘▓ĮżĶżĻżŌFinFETż╚¾H┴žŪ█└■ż╦╣®╔ūĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2020/09/04)