65nmż╬╝ĪżŽ28nmźŪźČźżź¾ż“┐õ┐╩ż╣żļźķźŲźŻź╣ĪóŲ³╦▄ż╬źšźĪź”ź¾ź╔źĻżŽ▌xŠņ┴ė╝║

ä▌źķźŲźŻź╣ź╗ź▀ź│ź¾ź└ź»ź┐Ī╝Ī╩Lattice SemiconductorĪ╦╝꿎ĪóĖĮ║▀╝ń╬«ż╬65nmźūźĒź╗ź╣×æēäżŪ╔┘╗╬─╠ż╚ź╗źżź│Ī╝ź©źūźĮź¾ż“źšźĪź”ź¾ź╔źĻż╚żĘżŲ╗╚ż├żŲżżżļż¼Īó╝ĪżŽ45nm/32nmż“ź╣źŁź├źūżĘżŲżżżŁż╩żĻ28nmźūźĒź╗ź╣żžż╚Ė■ż½ż”ż│ż╚ż“£½żķż½ż╦żĘż┐ĪŻŲ³╦▄ż╬╚ŠŲ│öüźßĪ╝ź½Ī╝żŽ28nmż“│½╚»żĘżŲżżż╩żżż┐żßĪóźšźĪź”ź¾ź╔źĻż╚żĘżŲż╬Ė▄Ąęż“╝║ż”ż│ż╚ż╦ż╩żļĪŻ

┐▐1ĪĪźķźŲźŻź╣ż╬×æēäż“┴ßż»Įą▓┘ż╣żļ╗┼┴╚ż▀ĪĪĮąųZĪ¦Lattice Semiconductor

źķźŲźŻź╣ż¼źĒĪ╝ź©ź¾ź╔ż╚ź▀ź├ź╔źņź¾źĖż╬FPGA▌xŠņżžŠĶżĻĮąż╣ż│ż╚żŽż╣żŪż╦┼┴ż©ż┐ż¼Ī╩╗▓╣═½@╬┴1)Īóź▀ź├ź╔źņź¾źĖżŪżŽżõżŽżĻ╚∙║┘źčź┐Ī╝ź¾ż“╗╚żżĪó╣Ō└Łē”Ī”─ŃŠ├õJ┼┼╬üż╬─Ńź│ź╣ź╚×æēäż“║Ņżļż┐żßż╬28nmźūźĒź╗ź╣ż“źķźŲźŻź╣żŽĄßżßżŲżżżļĪŻŲ▒╝ęCEOż╬Darin BillerbeckĢ■żŽĪóĪųĖĮ║▀Īó└ż─cżŪżŽźšźĪź”ź¾ź╔źĻ3╝ęż¼28nmźūźĒź╗ź╣ż“│½╚»żĘżŲżżżļĪŻ»éżßŠ}ż╚ż╩żļż╬żŽź│ź╣ź╚żŪżóżĻĪóÖ┌ŠÅżŪżŁżļż╚żżż”ź│ź▀ź├ź╚źßź¾ź╚żŪżóżļĪŻżĮżņż“╝┬ĖĮżŪżŁżļźšźĪź”ź¾ź╔źĻż“┬ō(li©ón)żųĪūż╚Ė└ż”ĪŻźšźĪźųźņź╣ż└ż½żķż│żĮż╬äėż▀ż¼ż│ż│ż╦żóżļĪŻĖĮ║▀ż╬65nm└▀╝Ŗż╬╬╠ŠÅź┴Ī╝źÓż╚żŽ╩╠ż╦Īó28nm└▀╝Ŗż╬ż┐żßż╬R&Dź┴Ī╝źÓż¼ż╣żŪż╦żżżļĪŻ

źżź¾źŲźļĪóźČźżźĒź░ż“ĘążŲ║“ŃQ┼×ŪżżĘż┐CEOż╬Darin BillerbeckĢ■ż¼╬©żżżļ┐ĘÖ┌źķźŲźŻź╣ż¼ØŖ─╣ż╚ż╣żļż╬żŽĪó│ū┐Ę┼¬ż╩┐Ę×æēäż“ż╔ż│żĶżĻżŌ┴ßż»Įąż╣ż│ż╚ĪŻ5ĘŅ24Ų³ż╬ĄŁŪv▓±Ė½ż╬├µżŪĪóBillerbeckĢ■żŽ▓┐┼┘żŌĪųGo fastĪūżóżļżżżŽĪųRun fastĪūż╚żżż”Ė└±äż“╗╚ż├ż┐ĪŻżĮż╬ż┐żßż╦IPż“?q©▒)Ö├ōżĘFPGAżĮż╬żŌż╬ż½żķSoC┼¬ż╩źóźūźĒĪ╝ź┴ż“┐╩żßżŲżżż»ĪŻØŖż╦FPGAż╬źėźļźŪźŻź¾ź░źųźĒź├ź»ż“┐õżĘ┐╩żßżļ└’ŠSż└ĪŻIPźķźżźųźķźĻż“śO╝ę│½╚»żĘĪóIPż╬├µżŪżŌźżź¾ź┐Ī╝źšź¦Ī╝ź╣╝■żĻż╬PCIeżõUSB3.0ż╬żĶż”ż╩źżź¾ź┐Ī╝źšź¦Ī╝ź╣IPż“┬Ęż©żŲżżż»ĪŻFPGAż└ż▒żŪżóżņżą└▀╝ŖżõźĮźšź╚ź”ź©źóż╬║ŲŠW(w©Żng)├ōżŽžMżĘżżż¼ĪóIPżõźėźļźŪźŻź¾ź░źųźĒź├ź»öĄ(sh©┤)╝░ż╩żķ║ŲŠW(w©Żng)├ōżĘżõż╣ż»ż╩żļż┐żßĪóFPGAż½żķSoCż╬Š}╦Īż╦ō¶żŲż»żļż╬żŪżóżļĪŻ└▀╝Ŗż╬║ŲŠW(w©Żng)├ōĪóIPż╬║ŲŠW(w©Żng)├ōż“żĶżĻ┐╩żßżŲżżżŁĪó┴ßż»Įą▓┘żŪżŁżļżĶż”ż╦ż╣żļĪŻ

┐▐2ĪĪ3D IC▓Įż“FPGAźßĪ╝ź½Ī╝ż╬├µżŪ└ĶŲ¼żŪ┐╩żßżļĪĪĮąųZĪ¦Lattice Semiconductor

źčź├ź▒Ī╝źĖČ\ĮčżŪżŽźŽźżź©ź¾ź╔┴└żżż╬Įj(lu©░)Š}FPGAźßĪ╝ź½Ī╝żĶżĻżŌźĻĪ╝ź╔żĘżŲżżżļż╚żżż”ĪŻ3╝ĪĖĄICżŪżŽĪó╬╔ēä (KGD: knowngood die)ż“Ęeż─ż│ż╚ż¼─Ńź│ź╣ź╚ż╦żŽź▐ź╣ź╚ż╚ż╩żļż╚BillerbeckĢ■żŽĖ└ż”ĪŻż╣żŪż╦FPGAźßĪ╝ź½Ī╝ż╚żĘżŲź╣ź┐ź├ź»Ī▄ź’źżźõĪ╝ź▄ź¾źŪźŻź¾ź░ż╦żĶżļ3╝ĪĖĄ ICż“Ęeż├żŲżżżļż╚śO╦²ż╣żļĪŻFPGAĮj(lu©░)Š}2╝꿎ź┴ź├źūż“▓Żż╦╩┬ż┘żļī¦(d©Żo)ō¶3╝ĪĖĄżóżļżżżŽ2.5╝ĪĖĄICżĘż½Ęeż├żŲżżż╩żżż╚żżż”ĪŻ║ŻĖÕżŽź╣ź┐ź├ź»ż“żĄżķż╦╗\żõżĘĪó─Ńź│ź╣ź╚▓ĮŠ«Ę┐▓Įż“┐╩żßżŲżżż»ĪŻ

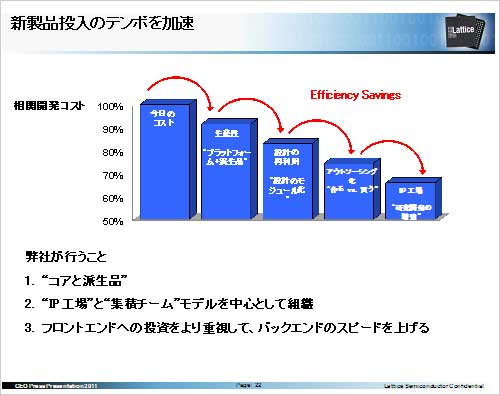

┐▐3ĪĪźķźŲźŻź╣ż╬źūźķź├ź╚źšź®Ī╝źÓ└’ŠSżŪź│ź╣ź╚ż“║’žōĪĪĮąųZĪ¦Lattice Semiconductor

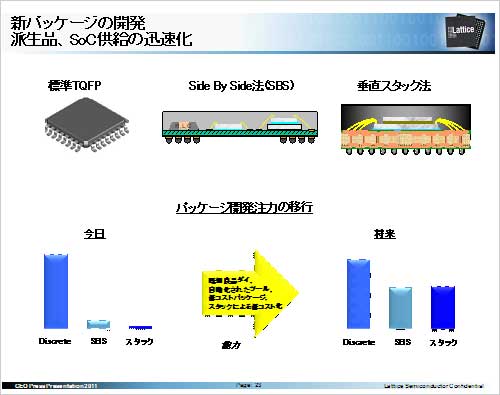

Ų▒╝꿎×æēäż╬źĘźĻĪ╝ź║ż“┬Ęż©żŲżżżļż└ż▒żŪżŽż╩żżĪŻźūźķź├ź╚źšź®Ī╝źÓź▐ź═Ī╝źĖźŃĪ╝ż╚Ō}żų2ź┴ź├źūČ\Įčż“Ęeż┴Īóźóź╩źĒź░ż╬źčź’Ī╝ź▐ź═Ī╝źĖźßź¾ź╚ICż╚ĪóFPGAż╬źŪźĖź┐źļź┴ź├źūż“1źčź├ź▒Ī╝źĖŲŌż╦╝²żßżŲżżżļĪŻź╬źżź║ż╬╠õ¼öż╩ż╔ż“ķcż▒Īóźčź’Ī╝ź▐ź═Ī╝źĖźßź¾ź╚ICż╚żĘżŲżŌ├▒ż╩żļDC-DCź│ź¾źąĪ╝ź┐ż└ż▒żŪżŽż╩ż»Īóź█ź├ź╚ź╣ź’ź├źūöUĖµżõĪó┼┼Ė╗ż╬źĘĪ╝ź▒ź¾ź╣öUĖµĪó┼┼░ĄźŌź╦ź┐źĻź¾ź░ż╩ż╔ż╬ĄĪē”żŌĘeż├żŲżżżļĪŻż│ż╬źūźķź├ź╚źšź®Ī╝źÓź▐ź═Ī╝źĖźŃĪ╝Č\Įčż¼2ź┴ź├źūźĮźĻźÕĪ╝źĘźńź¾ż“ܦż©żŲżżżļĪŻż│ż”żżż├ż┐└▀╝ŖŠ}╦ĪĪóźčź├ź▒Ī╝źĖź¾ź░Īóźūźķź├ź╚źšź®Ī╝źÓż╚żżż├ż┐Č\Įčż“┐õ┐╩ż╣żļż╬żŽźżź¾źŲźļż½żķ╗▓▓├żĘż┐ź┘źŲźķź¾ż╬ź©ź¾źĖź╦źóż┐ż┴ż└ż╚żżż”ĪŻ

║ŪĖÕż╦Īó║ŪŖZÅRų`ż“ĮĖżßżŲżżżļTabula╝ęż╦ż─żżżŲż┐ż║ż═żŲż▀żļż╚ĪóĪųĪ╩Ų▒╝ęż╬Ī╦Č\Įčż╦┤ž┐┤żŽżóżļżŌż╬ż╬ĪóĒö┴Ķ┴ĻŠ}żŽźČźżźĻź¾ź»ź╣żõźóźļźŲźķżŪżóżĻĪó┼÷╝ężŪżŽż╩żżĪūż╚żĘżŲĪóźĒĪ╝ź©ź¾ź╔Īóź▀ź├ź╔źņź¾źĖż╦ĮĖ├µż╣żļźķźŲźŻź╣ż╚żŽ└’ŠSż╬░Ńżżż¼£½│╬ż╦ĮążŲżżżļĪŻ

╗▓╣═½@╬┴

1. 2Č╦▓Įż╣żļFPGAČ╚─cĪó─Ń┼┼╬üĪóŠ«æä╠Ž▌xŠņż╦źķźŲźŻź╣żõźĘźĻź│ź¾źųźļĪ╝ż¼īÖ╠÷ (2011/04/28)