Intelź▐źņĪ╝źĘźóĖ½│žĄŁ(5)Ī¦CPUźŲź╣ź┐Ī╝żŽĖÕ╣®µć╣®ŠņżŪŲŌ×æżĄżņżŲżżż┐Ī¬

Intelź▐źņĪ╝źĘźóŗī2övż╚ŗī3övĪ╩╗▓╣═½@╬┴1Īó2Ī╦żŪCPUźŲź╣ź┐Ī╝ż“żżż»ż─ż½Šę▓żĘż┐ż¼Īóż│żņżķż╬źŲź╣ź┐Ī╝żõźŲź╣ź╚├ōź▐źČĪ╝ź▄Ī╝ź╔żŽĪóĄĪ╠®ŃŖ▒╠╦╔┘Vż╬ż┐żßĪóIntelź▐źņĪ╝źĘźóĖÕ╣®µć╣®ŠņżŪŲŌ×æżĄżņżŲżżż┐ĪŻIntelź▐źņĪ╝źĘźóĖ½│žĄŁż╬║ŪĮ¬övż╚ż╩żļ║ŻövżŽĪóCPUźŲź╣ź┐Ī╝ż╬×æļ]ż╬══╗ęż“└^┐┐żŪŠę▓żĘżĶż”ĪŻ║ŪĖÕż╦Ī󿬿▐ż▒żŪź┘Ī╝źļż╦╩±ż▐żņżŲżżżļ╔į╬╔▓“└Žźķź▄ż╦ż─żżżŲżŌŠę▓ż╣żļĪŻ

(1)CPUźŲź╣ź┐Ī╝ż¬żĶżėźŲź╣ź╚├ōź▐źČĪ╝ź▄Ī╝ź╔×æļ]

ź▐źņĪ╝źĘźóż╬ź┌ź╩ź¾ćŖż╬×┤┤▀ż╬ź▐źņĪ╝╚ŠćŖż╦żóżļź»źĻźÓĪ”źŁźŃź¾źčź╣ż╦żŽĪóźĘź╣źŲźÓźżź¾źŲź░źņĪ╝źĘźńź¾&ź▐ź╦źÕźšźĪź»ź┴źŃźĻź¾ź░źĄĪ╝źėź╣Ī╩SIMSĪ╦ż╚Ō}żążņżļĄ£Č╚ŗ╠ńż¼Ų▒Ą’żĘżŲż¬żĻĪóSMT(╔ĮĀC╝┬äóČ\Įč)ż╚żżż”źūźĻź¾ź╚┤łż╦┼┼╗ęŗēäż“╔ĮĀC╝┬äóż╣żļäóÅøż¼╩┬ż¾żŪĪóIntelż╬CPUżõGPUż╩ż╔ż╬║ŪĮ¬źŲź╣ź╚╗■ż╦ØŁ═ūż╩ź▐źČĪ╝ź▄Ī╝ź╔ż¬żĶżėż│żņżķż“┼ļ║▄żĘż┐źŲź╣ź╚źĘź╣źŲźÓż“ź▐źņĪ╝źĘźó╣®ŠņŲŌŗżŪ×æļ]żĘżŲżżż┐ĪŻSIMSżŪżŽĪóźūźņĪ”źĘźĻź│ź¾Ė■ż▒ż╬źĘź▀źÕźņĪ╝ź┐├ō┤łżŌ×æļ]żĄżņĪóä▌(sh©¼)╣±żŽżĖżß└ż─c├µż╬CPUż╬│½╚»Ą“┼└ż╦─¾ČĪżĄżņżŲżżżļż╚żżż”ĪŻCPUźŲź╣ź┐Ī╝żõżĮż╬ż┐żßż╬ź▐źČĪ╝ź▄Ī╝ź╔ż“ź▐źņĪ╝źĘźó╣®ŠņżŪŲŌ×æż╣żļż╬żŽIntel╝ę│░ż╦×æēäż╬╚ļ╠®ż¼ŃŖ▒╠żĘż╩żżż┐żßż└ż╚żżż”ĪŻ

(1-1) High Density Modular Tester

║ŪĮķż╦ĪóCPUź┴ź├źūż╬źĘź╣źŲźÓźņź┘źļźŲź╣ź╚ż“╣įż”ż┐żßż╬ĪųHigh Density ModularĪĪTesterĪ╩HDMTĪ╦Īūż╬×æļ]ĖĮŠņż“Šę▓żĘżĶż”ĪŻż│żņżŽCPUż╬┤╦▄└Łē”ż“źŲź╣ź╚ż╣żļäóÅøżŪżóżļĪŻ

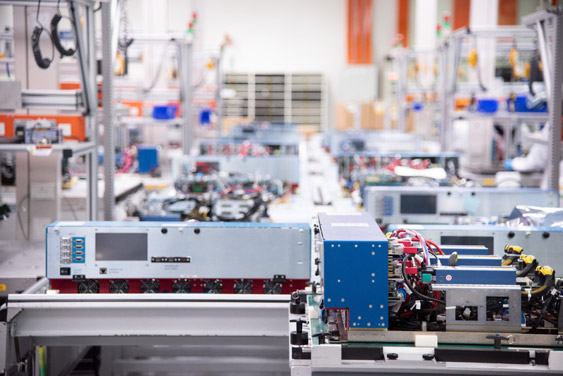

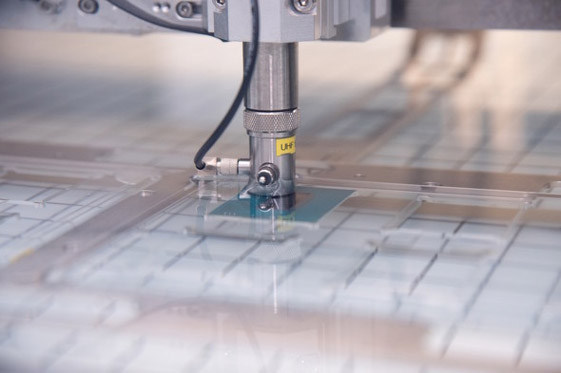

┐▐1ĪĪźŲź╣ź┐Ī╝├ōź▐źČĪ╝ź▄Ī╝ź╔Ī╩╗Ņ║Ņ├╩│¼Ī╦żžŠ}║ŅČ╚żŪ┼┼╗ęŗēäż╬äóŠÆż¬żĶżėĖĪØhĪĪĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ

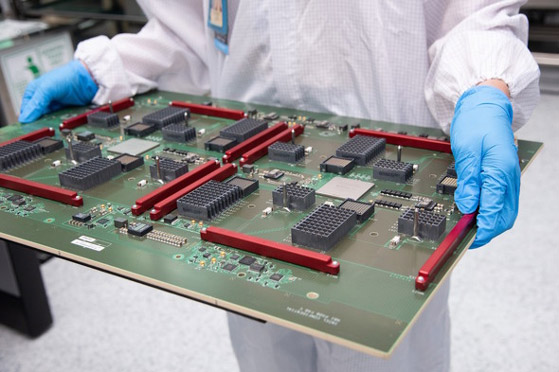

┐▐2ĪĪźŲź╣ź┐Ī╝├ōź▐źČĪ╝ź▄Ī╝ź╔Ī╩╗Ņ║ŅēäĪ╦ż╬┼┼Ąż┼¬ØŖ└Łź┴ź¦ź├ź»ĪĪĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ

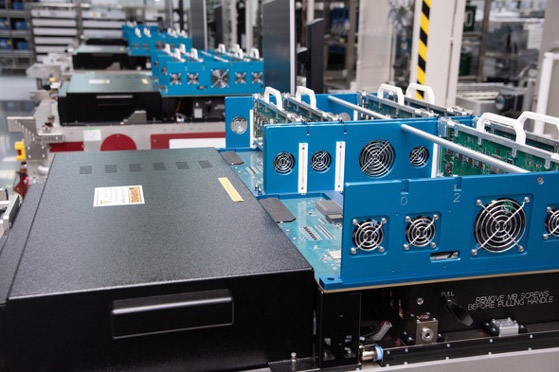

┐▐3ĪĪHigh Density Modular Testerż╬┴╚ż▀╬®żŲĖĮŠņĪĪĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ

┐▐4ĪĪHDMTż“4├╩└čż▀æųż▓żŲŲ░║Ņ│╬Ū¦├µĪĪĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ

(1-2) System Level Tester

System Level TesterżŽĪó│░¤²ż▒GPUĪóSSDż╩ż╔ż╬ź╣ź╚źņĪ╝źĖźŪźąźżź╣ĪóUSBż╩ż╔ż╬ĘQ¹|╝■╩šĄĪ▀_(d©ó)ż╚ż╬ŽóĘ╚Ų░║Ņż“ĪóWindowsż╩ż╔ż╬╝┬║▀OSżŪż╬Ų░║Ņ▓╝żŪ╝┬║▌ż╬ź│ź¾źįźÕĪ╝ź┐×æēäż╦╝²ż▐ż├ż┐ėX(ju©”)▌åż╚Č╦żßżŲŖZżżėX(ju©”)▌åżŪŲ░║Ņ╗Ņ┘xż“╣įż”║ŪĮ¬├╩│¼ż╬źŲź╣ź┐Ī╝żŪżóżļĪŻ

┐▐5ĪĪSLT│░ćĶĪĪĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ

![┐▐6ĪĪ╬«żņ║ŅČ╚ż╬źŲź╣ź┐Ī╝╬╠ŠÅ×æļ]ĪĪĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ](/archive/blog/insiders/hattori/img/20231115-Intel_penang_campus6.jpg)

┐▐6ĪĪ╬«żņ║ŅČ╚ż╬źŲź╣ź┐Ī╝╬╠ŠÅ×æļ]ĪĪĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ

(1-3) High Density Burn-InĪ╩HDBIĪ╦Tester

High Density Burn-InĪ╩HDBIĪ╦TesterżŽĪó┤░└«żĘż┐CPUź┴ź├źūż“╝┬║▌ż╦─Ńča(b©│)Ī┐╣Ōča(b©│)ėX(ju©”)▌åż╦żĘż┐żĻĪó─Ļ│╩żĶżĻżŌ╣Ōżż┼┼░Ąż“²Xż▒ż┐żĻżĘżŲĪó┤╦▄Ų░║Ņ╗Ņ┘xż“╣įż”ż┐żßż╦╗╚ż’żņżļźŲź╣ź┐Ī╝żŪżóżļĪŻ1±śż╬äóÅøżŪ╩Ż┐¶ż╬CPUż“╩┬╣įżĘżŲźŲź╣ź╚żŪżŁżļżĶż”ż╦ż╩ż├żŲżżżļĪŻ

┐▐7ĪĪHigh Density Burn-InĪ╩HDBIĪ╦Tester│░ćĶĪĪ ĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ

┐▐8ĪĪHDBIźŲź╣ź┐Ī╝├ōź▐źČĪ╝ź▄Ī╝ź╔Ī¦Ė³ż»żŲ─_ż»żŲ┬čÕXĪĪĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ

┐▐9ĪĪHDBIźŲź╣ź┐Ī╝Ö┌ŠÅĖĮŠņĪĪĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ

(2) ╔į╬╔▓“└Žźķź▄

ź┌ź╩ź¾źŁźŃź¾źčź╣ż╦żŽ╔į╬╔▓“└Žźķź▄ż¼żóżĻĪóźŲź╣ź┐Ī╝żŪ╔į╬╔ż╚ż╩ż├ż┐CPUź┴ź├źūż╬╔į╬╔ĖČ░°╝{Ą┌║ŅČ╚ż¼╣įż’żņżŲżżż┐ĪŻź”ź¦Ī╝źŽźņź┘źļż╬╔į╬╔▓“└ŽżŌ╣įż├żŲż¬żĻĪó╔į╬╔▓“└ŽŠ╩¾żŽä▌(sh©¼)╣±ź¬źņź┤ź¾ä”ż╬│½╚»Ī”╗Ņ║Ņź┴Ī╝źÓż╦źšźŻĪ╝ź╔źąź├ź»żĄżņżļĪŻ

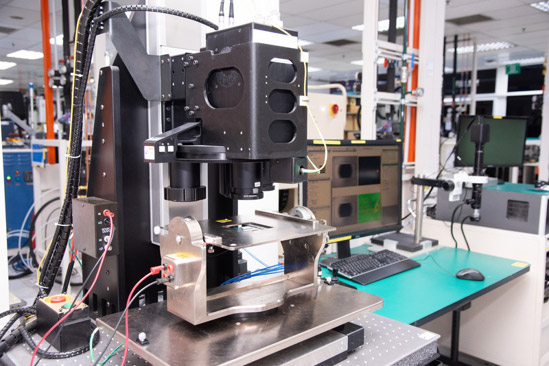

┐▐10ĪĪ╔į╬╔▓“└Ž║ŅČ╚ĪĪĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ

┐▐11ĪĪ╔į╬╔ź┴ź├źū╔ĮĀCż╬ča(b©│)┼┘╩¼╔█ż“ćĶ╗Īż╣żļż┐żßż╬╝■āS┐¶źĒź├ź»źżź¾Ī”źĄĪ╝źŌź░źķźšźŻĪĪ╝■āS┐¶ż“╔w─ĻżĘżŲča(b©│)┼┘╩¼╔█ż“▒R─ĻżŪżŁżļżĶż”ż╦ż╩ż├żŲżżżļĪĪĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ

┐▐12ĪĪ╔į╬╔CPUź┴ź├źūż╬ŲŌŗż╬┤┘ż“ĖĪĮąż╣żļ«Ć▓╗āSĖ▓╚∙¬Ü(d©▓)ĪĪĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ

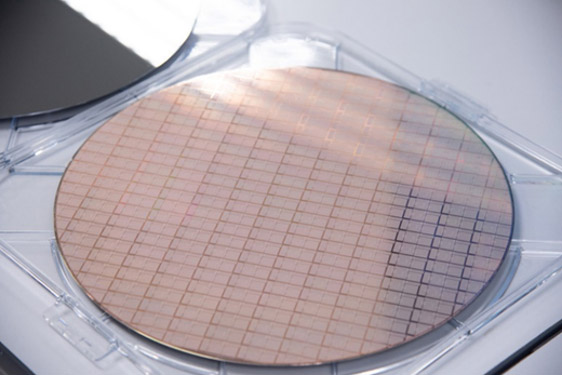

┐▐13ĪĪ╔į╬╔▓“└Žż“┬įż─300mmźĘźĻź│ź¾ź”ź¦Ī╝źŽĪ©Core UltraźūźĒź╗ź├źĄĪ╩│½╚»ź│Ī╝ź╔Ī¦Meteor LakeĪ╦ż╬ź▐źČĪ╝ź”ź¦Ī╝źŽĪ╩ź┴ź├źūźņź├ź╚ż“┼ļ║▄ż╣żļż┐żßż╬Ū█└■├ōźĘźĻź│ź¾┤łĪ╦ż╚╗ūż’żņżļĪĪĮąųZĪ¦Intelź▐źņĪ╝źĘźó╣®Šņ

Intelż¼Īóź┘Ī╝źļż╦╩±ż▐żņżŲżżż┐ĖÕ╣®µć╣®Šņż“ż│ż│ż▐żŪPC┤žŽóźßźŪźŻźóż╦Įo│½żĘż┐ż╬żŽĮķżßżŲż╬ż│ż╚ż└ż╚żżż”ĪŻEUVźĻźĮź░źķźšźŻż“ĮķżßżŲ╗╚├ōżĘż┐AIĄĪē”┼ļ║▄ PC├ōCore UltraźūźĒź╗ź├źĄĪ╩12ĘŅ╚»Ūõ═Į─ĻĪ╦ż¼ż╩ż½ż╩ż½╚»╔ĮżĄżņż║ĪóŃQŲŌ╚»Ūõż“Õe(cu©░)żųżÓ╠mż¼æųż¼ż├żŲżżż┐ż¼ĪóIntelżŽĪó12ĘŅ14Ų³ż╬╚»Ūõ│½╗Žż╦Ė■ż▒żŲĮń─┤ż╦┴╚ż▀╬®żŲżķżņżŲżżżļż│ż╚ż“źóźįĪ╝źļżĘż┐ż½ż├ż┐żĶż”żŪżóżļĪŻ

╗▓╣═½@╬┴

1. └Kŗō·(d©Īn)ĪóĪųIntel║ŪĮj(lu©░)ż╬ź▐źņĪ╝źĘźóĖÕ╣®µć╣®Šņż╬ź»źĻĪ╝ź¾źļĪ╝źÓż╦Ų■ż├żŲżŁż┐!ĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2023/09/26)

2. └Kŗō·(d©Īn)ĪóĪų12ĘŅ╚»Ūõ═Į─Ļż╬Intel Core UltraźūźĒź╗ź├źĄ┴╚╬®Ī”źŲź╣ź╚ĖĮŠņż“Ė½żŲżŁż┐!ĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2023/10/11)