12ĘŅ╚»Ūõ═Į─Ļż╬Intel Core UltraźūźĒź╗ź├źĄ┴╚╬®Ī”źŲź╣ź╚ĖĮŠņż“Ė½żŲżŁż┐!

ä▌Intelż¼9ĘŅ19Ų³ż╦╚»╔ĮżĘż┐ĪóAIĄĪē”┼ļ║▄ż╬ź»źķźżźóź¾ź╚PCĖ■ż▒źūźĒź╗ź├źĄżŪżóżļCore Ultra Processorż╬ĖÕ╣®µćżŽĪóŲ▒╝ęż╬ź▐źņĪ╝źĘźó╣®ŠņżŪ╣įż’żņżŲż¬żĻĪóżĮż╬ź»źĻĪ╝ź¾źļĪ╝źÓŲŌżŪ║ŅČ╚ż╬══╗ęż¼▐kŗż╬PC┤žŽóźßźŪźŻźóż╦Įo│½żĄżņż┐ĪŻź└źżźĘź¾ź░ż╚źĮĪ╝ź╚Ī╩┬ō╩╠ĖĪØhĪ╦ż▐żŪż╬══╗꿎ØiövŠę▓żĘż┐ż╬żŪĪ╩╗▓╣═½@╬┴1Ī╦Īó║ŻövżŽĪóź┌ź╩ź¾ćŖż╦żóżļĪųPenang Assembly and TestĪūĪ╩PGATĪ╦ŗ╠ńżŪ╣įż’żņżŲżżżļĖÕ╣®µćĖÕ╚Šż╬źóź╗ź¾źųźĻż╚║ŪĮ¬źŲź╣ź╚ż“Šę▓żĘżĶż”ĪŻ

![┐▐1ĪĪIntelź▐źņĪ╝źĘźóĖÕ╣®µć╣®Šņź┌ź╩ź¾źŁźŃź¾źčź╣ż╬×æļ]╗▄└▀ĪĪĮąųZĪ¦├°Ūv╗Ż▒Ų](/archive/blog/insiders/hattori/img/20231011-Intel_penang_campus.png)

┐▐1ĪĪIntelź▐źņĪ╝źĘźóĖÕ╣®µć╣®Šņź┌ź╩ź¾źŁźŃź¾źčź╣ż╬×æļ]╗▄└▀ĪĪĮąųZĪ¦├°Ūv╗Ż▒Ų

12ĘŅ14Ų³ż╦╚»ŪõżĄżņżļCore UltraĪ╩│½╚»ź│Ī╝ź╔ć@Meteor LakeĪ╦żŽĪóź┴ź├źūźņź├ź╚żõ2.5D/3D-ICż“╗╚ż├ż┐└Ķ├╝źčź├ź▒Ī╝źĖżŪĮą═ĶżŲż¬żĻĪóż│ż╬CPUź┴ź├źūźņź├ź╚żŽĪóä▌╣±ź¬źņź┤ź¾ä”ż╬│½╚»╗Ņ║Ņźķźżź¾żŪEUVźĻźĮź░źķźšźŻż“╗╚ż├żŲ×æļ]żĄżņżŲżżżļĪŻ9ĘŅ29Ų³ż╦żŽźóźżźļźķź¾ź╔╣®ŠņżŪżŌIntel 4źūźĒź╗ź╣ź╬Ī╝ź╔żŪż╬╬╠ŠÅż“│½╗Žż╣żļ╝░ųZż“╣įż├ż┐żąż½żĻżŪżóżļ (╗▓╣═½@╬┴2)ĪŻ

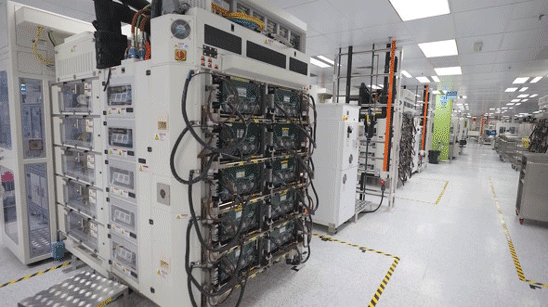

┐▐2ĪĪź┌ź╩ź¾ćŖż╦żóżļźóź╗ź¾źųźĻ├ōź»źĻĪ╝ź¾źļĪ╝źÓĪĪĮąųZĪ¦Intel

ź»źĻźÓźŁźŃź¾źčź╣żŪź└źżźĘź¾ź░ż╚źĮĪ╝ź╚ż“ĘążŲźŲź╣ź╚ż╦╣ń│╩żĘż┐ź└źżżŽ,ź┌ź╩ź¾źŁźŃź¾źčź╣ż╦┴„żķżņżŲ,źóź╗ź¾źųźĻż╚║ŪĮ¬źŲź╣ź╚ż¼╣įż’żņżļĪŻ

(1)źóź╗ź¾źųźĻ╣®µć

źóź╗ź¾źųźĻż╬║ŪĮķż╬╣®µćżŪżŽĪóź└źżż“Ń~ĄĪ█`╗ķ×æ┤łż╦║▄ż╗żŲÕXĮĶ═²żĘżŲ┼┼Ąż┼¬ż╦└▄¶öżĘż┐æųżŪ,ź└źż╝■╩šż╚┤łż╬ź└źżż╬Ęõ┤ųż“ź©ź▌źŁźĘ█`╗ķżŪä┘ż”Ī╩┐▐3Ī┴5Ī╦ĪŻż│żņż╦żĶż├żŲĪóź└źżż“żĘż├ż½żĻż╚┤łż╦╔w─Ļż╣żļż╚ż╚żŌż╦┬čÕX└ŁĪó┬č┐Õ└ŁĪó┬č╠¶ēä└ŁĪó┬čŃt└Łż“¤²▓├ż╣żļĪŻ

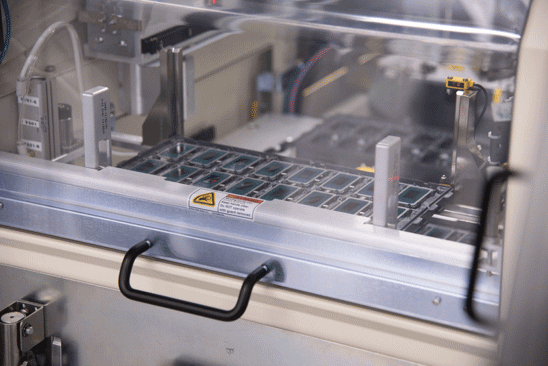

┐▐3ĪĪŃ~ĄĪ█`╗ķ┤łż╦Core UltraźūźĒź╗ź├źĄż╬ź└źżż“║▄ż╗żļäóÅøż╬ŲŌŗĪĪĮąųZĪ¦Intel

┐▐4ĪĪżĮż╬║ŅČ╚żŽśOŲ░▓ĮżĄżņżŲżżżļż¼Īóų`£åż╚ź╚źņźżż╬╚┬┴„żŽŠ}Ų░ĪĪĮąųZĪ¦Intel

┐▐5ĪĪĪ╩źŪĪ╝ź┐ź╗ź¾ź┐Ī╝Ė■ż▒XeonźūźĒź╗ź├źĄ├ōż╬Ī╦ź└źż╝■╩šż“ź©ź▌źŁźĘ█`╗ķżŪä┘ż├ż┐Ń~ĄĪ█`╗ķ┤łĪĪĮąųZĪ¦Intel

ź└źżż╬╝■╩šżžż╬ź©ź▌źŁźĘ█`╗ķż╬┼╔╔█ėX▌åż“ų`£åżŪĖĪØhżĘż┐ĖÕĪ╩┐▐6Ī╦ĪóÕX┼┴Ų│║Óż“ź└źż╔ĮĀCż╦┼╔╔█żĘżŲż½żķĪó╔ĮĀCż╦╩³ÕX├ōż╬źęĪ╝ź╚ź╣źūźņź├ź└ż“ØażĻ¤²ż▒żļż╚żżż”╣®µćżŪ┴╚ż▀╬®żŲżķżņżļĪŻż┐ż└żĘĪóMeteor Lake ż╬żĶż”ż╩ź»źķźżźóź¾ź╚PCĖ■ż▒źūźĒź╗ź├źĄż╦żŽźęĪ╝ź╚ź╣źūźņź├ź└żŽäóŠÆżĄżņż╩żżĪŻ

┐▐6ĪĪCore Ultra źūźĒź╗ź├źĄź└źżż╬╝■╩šżžż╬ź©ź▌źŁźĘ█`╗ķ┼╔╔█ėX▌åż“ų`£åĖĪØhĪĪĮąųZĪ¦Intel

(2)║ŪĮ¬źŲź╣ź╚╣®µć

┤░└«żĘż┐źūźĒź╗ź├źĄĪ╩┐▐7Ī╦żŽĪóż▐ż║źąĪ╝ź¾źżź¾źŲź╣ź╚Ī╩╣ŌčażŪż╬ĖĪØhĪ╦ż“ż¬ż│ż╩ż”ĪŻ╣ŌčażŪ─Ļ│╩żĶżĻżŌ╣Ōżż┼┼░Ąż“░§▓├żĘżŲź╣ź╚źņź╣ż“▓├ż©ż┐ėX▌åżŪ┤╦▄Ų░║Ņ╗Ņ┘xż“╣įż”Ī╩┐▐8Ī╦ĪŻżĮż╬ĖÕĪó▐kŽóż╬┼┼Ąż┼¬źŲź╣ź╚ż“╣įżżĪóCPUż╦×óż’żļ┤╦▄ĄĪē”ż¼µ£żŲ┘抒ż╦Ų░║Ņż╣żļż½ż╔ż”ż½ż“ź┴ź¦ź├ź»ż╣żļĪ╩┐▐9Ī╦ĪŻ

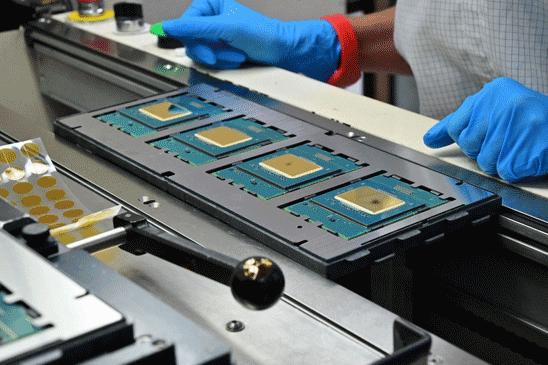

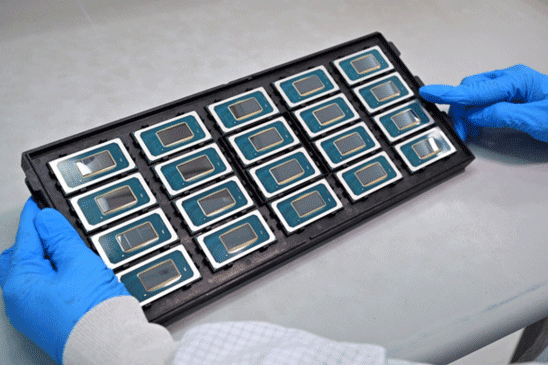

┐▐7ĪĪ┤░└«żĘż┐ź╚źņźżż╦║▄ż├ż┐20Ė─ż╬Core UltraźūźĒź╗ź├źĄĪĪĮąųZĪ¦Intel

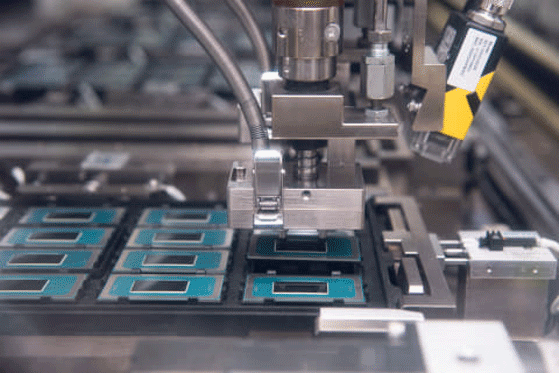

┐▐8ĪĪźĒź▄ź├ź╚ż¼ź└źżż“┼ļ║▄żĘż┐Ń~ĄĪ█`╗ķ┤łż“źąĪ╝ź¾źżź¾äóÅøĪ╩▒³ż╦░╠ÅøżĘżŲż¬żĻĖ½ż©ż╩żżĪ╦żžöĪ┴„ĪĪĮąųZĪ¦Intel

┐▐9ĪĪźŲź╣ź╚╣®µćĪĪĮąųZĪ¦Intel

żĮżĘżŲ║ŪĖÕż╦ĪóĪųPlatform Performance ValidationĪ╩PPVĪ¦źūźķź├ź╚źšź®Ī╝źÓż╚żĘżŲż╬źčźšź®Ī╝ź▐ź¾ź╣ĖĪŠ┌Ī╦Īūż“╣įż”Ī╩┐▐10Ī╦ĪŻż│ż│żŪżŽĪó╝┬║▌ż╦ź©ź¾ź╔źµĪ╝źČĪ╝ż¼╗╚ż”┤─ČŁż“„[─ĻżĘż┐źŲź╣ź╚ż“╣įż╩ż”ĪŻ│░¤²ż▒ż╬GPUżõSSDż╩ż╔ż╬ź╣ź╚źņĪ╝źĖźŪźąźżź╣ż╩ż╔ĘQ¹|╝■╩šĄĪ▀_ż“╝┬║▌ż╦ż─ż╩żżż└źŽĪ╝ź╔ź”ź¦źóæųżŪĪóWindowsż╩ż╔ż╬OSż“Ų░║ŅżĄż╗żŲĪóCPUż¼╠õ¼öż╩ż»Ų░ż»ż╬ż½ż“│╬ż½żßżļĪŻż─ż▐żĻĪóźūźĒź╗ź├źĄż¼╝┬║▌ż╬PCż╦╝²ż▐ż├ż┐ėX▌åż╦Č╦żßżŲŖZżż┤─ČŁżŪŲ░║Ņ╗Ņ┘xż¼╣įż’żņĪó╣ń│╩żĘż┐×æēäż└ż▒ż¼Īóź▐źņĪ╝źĘźóż╬ź┌ź╩ź¾źŁźŃź¾źčź╣ż½żķ└ż─c├µż╬Ė▄Ąęż╦Įą▓┘żĄżņżļ(┐▐ 11)ĪŻ

┐▐10ĪĪPPV╣®µćĪĪĮąųZĪ¦Intel

┐▐11 źūźĒź╗ź├źĄ×æēäż╬║Ł╩±Ī”Įą▓┘╣®µćĪĪĮąųZĪ¦Intel

╝Īövż╬Intelź▐źņĪ╝źĘźó╣®ŠņĖ½│žĄŁĪ╩ŗī4öv=║ŪĮ¬övĪ╦żŪżŽĪóĖÕ╣®µćźūźĒź╗ź╣░╩│░ż╬ŗ╠ńĪ╩źŪźČźżź¾ż¬żĶżė│½╚»źķź▄Īó╔į╬╔▓“└Žźķź▄ĪóźŲź╣ź┐Ī╝×æļ]ŗ╠ńż╩ż╔Ī╦ż“Šę▓żĘżĶż”ĪŻ

╗▓╣═½@╬┴

1. └Kŗō·ĪóĪųIntel║ŪĮjż╬ź▐źņĪ╝źĘźóĖÕ╣®µć╣®Šņż╬ź»źĻĪ╝ź¾źļĪ╝źÓż╦Ų■ż├żŲżŁż┐!ĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2023/09/26)

2. └Kŗō·ĪóĪųIntel 4ż╬╬╠ŠÅż“│½╗ŽżĘż┐źóźżźļźķź¾ź╔ż╬Intel Fab 34ż╦żŽ╩Ż┐¶ż╬EUVż¼Ų│Ų■ĪūĪóź▐źżź╩źėź╦źÕĪ╝ź╣TECH+ (2023/10/02)