QuickLogicż¼ź½ź╣ź┐ź▐źżź║ōļ░Ķż└ż▒ż“źūźĒź░źķźÓż╣żļCSSPżŪĘ╚┬ė├ō²ŗż╦└’ŠS┼Š┤╣

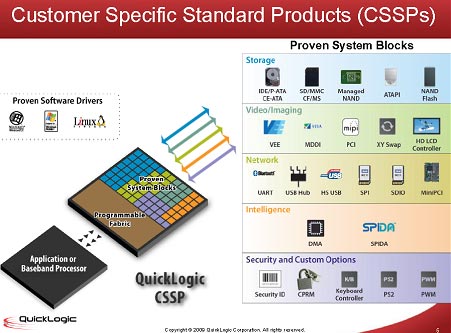

źóź¾ź┴źęźÕĪ╝ź║öĄ╝░ż╬FPGAż“ŪõżĻرż╦żĘżŲżżż┐ä▌QuickLogicż¼×æēä└’ŠSż╬öĄ┐╦ż“╩čż©ż┐ĪŻ┴└ż”▌xŠņżŽĘ╚┬ė┼┼ÅBżõPDAĪóPNDĪ╩źčĪ╝źĮź╩źļź╩źėź▓Ī╝źĘźńź¾źŪźąźżź╣Ī╦ż╩ż╔ż╬Ę╚┬ėĄĪ▀_ĪŻż│ż╬ż┐żß└@├ōż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“┬Ęż©ż╩ż¼żķĪóżĘż½żŌźµĪ╝źČĪ╝ż┤ż╚ż╦ź½ź╣ź┐ź▐źżź║ż╣żļźūźĒź░źķź▐źųźļż╩ŗ╩¼żŌ╗─ż╣ĪŻż│ż”żżż├ż┐öĄ╝░ż“CSSPĪ╩customer specific standard productsĪ╦ż╚Ō}żėĪóż½ż─żŲż╬ź│źóČ\Įčż“Ö┌ż½żĘż╩ż¼żķĪó║Żż╬źµĪ╝źČĪ╝╗┼══ż“╦■ż┐żĘżŲżżż»ż╚żżż”Īó┐Ę└’ŠSż╦æ]ż├żŲĮąż┐ĪŻ

ż½ż─żŲĪóQuickLogicżŽźėźóźĻź¾ź»Ī╩ViaLinkĪ╦Č\Įčż╚Ō}żųĪóźŽĪ╝ź╔ź’źżźõĪ╝ź╔ż╩FPGAż“Š}²Xż▒żŲżżż┐ĪŻż│żņżŽĪó¾H┴žŪ█└■źßź┐źļż╬╬Ńż©żą5┴žų`ż╚4┴žų`ż╬┤ųż╦└õ▒’╦ņż╚żĘżŲż╬źóźŌĪ╝źšźĪź╣Si╦ņż“Ę┴└«żĘżŲż¬żŁĪóżĮżņżķż╬Ū█└■ż“ź▐ź╚źĻź»ź╣ėXż╦ź»źĒź╣żĘżŲż¬ż»╣Įļ]ż“ŠW├ōż╣żļĪŻŪ█└■┤ųż╦┼┼░Ąż“ż½ż▒ż╩ż▒żņżą┼┼╬«żŽ╬«żņż╩żżż¼Īó╣Ōżż┼┼░Ąż“ż½ż▒żļż╚źóźŌĪ╝źšźĪź╣Siż¼źĘźńĪ╝ź╚żĘ┼┼╬«ż¼╬«żņżļĪŻ┼┼╬«ż╬╬«żņżļĪó╬«żņż╩żżż“Īų0ĪūĪóĪų1Īūż╦×┤▒■żĄż╗żļĪŻ▓╚─Ēż╬┼┼ĄżźęźÕĪ╝ź║ż└ż╚Įj┼┼╬«ż¼╬«żņżļż╚└┌żņżŲź¬Ī╝źūź¾ż╦ż╩ż├żŲżĘż▐ż”ż¼ĪóźėźóźĻź¾ź»Č\Įčż└ż╚źĘźńĪ╝ź╚ż╦ż╩żļż┐żßĪóźóź¾ź┴Ī╩╚┐Ī╦źęźÕĪ╝ź║ż╚Ō}ż¾żŪżżżļĪŻ

QuickLogicż╬Andrew Pease╝ę─╣

ż│ż╬öĄ╝░żŽĪóSRAMż“źūźĒź░źķźÓ┴Ū╗ęż╦╗╚ż”“£═Ķż╬FPGAż╦×┤żĘżŲĪóź╗źŁźÕźĻźŲźŻżŽ╣Ōżżż¼1övżĘż½Į±żŁ╣■żßż╩żżż╚żżż”’L┼└ż¼żóżļĪŻżĘż½żĘż╩ż¼żķĪóĪųż│ż╬’L┼└żŽ▐kż─żĘż½ż╩żżż¼Īó1övżŁżĻż╚żżż”’L┼└ż¼ĮjżŁż╣ż«ż┐Īūż╚Ų▒╝ę╝ę─╣ż╬Andrew J. PeaseĢ■żŽĮęĻUż╣żļĪŻźūźĒź░źķźÓż╬żõżĻ─ŠżĘż¼żŁż½ż╩żżż┐żß╣Łżż├ō²ŗż╦żŽ╗╚ż©ż╩żżĪŻż│ż╬ż┐żß¤®├ōĪ󟎟żź©ź¾ź╔ż╬╝Ŗ▒R▀_ż╩ż╔ż╬▌xŠņż╦Ė┬żķżņżŲżżż┐ĪŻżŌż┴żĒż¾ĪóźßźĻź├ź╚żŽFPGAżĶżĻżŌżóż├ż┐ĪŻ╬Ńż©żąĪóźĒĪ╝ż╚ź½źķźÓż╬źķźżź¾ż¼ø]żżż┐żßSRAMź┘Ī╝ź╣żĶżĻżŌ╣ŌÅ]żŪżóżļĪó0.18”╠mżŪ║Ņżļź┴ź├źūż╚FPGAż╬65nmźūźĒź╗ź╣ź┴ź├źūż╚żŽż█ż▄Ų▒żĖĀC└čĪóźūźĒź░źķźÓĖ─ĮĻż¼ź╚źķź¾źĖź╣ź┐żŪżŽż╩żżż┐żßźĻĪ╝ź»┼┼╬«ż¼─Ńż»─ŃŠ├õJ┼┼╬üĪóź╗źŁźÕźĻźŲźŻż¼╣ŌżżĪóż╩ż╔ż╬źßźĻź├ź╚ż¼żóżļĪŻ

Īų└╬ż╬QuickLogicżŽŠW▒ūż“ĮążĘżŲżżż┐ż¼Īó▌xŠņż¼Š«żĄżżż┐żßŪõżĻæųż▓żŌŠ«żĄż½ż├ż┐ĪŻXilinxżõAlteraż╦╚µż┘żļż╚ŪõżĻæųż▓żŽż½ż╩żĻ▓╝ż└ż├ż┐ĪŻź”ź®Ī╝źļÅžżŪżŽżżż»żķŠW▒ū╬©ż¼╣Ōż»żŲżŌŪõżĻæųż▓ż¼Š«żĄż╣ż«żļż╚╝āĘ▐żĄżņż╩żżĪūż╚PeaseĢ■żŽĮęż┘żļĪŻźėźóźĻź¾ź»Č\Į迎─ŃŠ├õJ┼┼╬üż└ż½żķĪó▌xŠņż╬ĮjżŁż╩źŌźąźżźļ▌xŠņż╦Ė■ż»ż½żŌżĘżņż╩żżĪŻż│ż╬żĶż”ż╦╣═ż©ż┐Pease ╝ę─╣żŽĪóBluetoothżõWi-FiĪóźųźĒĪ╝ź╔źąź¾ź╔─╠┐«ż╩ż╔ż¼įu┴Tż╩Broadcom╝ęĮą┐╚ż└ĪŻĪųźóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄż╬ź│ź¾źčź╦ź¬ź¾ź┴ź├źūż╚żżż”├ō²ŗż“┴└ż©żąĪó1ź┴ź├źūż╬źūźĒź░źķź▐źųźļźŪźąźżź╣żŪżŽż╩ż»ĪóCSSPż╚żĘżŲ└@├ō└Łż╬żóżļź½ź╣ź┐źÓź┴ź├źūż╦żŪżŁżļĪūż╚Ų▒Ģ■żŽ╣═ż©ż┐ĪŻ

ż│ż╬CSSPżŽĪóµ£ĀCźūźĒź░źķźÓöĄ╝░żŪżŽż╩ż»Īó╚Š╩¼µć┼┘źūźĒź░źķźÓöĄ╝░ż╦żĘżŲ╗─żĻżŽ║YØŹż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣övŽ®ż“¾H┐¶┼ļ║▄ż╣żļĪŻźūźĒź░źķźÓŗ╩¼ż“ź½ź╣ź┐ź▐źżź║ż╣żļż╬ż└ĪŻĪųBroadcomżõQualcommĪóIntelż╚żżż├ż┐╚ŠŲ│öüźßĪ╝ź½Ī╝żŽI/Oźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż╬└▀╝Ŗ×æļ]ż╦2ŃQż»żķżżż½ż½żļĪŻż│żņżŪżŽUSB1.0ż╬└▀╝Ŗż¼Į¬ż’żļż╚╗■┬ÕżŽUSB2.0ż╦╩čż’ż├żŲżĘż▐ż├żŲżżżļżĶż”ż╩żŌż╬ĪŻBluetoothżŌ1.0ż½żķ2.0ż╦╩čż’żļĪŻUARTżŌŲ▒żĖĪūĪ╩PeaseĢ■Ī╦ĪŻż└ż½żķĪóCSSPż╚żżż”║YØŹēäż“║ŅżĻĪóźµĪ╝źČĪ╝ż¼═▀żĘżżż╚ż│żĒż└ż▒ź½ź╣ź┐ź▐źżź║ż╣żņżą╗■┬Õż╬╩č▓Įż╦żŌż─żżżŲżżż▒żļĪŻźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż╩ż╔║YØŹ┼¬ż╩övŽ®ż“Ų▒╝꿎PSBĪ╩Proven System BlocksĪ╦ż╚Ō}ż¾żŪżżżļĪŻ

ż│ż╬ż█ż╔╚»╔ĮżĘż┐┐Ę×æēäźĘźĻĪ╝ź║ż╦żŽĪóŗī2└ż┬Õż╬VEEĪ╩visual enhancement engineĪ╦ĄĪē”żŪżóżļVEE2.0ż“║YØŹ╗┼══ż╚ż╣żļźŪźŻź╣źūźņźżźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“└▀ż▒ż┐×æēäĘ▓ż¼żóżļĪŻVX4źšźĪź▀źĻĪ╝żŽQualcommż¼╗╚ż├żŲżżżļVESAØŹĄ“ż╬MDDIĪ╩mobile data display interfaceĪ╦ż“×óż©ż┐×æēäĪŻż│żņż▐żŪżŽMIPIĪ╩Mobile Industry Processor InterfaceĪ╦DSIĪ╩Display Serial InterfacesĪ╦ż“×óż©ż┐VX3źšźĪź▀źĻĪ╝ż╚RGB/EBIż╬VX2ż¼ŗī2└ż┬Õ×æēäż╚żĘżŲżóż├ż┐ĪŻQualcommż╬MDDI░╩│░ż╬æä│╩żŽ║YØŹ▓ĮżĄżņż┐żŌż╬ĪŻ

VEEČ\Į迎QuickLogicż¼│½╚»żĘż┐Īó░┼żż▒Ū楿ŪżŌ£½żļż»Ė½ż╗żļČ\ĮčĪŻØŖż╦×Eȧż“źąź├ź»ż╦żĘż┐ĄšĖ„ż╬żĶż”ż╦░┼ż»ż╩ż├żŲżĘż▐ż”▒Ū楿╦░ę╬üż“╚»Ä¦ż╣żļĪŻź│ź¾ź╚źķź╣ź╚ż╬▓─╩čšJ░Žż╦┼Žż├żŲ▓Ķ┴Ūż┤ż╚ż╦ź│ź¾ź╚źķź╣ź╚╚µż“ź└źżź╩ź▀ź├ź»ż╦╩čż©żļż│ż╚żŪ£½żļż»ż╣żļĪŻźąź├ź»źķźżź╚ż“─┤┼DżĘż╩żżż┐żßŠ├õJ┼┼╬üż¼╗\ż©żļż’ż▒żŪżŽż╩żżĪŻ