TSMCż¼20nmż╬źūźĒź╗ź╣ż“═ĶŃQŗī3╗═╚Š┤³ż╦źĻźĻĪ╝ź╣Īó14nmż╦żŌ│½╚»ŠÆŠ}

║Ū└Ķ├╝ż╬IC│½╚»żŪżŽ28nmż╬╬╠ŠÅż¼╗Žż▐ż├ż┐ż¼Īó┴ßż»żŌ20nmźūźĒź╗ź╣ż“2012ŃQż╬ŗī3╗═╚Š┤³ż╦źĻźĻĪ╝ź╣ż╣żļĪóż╚±śŽčTSMC╝ęż╬CTOżŪżóżļJack SunĢ■(┐▐1)żŽĖņż├ż┐ĪŻSunĢ■żŽ╝Īż╬14nm░╩æTż╦ż─żżżŲżŌżĮż╬Ė½─╠żĘż“ĖņżĻĪóż│ż│ż½żķżŽźĻźĮź░źķźšźŻżŌźŪźąźżź╣╣Įļ]żŌĮj(lu©░)żŁż»╩čż’żļż│ż╚ż“┐ā║ȿʿŲżżżļĪŻżĘż½żĘĪóśO┐«ż╦Į╝ż┴░ŅżņżŲżżżļĪŻż╩ż╝ż½ĪŻ

┐▐1ĪĪTSMCż╬CTOżŪżóżļJack SunĢ■

ż│żņż▐żŪ130nmĪó90nmĪó65nmĪó40/45nmĪó28nmż╚żõż├żŲżŁżŲĪó│½╚»ż╬ŠÆŠ}ż½żķ╬╠ŠÅż╬╬®ż┴æųż¼żĻż▐żŪż╬┤³┤ųż¼╝┬żŽĪóż╔ż¾ż╔ż¾ø]ż»ż╩ż├żŲżżżļż│ż╚ż¼żĮż╬śO┐«ż╬╬óż╦żóżļĪŻ╩Ōé╬ż▐żĻż╦─Š└▄┤žĘĖż╣żļźčź┐Ī╝ź¾ż╬’L(f©źng)┤┘╠®┼┘żŽĪó130nmż½żķ40nmż╚╚∙║┘ż╦ż╩żļż╦ż─żņĪóß×═Ų├═░╩▓╝ż╦ż╩żļ┤³┤ųż¼ø]ż»ż╩ż├żŲżżżļĪŻ╬Ńż©żąĪó90nmźūźĒź╗ź╣żŪżŽÖ┌ŠÅ╬╠ż¼źįĪ╝ź»╗■ż╬50%ż╦ż╩żļż╬ż╦12╗═╚Š┤³Ī╩3ŃQĪ╦ż½ż½ż├ż┐ż¼Īó28nmźūźĒź╗ź╣żŽ4╗═╚Š┤³(1ŃQ)żĘż½ż½ż½ż├żŲżżż╩żżĪŻż┐ż└żĘĪóż│ż╬┤³┤ųż╬╬ó¤²ż▒ż╚ż╩żļÉ║öü┼¬ż╩źŪĪ╝ź┐żŽ╣ų▒ķżŪĖ½ż╗ż┐ż└ż▒ż╦é╬ż▐żĻĪó═ĮąMĮĖż╦żŌĘŪ║▄żĘżŲżżż╩żżĪŻSunĢ■ż╦żĶżļż╚Īó28nmż“╬╠ŠÅżĘżŲż½żķż╬źŲĪ╝źūźóź”ź╚ż╬┐¶żŽĪó40nmźūźĒź╗ź╣ż╬╬╠ŠÅż“╗ŽżßżŲż½żķ╬®ż┴żóż¼żļż▐żŪż╬┤³┤ųż¼Ų▒żĖż╚żĘżŲż█ż▄2Ū▄ż╦żŌż╩żļż╚ż╣żļĪŻ28nmż╬╩Ōé╬ż▐żĻżŽĪųvery goodĪūż╚Ė└żżĪóśO┐«╦■Ī╣żŪżóżļĪŻ

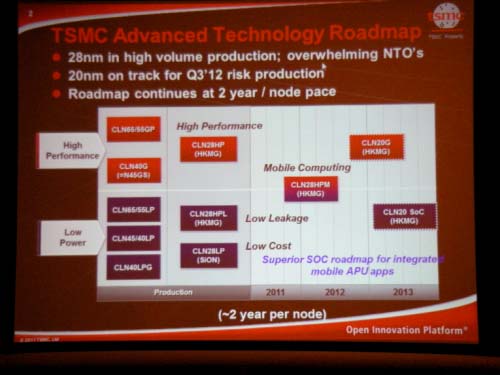

20nmż╦ż─żżżŲżŽż╣żŪż╦SRAMż╬╗Ņ║Ņż╚Ų░║Ņ│╬Ū¦ż“Į¬ż©żŲż¬żĻĪóźßźŌźĻż└ż▒żŪżŽż╩ż»źūźĒź╗ź├źĄżõźĒźĖź├ź»ICż╬źņźĖź╣ź┐ż╩ż╔ż╦żŌ╗╚ż©żļźņź┘źļż╦═ĶżŲżżżļż│ż╚ż“╝┬Š┌żĘż┐ĪŻ▒čARM╝ęż╚─¾Ę╚żĘżŲżżżļTSMCżŽĪóARMż╬Cortex-A9źŪźÕźóźļź│źóż“źŲĪ╝źūźóź”ź╚żĘżŲż¬żĻĪó10ĘŅż╦żŌ20nmźūźĒź╗ź╣żŪ║ŅżļCortex-A15MPCoreż“źŲĪ╝źūźóź”ź╚żĘż┐ż│ż╚ż“╚»╔ĮżĘżŲżżżļĪ╩╗▓╣═½@╬┴1Ī╦ĪŻ20nmż╬źūźĒź╗ź╣×æē俎└Łē”ż“─_£åż╣żļCLN20GĪ╩HKMGĪ╦ż“ż▐ż║─¾ČĪżĘĪó╝Īż╦─ŃŠ├õJ┼┼╬üż╬CLN20 SoCĪ╩HKMGĪ╦ż“2013ŃQż½żķ─¾ČĪż╣żļ(┐▐2)ĪŻ20GżŽ║Ū┐Ę28nmźūźĒź╗ź╣ż╬28HPĪó20SoCżŽ28HPMż╚żĮżņżŠżņ╚µż┘żŲĪó└Łē”żŽ2.1Ū▄ż╦ź╣źżź├ź┴ź¾ź░┼┼╬üżŽ0.75Ū▄░╩▓╝ż╦ż╩żļż╚Ė½└čżŌż├żŲż¬żĻĪóź┴ź├źūżŽ35Ī┴40%Š«żĄż»ĪóÅ]┼┘żŽ20%░╩æųÅ]ż»ĪóŠ├õJ┼┼╬üżŽ30%░╩▓╝ż╦Š«żĄż»ż╩żļż╚żĘżŲżżżļĪŻ

┐▐2ĪĪ2012ĖÕ╚Šż½żķ20nmźūźĒź╗ź╣ż“źĻźĻĪ╝ź╣ż╣żļ

20nmźūźĒź╗ź╣żŪżŽĪóź▓Ī╝ź╚źķź╣ź╚╣Įļ]ż“╗╚żżĪóź▓Ī╝ź╚└õ▒’╦ņż“╠®ż╦żĘż╩ż¼żķŪ÷ż»ż╣żļż│ż╚żŪ╚∙║┘▓Įż╦żŌ×┤▒■żĘĪóŪ█└■ŗ╩¼żŽ─Ń°BŃ^ż╬CuŪ█└■ż“╗╚ż”ż╩ż╔ż╬╣®╔ūż“╗▄żĘżŲżżżļĪŻSiż╬Ž─ż▀ż╦×┤żĘżŲżŌGeż╬Ū█╩¼╬╠ż“╩čż©ĪóSiNż╬ŗ╩¼ż╦żŌ╣®╔ūż“Č┼żķżĘĪóż│żņż▐żŪż╬źūźĒź╗ź╣ż“┐╩▓ĮżĄż╗żļż╚żżż├ż┐╚∙öéż╩╣®╔ūż╦żĶż├żŲ╝┬ĖĮżĘżŲżżżļĪŻ

20nmż╬źĻźĮź░źķźšźŻżŪżŽĪóNA=1.35ż╬ArFķ]┐╗źĻźĮź░źķźšźŻż╬ź└źųźļźčź┐Ī╝ź╦ź¾ź░ż“╦▄╠┐ż╚żĘżŲ╗╚żżĪóź▐źļź┴źėĪ╝źÓż“╗╚ż”┼┼╗ęźėĪ╝źÓźĻźĮź░źķźšźŻż╚ĪóEUVĪ╩NA=0.25Ī╦żŌŲ│Ų■żĘżŲżżżļĪŻź└źųźļźčź┐Ī╝ź╦ź¾ź░żŪżŽŲ╚śOż╬└▀╝ŖźļĪ╝źļż“║ŅżĻæųż▓Īóź½ź╣ź┐ź▐ż¼Ž¬Ė„ż“2övż╦╩¼ż▒żļż┐żßż╬ź▐ź╣ź»ż“║ŅżļØŁ═ūżŽż╩żżĪŻż╣ż┘żŲTSMCż¼ź▐ź╣ź»ż“Ų¾ż─ż╦╩¼ż▒żļĪŻ

┼┼╗ęźėĪ╝źÓŽ¬Ė„żŪżŽź▐źļź┴źėĪ╝źÓż╬źėĪ╝źÓ╦▄┐¶ż“1╦³3000╦▄ż╦╗\żõżĘź”ź¦Ī╝źŽĮĶ═²ĮŚ┐¶ż╚żĘżŲ10 wphĪ╩wafers per hourĪ╦ż“╝Ŗ▓ĶżĘżŲżżżļż¼ĪóĖĮ╝┬ż╬ź╣źļĪ╝źūź├ź╚żŽż▐ż└1wphż╦żŌ╦■ż┐ż╩żżĪŻ▐köĄ(sh©┤)ĪóEUVŽ¬Ė„ĄĪż╚żĘżŲź¬źķź¾ź└ASML╝ęż╬NXE3100ż“└▀ÅøżĘ27nmźčź┐Ī╝ź¾ż“NA=0.25ż╬╚┐╝o(j©¼)Ė„│žÅUżŪ4.5 wph░╩▓╝ż╚żżż”±T▓╠ż“įużŲżżżļĪŻ

Č”ż╦╔įØ▓╩¼ż╩ż¼żķżŌ14nmżŪżŽż╔ż┴żķż½ż╬┬ō(li©ón)┘IżĘż½ż╩żżż╚żĘżŲżżżļĪŻź▐źļź┴źėĪ╝źÓż╬EBżŪżŽź»źķź╣ź┐╣Į└«żŪ100 wph░╩æųĪóEUVżŪżŌNA0.33ż╬Ė„│žÅUżŪ100 wph░╩æųż╬ź╣źļĪ╝źūź├ź╚ż“ų`╗žżĘżŲżżżļĪŻ

żĮż╬╝Īż╬14nmż╦ż─żżżŲżŌĖ”ē|│½╚»ż“╗ŽżßżŲż¬żĻĪóMUGFETĪóFINFETż╩ż╔ż╬źŪźąźżź╣╣Įļ]żõGeż“żŽżĖżßż╚ż╣żļ╣ŌöĪŲ░┼┘║Ó╬┴ż“╔ĮĀC┼┼╗ę┴÷╣į┴žż╦╗╚ż”źŪźąźżź╣ż¼ĖĪŲżż╦Ų■ż├żŲżżżļĪŻżĮż╬╝┬┘xż╚żĘżŲ22nmż╬źņźżźóź”ź╚żŪ║Ņż├ż┐FINFETż“Īó║“ŃQż╬IEDMżŪ╚»╔ĮżĘżŲżżżļż¼Ī󟥟ųź╣źņź├źĘźńźļź╔┼┼╬«ż╬’łżŁż¼70mV/decadeż╚źūźņĪ╝ź╩╣Įļ]żŪżŽįużķżņż╩żż├═ż“įużŲżżżļĪŻż│ż╬├═ż╦żĶżĻĪó┼┼░Ąż“▓╝ż▓żŲżŌŲ░║ŅżŪżŁżļż│ż╚ż“┐āżĘĪóĄšż╦FINFETżŪżŽż╩ż»“£═Ķż╬źūźņĪ╝ź╩FETżŪżŽżŌżŽżõźĄźųź╣źņź├źĘźńźļź╔┼┼╬«ż╬’łżŁż“▓╝ż▓żķżņż╩żżż┐żßĪóź╚źķź¾źĖź╣ź┐żŽ╗╚ż©ż╩żżż╚żĘżŲżżżļĪŻż┴ż╩ż▀ż╦14nmżŪFINFET╣Įļ]ż└ż╚0.75Ī┴0.7VŲ░║Ņż╦ż╩żĻżĮż”ż└ż╚SunĢ■żŽ═Į▒Rż╣żļĪŻ14nmżŪżŽSOIżŽżŌżŽżõ┬ō(li©ón)┘I╗Ķż╦Ų■żķż╩żżĪŻSOIżŽ┴Ļ╩čż’żķż║ź╦ź├ź┴▌xŠņż╦╗╚ż’żņżļż└żĒż”ż¼ĪóźßźĖźŃĪ╝ż╦żŽż╩żĻż©ż╩żżż╚Ų▒Ģ■żŽĖ½żŲżżżļĪŻ

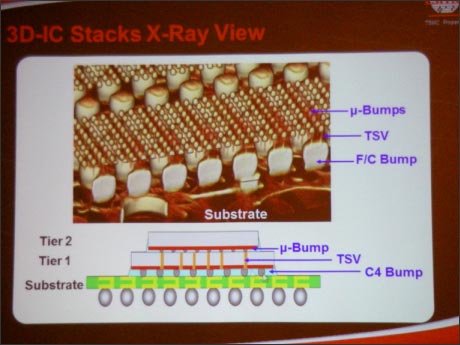

╚∙║┘▓Įż╚żŽ╩╠ż╦╣ŌĮĖ└čż“├Ż└«ż╣żļČ\Įčż╚żĘżŲ3╝ĪĖĄICż¼żóżļĪŻTSMCżŽźĄźųźĘź╣źŲźÓźżź¾źŲź░źņĪ╝źĘźńź¾ż╚żĘżŲĪóźūźĻź¾ź╚Ū█└■┤łæųż╦DRAM8Ė─ż╚GPU1Ė─ż╬źĄźųźĘź╣źŲźÓż“1źčź├ź▒Ī╝źĖż╦╝²żßżļSiźżź¾ź┐Ī╝ź▌Ī╝źČČ\Įčż“─¾░ŲżĘżŲżżżļĪŻSiż╬źżź¾ź┐Ī╝ź▌Ī╝źČż╦żŽ¾H┴žŪ█└■ż“╣Į└«żĘżŲż¬żŁĪóGPUż╚DRAMż“żĮż╬æųż╦źšź¦Ī╝ź╣ź└ź”ź¾żŪź▐źżź»źĒźąź¾źūż“─╠żĖ└▄¶öż╣żļĪ╩┐▐3Ī╦ĪŻĖ▄Ąęć@żŽĖņżķż╩żżż¼Īóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļżŪŠę▓żĘż┐źČźżźĻź¾ź»ź╣ż╬Vertex-7 FPGA4Ė─ż“źżź¾ź┐Ī╝ź▌Ī╝źČæųż╦ĮĖ└čżĘż┐Č\Įčż╚ō¶żŲżżżļĪ╩╗▓╣═½@╬┴2Ī╦ĪŻ

┐▐3ĪĪSiźżź¾ź┐Ī╝ź▌Ī╝źČæųż╦TSVżŪź┴ź├źūż╚└▄¶ö

450mmż╦┤žżĘżŲżŽĪóżŌż├ż╚ź░źĻĪ╝ź¾ż╩╣®Šņż“║Ņżļż│ż╚ż“ų`╗žż╣ĪŻ2013Ī┴2014ŃQż╦żŽ┐Ęāń▌xż╦żóżļFab12ż╦źčźżźĒź├ź╚źķźżź¾ż“║ŅżĻĪóÖ┌ŠÅżŽ±ś├µż╦żóżļFab15żŪ2015Ī┴2016ŃQ║óż╦╗Žżßżļ═Į─Ļż└ż╚żĘżŲżżżļĪŻ

╗▓╣═½@╬┴

1. ARM and TSMC Tape Put First 20nm ARM Cortex-A15 Multicore Processor

2. 28nmż╬FPGAżŽźżź¾ź┐Ī╝ź▌Ī╝źČŠW(w©Żng)├ōżŪTbps╝┬ĖĮĪóź▐źļź┴ź│źóŲŌē┼żŪĮĶ═²Ī”▓“└Ž├ōż╦ (2011/10/26)