Mentorż¼źšźĪĪ╝ź╣ź╚źĘźĻź│ź¾ż╬▐k╚»┤░Ų░ż“╝┬ĖĮż╣żļäė╬üź─Ī╝źļż“╚»╔Į

ä▌Mentor Graphics╝꿎Īó45nmźūźĒź╗ź╣░╩æTż╬LSIż“╩Ōé╬żĻ╬╔ż»║Ņżļż┐żßż╬ر═²└▀╝ŖĪ”ĖĪŠ┌Ī”╩Ōé╬ż▐żĻĖ■æųż▐żŪż“┤▐żßż┐ر═²└▀╝Ŗź─Ī╝źļż“DAC (Design Automation Conference) 2008żŪźĻźĻĪ╝ź╣żĘż┐ĪŻ╚ŠŲ│öüźūźĒź╗ź╣ż╬źĻźĮź░źķźšźŻØó╦Īż¼Ė„ż╬āS─╣Ī╩ż½ż─żŲżŽźĻźĮź░źķźšźŻż╬Ė┬─cØó╦Īż╚Ė└ż’żņż┐Ī╦żĶżĻżŌø]ż»ż╩ż├żŲżŁżŲżżżļż┐żßĪóźčź┐Ī╝ź¾─╠żĻż╬Øó╦Īż“▓├╣®ż╣żļż│ż╚ż¼žMżĘż»ż╩ż├żŲżŁżŲżżżļĪŻżĮżņż“╗Ņ╣įēžĖĒżŪ▌ö┘ćżĘżŲżŁż┐ż¼Īó║Żövż╬ź─Ī╝źļżŽź┐źżź▀ź¾ź░ż½żķźūźĒź╗ź╣ż╬źąźķź─źŁż▐żŪ┤▐żßżŲśOŲ░▓ĮżĘżĶż”ż╚żżż”żŌż╬ĪŻ

LSIż╬└▀╝Ŗ╩¼╠ŅżŽĪóźĘź╣źŲźÓż╦ŖZżżźņź┘źļżŪżŽż╩żĖż▀ż╬Ū÷żżVHDLżõVerilogż╦┬Õż’ż├żŲĪóżŌż├ż╚│┌ż╦├»żŪżŌ└▀╝ŖżŪżŁżļöĄ╦Īż╚żĘżŲĪóCĖ└Ėņ└▀╝Ŗż“ź┘Ī╝ź╣ż╦ż╣żļESLĪ╩electronic system levelĪ╦ż¼ÅRų`żĄżņżŲżżżļĪŻCż╦żĶżļźūźĒź░źķź▀ź¾ź░Ė└ĖņżŪ└▀╝ŖżĘż┐żóż╚Īóź│ź¾źčźżźķżŪRTLźņź┘źļż▐żŪ╩č┤╣ż╣żļż’ż▒ż└ż¼ĪóRTLźņź┘źļż╬Č\Į迎żŌżŽżõ┤░└«żĘ┐įż»żĘżŲż█ż╚ż¾ż╔ÅB¼öż╦żŌæųżķż╩żżż¼ĪóRTLźņź┘źļż½żķر═²┼¬ż╩Ū█ÅøĪ”Ū█└■ż“ķWż»ż╚ż│żĒż¼żżż▐Įj╠õ¼öż╦ż╩ż├żŲżżżļĪŻ

éb═²źņź┘źļżŪżŽ╝┬║▌ż╬ź┐źżź▀ź¾ź░ż“ĖĪŠ┌żŪżŁż╩żżż┐żßĪó═▀żĘżż└Łē”ż¼╦▄┼÷ż╦įużķżņżļż╚żŽĖ┬żķż╩żżĪŻź┴ź├źūż“źĘźĻź│ź¾ż╦ŠŲżŁ¤²ż▒żŲż½żķ└Łē”ż¼Įąż╩żżĪóż╚żżż”żĶż”ż╩ż│ż╚żŽżŌżŽżõß׿Ążņż╩żżĪŻżĮżņżŌĪųź▓Ī╝ź╚ęÆūāżõŪ█└■ęÆūāż╬źŌźŪźļżŽżŌżŽżõāįĄŅż╬żŌż╬ż╦ż╩żĻĪó║Żżõź╬źżź║żõźĘź░ź╩źļźżź¾źŲź░źĻźŲźŻż¼ź┴ź├źūźņź┘źļżŪĄßżßżķżņżļżĶż”ż╦ż╩ż├żŲżŁżŲżżżļĪūĪóż╚Mentor╝ęDesign-to-Siliconŗ╠ńż╬╔¹╝ę─╣Ę¾źĖź¦ź═źķźļź▐ź═źĖźŃĪ╝żŪżóżļJoe SawickiĢ■żŽĮęż┘żļĪŻź┐źżź▀ź¾ź░ż╬ęÆūāżõź»źĒź├ź»ź╣źŁźÕĪ╝ż“╦╔ż░ż└ż▒żŪżŽż╩żż╗■┬Õż╦Ų═Ų■żĘż┐ĪŻ

ź┐źżź▀ź¾ź░ż└ż▒żŪżŽż╩żżĪŻźĻźĮź░źķźšźŻżŪźčź┐Ī╝ź¾─╠żĻż╬Øó╦Īż“żĮż╬ż▐ż▐▓├╣®żŪżŁż╩żżż╚żżż”╗■┬Õż╦żŌŲ■ż├żŲżżżļĪŻØ±═²└▀╝Ŗż╚ź▐ź╣ź»źŪĪ╝ź┐ż╚ż╬┤ųż╬┤žĘĖż¼ż│żņż▐żŪż╦ż╩ż»ĪóŌg╠®ż╩┤žĘĖż¼ĄßżßżķżņżļĪŻ

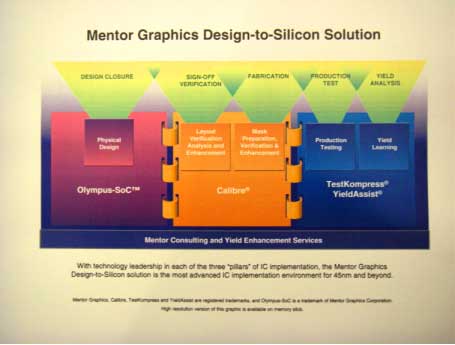

║ŻövMentorż¼┐Ę╗■┬Õż╬ر═²└▀╝Ŗź─Ī╝źļż╚żĘżŲ┐āżĘż┐ż╬żŽĪóįÆż─ż╬ĮjżŁż╩├ņż½żķż╩żļź─Ī╝źļżŪżóżļĪŻLSIæųż╬żĄż▐żČż▐ż╩övŽ®ż╬Ū█Åøż╚żĮżņżķżõżĮż╬ŲŌŗż“ż─ż╩ż░Ū█└■ż╬└▀╝ŖźĘź╣źŲźÓOlympus-SoCż╚Īóź┴ź├źūż╬Ū█ÅøŪ█└■ż¼┘ćżĘżż±T▓╠ż“ĖĪŠ┌żĘĪ󿥿ķż╦źĻźĮź░źķźšźŻż╬▌ö┘ćż▐żŪ╣įż”CalibreĪóżĮżĘżŲįÆż─ų`żŽLSIż╬éb═²Ų░║Ņż“źŲź╣ź╚żĘ╩Ōé╬żĻ▓“└Žż“╣įż”TestKompress/YieldAssistżŪżóżļĪŻż│żņżķ3╦▄ż╬ź─Ī╝źļż“┼²╣ńżĘżŲźšźĪĪ╝ź╣ź╚źĘźĻź│ź¾ż╬▐k╚»┤░Ų░ż¼ż╔ż╬╚ŠŲ│öüźßĪ╝ź½Ī╝żŪżŌżŪżŁżļżĶż”ż╦ż╣żļĪŻżĮż╬┼²╣ń║ŅČ╚ż╦żŌŠÆŠ}żĘ╗Žżßż┐ż╚ĪóSawickiĢ■żŽĖ└ż”ĪŻ

Olympus-SoCżŽĪóSierra Design Automation╝ęż¼─¾ČĪżĘżŲżżż┐ź─Ī╝źļżŪĪó║“ŃQMentorż¼āA╝²żĘżŲŠ}ż╦Ų■żņż┐żŌż╬ĪŻSieraż╬źµĪ╝źČĪ╝żŪżóż├ż┐ĪóSTMicroelectronicsżŽMentorż╬ĖĪŠ┌ź─Ī╝źļCalibreż╚┴╚ż▀╣ńż’ż╗żķżņżļż┐żßĪó╗╚żżżõż╣ż»ż╩ż├ż┐ż╚żĘżŲżżżļĪŻź┐źżź▀ź¾ź░▓“└ŽźóĪ╝źŁźŲź»ź┴źŃż“Ų│Ų■Īó¾H┐¶ż╬źūźĒź╗ź╣ź│Ī╝ź╩Ī╝żõ└▀╝ŖźŌĪ╝ź╔ż“║Ū┼¼▓Įż╣żļĪŻŪ█└■żŪżŌDFMż“╣═╬ĖżĘż┐Ū█└■Š}╦Īż“║╬żĻŲ■żņżŲżżżļĪŻżĄżķż╦Īó─ŃŠ├õJ┼┼╬ü└▀╝Ŗż╦├ōżżżķżņżļź▐źļź┴┼┼Ė╗ż╦żŌ×┤▒■żŪżŁżļĪŻ

Mentorż╬CalibreżŽĪóöĄµć╝░ź┘Ī╝ź╣ż╬DRCźšźĪź▀źĻĪ╝ż╚żĘżŲ▓■╬╔żĘ║ŻövĪó2╝ĪĖĄ/3╝ĪĖĄŪ█└■ż╬ĖĪŠ┌ż¼żŪżŁżļżĶż”ż╦ż╩ż├ż┐ĪŻ3╝ĪĖĄżŽŪ█└■ż╬├╩║╣żõźėźóź█Ī╝źļĪóź│ź¾ź┐ź»ź╚ź█Ī╝źļż╬ż╩ż╔ż╬ź┴ź¦ź├ź»ż╦░ę╬üż“╚»Ä¦ż╣żļĪŻż▐ż┐źßźŌźĻĪ╝ż╬ĖĪŠ┌╗■┤ųż¼ż½ż╩żĻø]Į╠żĘż┐ż╚żĘżŲżżżļĪŻżĄżķż╦CMPAnalyzerż╚Ō}żų╩┐┘Q└Łż╬║Ū┼¼▓ĮżŌ┐▐żņżļĪŻż│żņżŽCMPż╚źņźżźóź”ź╚╠®┼┘ż╬▓“└ŽŠ}╦Īż“╗╚ż├żŲźßź┐źļż╬ļmżß╣■ż▀ż╩ż╔ż“ź┴ź¦ź├ź»ż╣żļĪŻCalibre nmLVSź─Ī╝źļżŌ┼ļ║▄żĘĪóźņźżźóź”ź╚ż╚Ū█Åø┐▐Ę┴ż╬ź┴ź¦ź├ź»ż“ź┴ź¦ź├ź»żĘżŲT┘ćżŪżŁżļż╚żżż”ĄĪē”ż“Ęeż─Ī╩ż┐ż└żĘĪó▌xŠņżŪŲ■Š}żŪżŁżļż╬żŽ2008ŃQĖÕ╚ŠĪ╦ĪŻ

ż│żņżķż╬ź─Ī╝źļż“╗╚ż├żŲ390╦³ź▓Ī╝ź╚ż╬Ēö╣ń┬Š╝ęż╬×æēäövŽ®ż“65nmźūźĒź╗ź╣żŪ╗Ņ║Ņäh▓┴żĘżŲż▀ż┐ż╚ż│żĒĪóĒö╣ń┬Š╝ęż╚╚µż┘żŲź»źĒź├ź»ż╬żążķż─żŁżŽ40%─ŃžōżĘĪóźąź├źšźĪż╚żĘżŲź┴ź├źūż╦┼ļ║▄żĘżŲżżż┐ĀC└迎50%žōżĻĪóź╚Ī╝ź┐źļż╬ĀC└迎18%║’žōżŪżŁż┐ż╚żżż”ĪŻź└źżź╩ź▀ź├ź»Ų░║Ņ╗■ż╬Š├õJ┼┼╬üżŽ20%žōŠ»żĘżŲżżżļĪŻź»źĒź├ź»ź╣źŁźÕĪ╝żŽ40%žōż├ż┐ż╚żżż”ĪŻ

ż▐ż┐ĪóŪ█ÅøĪ󟻟Ēź├ź»Ąļ┼┼ĪóŪ█└■Īó║Ū┼¼▓ĮĪóDFMż╩ż╔ż╬ĮĶ═²ż“ź▐źļź┴ź╣źņź├ź╔Ī”ź▐źļź┴ź│źóöĄ╝░żŪ╩┬š`ĮĶ═²╝ŖōQżĘżŲĄßżßżļż’ż▒żŪżóżļż¼ĪóØŖ╩╠ż╩╣ŌÅ]ź│ź¾źįźÕĪ╝ź┐ż“×æ║Ņż╣żļż’ż▒żŪżŽż╩ż»Īó▌x╚╬ż╬Linuxź┘Ī╝ź╣ż╬ź’Ī╝ź»ź╣źŲĪ╝źĘźńź¾żŪ╝ŖōQżĘżŲżżżļĪŻCalibreż╬öĄµć╝░ź┘Ī╝ź╣ż╬└▀╝Ŗź┴ź¦ź├ź»ź─Ī╝źļżŽĪóŖZ└▄ź┴ź¦ź├ź½Ī╝żŪżŽĖĪĮążĄżņż╩żżż¼Īó┼┼╬«ĮĖ├µż“ÅŚż│żĘżõż╣żżµć┼┘ż╦▀`żņżŲżżżļź│ź¾ź┐ź»ź╚ż╬░╠ÅøżŌ╚»Ė½żŪżŁżļż┐żßĪó┼┼╬«ĮĖ├µż“╦╔ż░ż│ż╚ż¼żŪżŁżļĪŻźŌźŪźļż“ż│ż╬żĶż”ż╩ĮĻż╦żŌ╬®żŲżŲ╝ŖōQż╣żļĪŻżŌż┴żĒż¾źĻźĮźšźņź¾ź╔źĻż╩ź─Ī╝źļż└ż▒ż╦Ū█└■ż¼║┘ż»ż╩żĻż╣ż«żŲżżżļżĶż”ż╩ź█ź├ź╚ź╣ź▌ź├ź╚ż“ĖĪĮążŪżŁżļż│ż╚żŽżżż”ż▐żŪżŌż╩żżĪŻ

ż▐ż┐Īóéb═²źŲź╣ź╚ż╬ź─Ī╝źļżŪżŽĪóśŗż╩żļĮĖ└č┼┘Ė■æųż╦żĶżĻźŲź╣ź╚źŪĪ╝ź┐ż╬╗\▓├ż╦×┤żĘżŲĪóATPGż“░ĄĮ╠ż╣żļĄĪē”ż“┼ļ║▄żĘżŲżżżļĪŻ║ŻżŽĪóTestKompress Xpressż└ż¼Īó2011ŃQ░╩æTż╦Ė■ż▒ĪóTestKompress In-SystemżõTestKompress Low-Power OverdriveĪ󿥿ķż╦ TestKompress Multicoreż╚żżż”įÆż─ż╬│½╚»ż“Ų▒╗■ż╦┐╩żßżŲżżżļĪŻ▒ŻżņżŲĖ½ż©ż╩żżźĘź╣źŲź▐ź┴ź├ź»ż╩’L┤┘ż“Ų▒─Ļż╣żļÜżéāźóźļź┤źĻź║źÓż“│½╚»Īó╩Ōé╬żĻż“Ė■æųżŪżŁżļż╚żĘżŲżżżļĪŻ