Intelż¼ź▐źļź┴ź│źóźūźĒź╗ź├źĄż╚ź│źóż┤ż╚ż╬źßźŌźĻĪ╝ż“TSVżŪż─ż╩ż░źĘź╣źŲźÓż“╚»╔Į

ä▌Intel╝꿎Īó3╝ĪĖĄź┴ź├źūź╣ź┐ź├ź»╝┬äóż¼ź▐źļź┴ź│źóźūźĒź╗ź├źĄźĘź╣źŲźÓż╬źßźŌźĻĪ╝źąź¾ź╔╔²ż“╣Łż▓żļż╬ż╦Ń~Ė·żŪżóżļż│ż╚ż“ĪóASETĪ╩«Ć└Ķ├╝┼┼╗ęČ\Įč│½╚»ĄĪ╣ĮĪ╦╝ń╠¢ż╬International 3D System Integration Conference 2008żŪ┐āżĘż┐ĪŻ┼ņ»B╗h┬Õ┼─ČĶż╬▐kź─ČČ╣ųŲ▓żŪ│½╠¢żĄżņż┐Īó║ŻŃQż╬3D-SICżŽĪó┤─┤╣ų▒ķż“┤▐żß28°Pż╬╣ų▒ķ╚»╔Įż╚18°Pż╬ź▌ź╣ź┐Ī╝ź╗ź├źĘźńź¾ż¼żóż├ż┐ĪŻ

ĖĮ║▀ĪóźßźŌźĻĪ╝ż╬źąź¾ź╔╔²ż¼źūźĒź╗ź├źĄż╬I/OźŪĪ╝ź┐źņĪ╝ź╚ż╦ż─żżżŲżżż▒ż╩żżż█ż╔║╣ż¼ż─żżżŲżĘż▐ż├żŲżżżļĪŻż│ż╬║╣ż“Į╠żßżĶż”ż╚żżż”╚»„[ż¼Intelż╬╗žĖ■ż╣żļ3╝ĪĖĄ╝┬äóżŪżóżļĪŻźßźŌźĻĪ╝ż╬źąź¾ź╔╔²ż“╣Łż▓żļż┐żß├▒ĮŃż╦╩┬š`ż╦źŪĪ╝ź┐ż“ŲDżĻĮąż╣ż╩żķ║╣Ų░öĄ╝░żŪżŽ400źįź¾żŌż╬źŪĪ╝ź┐└■ż¼ØŁ═ūż╦ż╩żļĪŻżĮż╬ĖČ░°ż╬▐kż─żŽI/Oźķźżź¾ż╬┐«ęÄż╬ęÆżņż╦żĶżļĪŻ┐«ęÄāSĘ┴żŽ╩°żņĪóż╣ż╩ż’ż┴źĘź░ź╩źĻźżź¾źŲź░źĻźŲźŻż¼ĄKż»ż╩żļż┐żßĪóź╬źżź║×┤║÷żŽżŌż┴żĒż¾ż╬ż│ż╚ĪóźūźĻź©ź¾źšźĪźĘź╣Īóźżź│źķźżźČĮĶ═²ż╩ż╔ż╬āSĘ┴┼DĘ┴ĮĶ═²ż¼ØŁ═ūż╦ż╩żĻövŽ®ż¼╩Ż╗©ż╦ż╩ż├żŲżĘż▐ż”ĪŻżĘż½żŌ╩¼╔█─Ļ┐¶övŽ®┼¬ż╩┼┼╝¦āSż╚żĘżŲż╬╚┐╝oż“╣═╬ĖżĘż╩ż▒żņżąż╩żķż╩żżĪŻ3╝ĪĖĄź╣ź┐ź├ź»╝┬äóżŪźūźĒź╗ź├źĄż╬ź┐źżźļż╚źßźŌźĻĪ╝ż╬ź┐źżźļż╚ż╬š{▀`ż¼ŖZż▒żņżąĪóŪ█└■°BŃ^żõźżź¾ź└ź»ź┐ź¾ź╣ż╬▒ŲūxżŽ╠Ą£åżŪżŁżļż┐żßĪóźĘź░ź╩źļźżź¾źŲź░źĻźŲźŻż╬└▀╝Ŗż¼ØÖŠ’ż╦│┌ż╦ż╩żļĪŻ

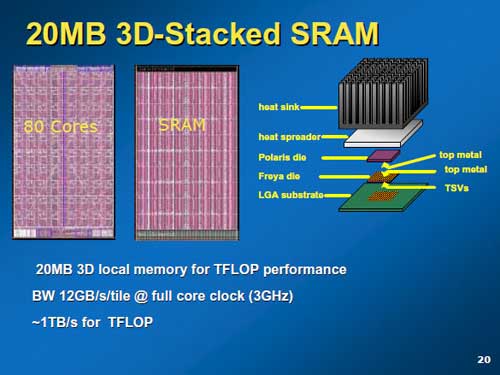

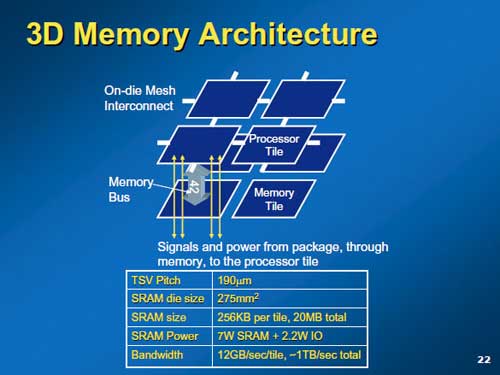

Intelż¼┐āżĘż┐ż│ż╬3╝ĪĖĄ╝┬äóźĘź╣źŲźÓżŽĪó80ź│źóż“ĮĖ└čżĘż┐źūźĒź╗ź├źĄź┴ź├źūż╬├µż╬ź│źóĪ╩ź┐źżźļż╚Ō}żųĪ╦ż╚20Mźąźżź╚ż╬SRAMź┴ź├źūż“80źųźĒź├ź»ż╦╩¼ż▒żĮżņżŠżņż╬źųźĒź├ź»ż“ź┐źżźļż╚źąź╣żŪ±Tżųż╚żżż”źĘź╣źŲźÓ╣Į└«żŪżóżļĪŻźßźżź¾źßźŌźĻĪ╝ż╚źóź»ź╗ź╣ż╣żļØiż╦ĪóL1ĪóL2źŁźŃź├źĘźÕż╦▓├ż©ĪóźĒĪ╝ź½źļźßźŌźĻĪ╝żŌŪ█Åøż╣żļż│ż╚żŪĪó╣ŌÅ]└Łż“░▌ĘeżŪżŁżļĪŻ

ĘQźūźĒź╗ź├źĄź┐źżźļż╚źßźŌźĻĪ╝ź┐źżźļżŽ42źįź¾ż╬─╠Š’ż╬źąź╣żŪ±Tż¾żŪżżżļĪŻż│ż╬źąź¾ź╔╔²żŽĪó3GHzŲ░║Ņż╬źšźļź│źóź»źĒź├ź»żŪ1ź┐źżźļ┼÷ż┐żĻ12Gźąźżź╚/╔├ż╚ż╩żĻĪó╬Šź┴ź├źūµ£öüż╬źąź¾ź╔╔²żŽĪó«Ć╩┬š`ź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╦żšżĄż’żĘżż1Tźąźżź╚/╔├ż╦ż╩żļĪŻSRAMż╬Š├õJ┼┼╬üżŽ7WĪóI/OżŪż╬żĮżņżŽ2.2WżŪżóżļĪŻ

80ź│źóż“┼ļ║▄żĘż┐źūźĒź╗ź├źĄź┴ź├źūż╬ĮjżŁżĄżŽĪó21.72mm x 12.64mm= 275mm2żŪĪóź┐źżźļ▐kż─ż╬ĮjżŁżĄżŽ2.0mm x 1.5mmżŪżóżļĪŻźūźĒź╗ź├źĄź┴ź├źūżŽĪó65nmż╬CMOSźūźĒź╗ź╣żŪ×æļ]żĘĪó┴Ēź╚źķź¾źĖź╣ź┐┐¶żŽ1▓»Ė─ż╦Ą┌żųĪŻź┴ź├źū├▒öüż╬źčź├ź▒Ī╝źĖż└ż╚Īó1248źįź¾ż╬LGAż╦14┴žŪ█└■Īó343┐«ęÄ└■ż“╝²═Ųż╣żļĪŻ20Mźąźżź╚ż╬SRAMź┴ź├źūżŌŲ▒żĖĮjżŁżĄż╬275mm2żŪżóżļĪŻ╬ŠŪvż“ż─ż╩ż░TSVĪ╩through silicon viaĪ╦ż╬źįź├ź┴żŽ190”╠mĪŻ

└č┴ž╣Įļ]ż╚żĘżŲżŽĪóLGAĪ╩źķź¾ź╔ź░źĻź├ź╔źóźņźżĪ╦┤łż╬æųż╦SRAMĪóżĮż╬æųż╦ź▐źļź┴ź│źóźūźĒź╗ź├źĄź┴ź├źūĪ󿥿ķż╦╩³ÕXłż╚źęĪ╝ź╚źĘź¾ź»ż“║▄ż╗żŲżżż»ĪŻ╬Šź┴ź├źūżŽźšź¦Ī╝ź╣ź─Ī╝źšź¦Ī╝ź╣żŪ└▄¶öż╣żļĪŻ╣ų▒ķżĘż┐Ų▒╝ęMicroprocessor TechnologyĖ”ē|ĮĻż╬Shekhar BorkaĢ■żŽĪóż│żņż▐żŪżŽŪ█└■żŪŠ├õJż╣żļ┼┼╬üżŽ╠Ą£åżĄżņżŲżŁż┐ż¼ĪóźßźŌźĻĪ╝ż¼DDR3żžż╚╣ŌÅ]ż╦ż╩żļż╦ż─żņĪóż│ż╬Š├õJ┼┼╬ü▓■║¤żŽ’Lż½ż╗ż╩ż»ż╩żļż╚ż▀żŲżżżļĪŻ