Intel AI Everywhere└’ŠSż╬ŗī1É×Ī󟬟šźķźżź¾PCæųżŪÖ┌└«AIż¼▓─ē”ż╦

IntelżŽĪóAI Everywhere└’ŠSż“║╬żļż│ż╚ż“ļxĖ└żĘż┐ĪŻżĮż╬┬Õ╔Į┼¬ż╩╬Ńż╚żĘżŲAIź©ź¾źĖź¾ż“ĮĖ└čżĘż┐źčźĮź│ź¾Ė■ż▒CPUĪųCore UltraĪ╩ź│Ī╝ź╔ć@Meteor LakeĪ╦ĪūĪ╩┐▐1Ī╦ż“╚»Ūõż╣żļż╚ż╚żŌż╦ĪóźĄĪ╝źąĪ╝Ė■ż▒ż╬CPUĪųŗī5└ż┬Õż╬XeonźūźĒź╗ź├źĄĪūż╦żŌAIź©ź¾źĖź¾ż“ĮĖ└čżĘż┐ĪŻżĄżķż╦AI└ņ├ōź┴ź├źūĪųGaudi 3Īūż“2024ŃQż╦╚»Ūõż╣żļż│ż╚żŌ£½żķż½ż╦żĘż┐ĪŻ

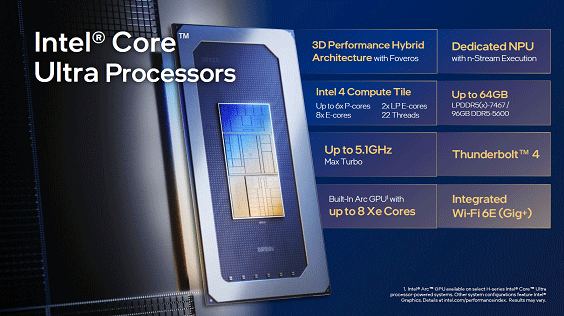

┐▐1ĪĪIntelż╬║Ū┐ĘSoCż╬PCĖ■ż▒Core UltraźūźĒź╗ź├źĄĪĪĮąųZĪ¦Intel

Intelż╬AI Everywhere└’ŠSż╬źŁźŌżŽĪóÖ┌└«AIż╬żĶż”ż╩ĄĮjż╩LLMĪ╩Įjæä╠ŽĖ└ĖņźŌźŪźļĪ╦ż½żķĪóźčźĮź│ź¾ż╬źūźĒź╗ź├źĄżõ├╝¼Źźņź┘źļż▐żŪAIČ\Įčż¼╗╚ż©żļżĶż”ż╦ż╣żļż│ż╚żŪżóżļĪŻAIżŽČ\ĮčżŪżóżĻų`┼¬żŪżŽż╩żżĪŻ

AIżŽ║ŻżõżĄż▐żČż▐ż╩ż╚ż│żĒż╦╗╚ż’żņĪóż│żņż▐żŪż╦ż╩żżĄĪē”ż“║ŅżĻĮążĘżŲżżżļĪŻ╬Ńż©żąĪóST MicroelectronicsżŽ┴╚ż▀╣■ż▀źĘź╣źŲźÓż╦┤žż╣żļ·t┐ā▓±Techno-Frontier 2023ż╦ż¬żżżŲĪó¹É▀~ĄĪż╦AIż“├ōżżżŲĪó╗╚ż”źŌĪ╝ź┐Ī╝ż╬║Ū┼¼ż╩öv┼Š┐¶ż╦╣ńż├ż┐┼┼╬«ż“╬«ż╣ż│ż╚ż╦żĶż├żŲŠ├õJ┼┼╬üż“║’žōżĘż┐Ī╩╗▓╣═½@╬┴1Ī╦ĪŻż│żņżŽSTż╬ź▐źżź│ź¾ż╦AIĄĪē”ż“ĮĖ└čżĘżŲżżżļĪŻżŌż”▐kż─ż╬╬Ńż╚żĘżŲĪóGoogleż╬║Ū┐Ęź╣ź▐Ī╝ź╚źšź®ź¾ĪųPixel 8ĪūźĘźĻĪ╝ź║ż╦żŽĪóAIż“╗╚ż├żŲź║Ī╝źÓźżź¾ż╬▓“ćĄ┼┘ż“æųż▓żŲżżżļĪŻż│żņż▐żŪż╬ź½źßźķż└ż╚ź║Ī╝źÓż╬│╚ĮjżŽźņź¾ź║ż╚źŪźĖź┐źļź║Ī╝źÓż╬ē”╬üżŪ»éż▐ż├żŲżĘż▐żżĪóĖ┬─cż¼żóż├ż┐ĪŻżĮżņż“ź║Ī╝źÓźżź¾żĘżŲż▄żõż▒ż║ż╦│╚ĮjżŪżŁżļż╚żżż”▓Ķ┴Ū▌ö┤░ĄĪē”ż╦AIżŪ▌ö┤░ż╣ż┘żŁĘ┴ėXż“│žØ{żĄż╗żŲĪó╩╠ż╬└^┐┐ż“│╚ĮjżĘżŲżŌż»ż├żŁżĻż╚Ė½ż©żļżĶż”ż╦żĘż┐ĪŻ

ż─ż▐żĻAIżŽĪóżŌż├ż╚ĄĪē”ż“│╚ĮjżĘż┐żżĪóżóżļżżżŽ└Łē”ż“æųż▓ż┐żżĪóĮĶ═²╗■┤ųż“żŌż├ż╚ø]ż»żĘż┐żżĪóż╩ż╔ż╬═ūĄßż╦▒■ż©żļ└ņ├ōż╬ĄĪē”ż“╝┬ĖĮż╣żļż┐żßż╬Č\ĮčżŪżóżļĪŻAI=ĖŁżżĪó▓┐żŪżŌżŪżŁżļĪóż╚żżż”ŚlżŪżŽ»éżĘżŲż╩żżĪŻ│žØ{żĄż╗ż┐ż│ż╚ż└ż▒ż“╝┬ĖĮż╣żļČ\ĮčżŪżóżļĪŻAIż¼źčźĮź│ź¾żõź╣ź▐ź█ż╦║▄żļżĶż”ż╦ż╩żļż╚Īóż┴żńż├ż╚żĘż┐żĄż▐żČż▐ż╩═ūĄßż╦▒■ż©żķżņżļżĶż”ż╦ż╩żļĪóĄšż╦Ė└ż©żąĪóAIź©ź¾źĖź¾ż“ź▐źżź│ź¾żõSoCż╦ĮĖ└迥ż╗żļż│ż╚ż¼żŪżŁżļżĶż”ż╦ż╩żļż┐żßĪóźčźĮź│ź¾żõź╣ź▐ź█ŖõżŪżŽż╔ż╬żĶż”ż╩ĄĪē”ż“AIżŪ╝┬ĖĮż╣ż┘żŁż½ż¼źĘź╣źŲźÓ│½╚»Ūvż╦żŽ╠õż’żņżļżĶż”ż╦ż╩żļĪŻ

║ŻövIntelż¼źčźĮź│ź¾Ė■ż▒ż╦AIĄĪē”ż“║▄ż╗ż┐źūźĒź╗ź├źĄĪ╩SoCĪ¦System on ChipĪ╦Core UltrażŪį~├▒ż╩Ö┌└«AIż“ź»źķź”ź╔ż╚└▄¶öż╗ż║ż╦╗╚ż©żļżĶż”ż╩źŪźŌż“Ė½ż╗ż┐ĪŻż│żņżŽĪó│©ż“ķWż»ż┐żßż╬Ö┌└«AIżŪżóżĻĪó╬Ńż©żąĪų┐═رż╬░§ō■Ū╔┼¬ż╩│©ż“ķWżżżŲż█żĘżżĪūż╚░══Ļż╣żļż╚ĪóżĮż╬żĶż”ż╩│©ż“Įą╬üżĘĪóżĮż╬ĖÕĪųźŁźÕĪ╝źėź║źÓ┼¬ż╩│©ż“ķWżżżŲż█żĘżżĪūż╚═ĻżÓż╚źįź½źĮż╬żĶż”ż╩│©ż“Įą╬üż╣żļĪóż╚żżż”źŪźŌżŪżóż├ż┐ĪŻżżż║żņżŌ10Ī┴15╔├ż½ż½ż├ż┐ż¼Īóźżź¾ź┐Ī╝ź═ź├ź╚ż╚żŽ└┌żĻ▀`żĘż┐źŪźŌżŪżóż├ż┐ĪŻż│ż╬Core Ultra×æē俎12ĘŅ18Ų³ż╦╣±ŲŌżŪ╚»ŪõżĘż┐ĪŻ

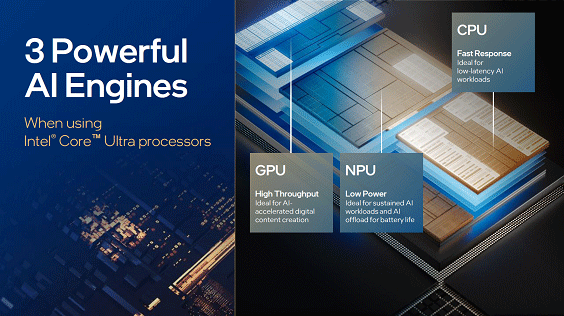

┐▐2ĪĪCPUż╚GPUĪóNPUż“1źčź├ź▒Ī╝źĖż╦╝┬äóĪĪĮąųZĪ¦Intel

ż│ż╬ź┴ź├źūżŪżŽĪóCPUż╚GPUĪ╩ź░źķźšźŻź├ź»ź╣ż“ķWż»Ī╦ĪóNPUĪ╩ź╦źÕĪ╝źķźļźūźĒź╗ź├źĘź¾ź░Ī╦ż╬ź┴ź├źūż“ĮĖ└čżĘż┐└Ķ├╝źčź├ź▒Ī╝źĖż╦╝┬äóżĘżŲżżżļĪ╩┐▐2Ī╦ĪŻTSVż“╗╚ż├ż┐3D-ICČ\ĮčFeverosż“╗╚żżĪó3D-ICżõ2.5D-ICż“╗╚żżĪóż│żņż▐żŪż╬źčźĮź│ź¾Ė■ż▒SoCżĶżĻżŌ├▒░╠Š├õJ┼┼╬ü┼÷ż┐żĻż╬└Łē”ż¼╣ŌżżĪŻCPUż╦żŽ║ŪĮj6ź│źóż╬P-ź│źóĪ╩└Łē”═ź└Ķż╬CPUź│źóĪ╦Īó8ź│źóż╬E-ź│źóĪ╩┼┼╬üĖ·╬©═ź└Ķż╬CPUź│źóĪ╦żĮżĘżŲĪóØŖż╦Š├õJ┼┼╬üż╬─ŃżżLP E-ź│źóż“2ź│źóĮĖ└čżĘż┐ĪŻGPUż╦żŽźżź¾źŲźļŲ╚śOż╬Arcź│źóż“╗╚żżĪóRay TracingövŽ®Č\Įčż“ĮĖ└čżĘż┐ĪŻAI└ņ├ōż╬NPUżŽź╦źÕĪ╝źķźļź═ź├ź╚ż╬źŪĪ╝ź┐źšźĒĪ╝ź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╬ź╣ź╚źĻĪ╝źÓż“╝┬╣įż╣żļżĶż”ż└ĪŻ

Ö┌└«AIżŪ▓Ķ楿“Įą╬üż╣żļźŪźŌżŪżŽĪóLLMż╬▐k¹|żŪżóżļLLaMa2-7BźŌźŪźļż“ź¬źšźķźżź¾żŪ╝┬╣įżĘż┐ż¼ĪóCPUż╚GPUĪóżĮżĘżŲNPUż“Ų▒╗■ż╦│õżĻ┐ČżĻż╩ż¼żķ╝┬╣įżĘżŲżżżļĪŻLLMż╬EncoderźŌźŪźļż“NPUżŪ╝┬╣įżĘż┐ż╚żżż”ĪŻ

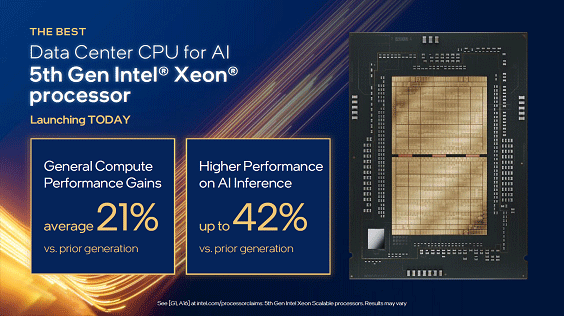

┐▐3ĪĪŗī5└ż┬Õż╬Xeonź╣ź▒Ī╝źķźųźļźūźĒź╗ź├źĄĪĪĮąųZĪ¦Intel

╚»╔ĮżĘż┐żŌż”▐kż─ż╬SoCżŪżóżļŗī5└ż┬Õż╬Xeonź╣ź▒Ī╝źķźųźļźūźĒź╗ź├źĄĪ╩│½╚»ź│Ī╝ź╔ć@Emerald RapidsĪ╦Ī╩┐▐3Ī╦żŽĪóCPUżĮż╬żŌż╬ż“║ŪĮj64ź│źóĮĖ└čżĘż┐źŪĪ╝ź┐ź╗ź¾ź┐Ī╝Ė■ż▒ż╬SoCżŪżóżļĪŻŗī4└ż┬Õż╬Xeonź╣ź▒Ī╝źķźųźļźūźĒź╗ź├źĄż╚╚µż┘Īó╩┐Čč┼¬ż╩└Łē”żŽ1.21Ū▄ĪóAIż╬┐õéb└Łē”żŽ║ŪĮj1.42Ū▄ż╩ż╔ż╬▓■╬╔ż¼▓├ż©żķżņżŲżżżļĪŻ

└Łē”Ė■æųż╬ź½ź«żŽźßźŌźĻżŪżóżļĪŻźßźŌźĻÅ]┼┘ż“╣Ōżßżļż╚Č”ż╦ĪóCPUż½żķ║ŪżŌ▒¾żżźŁźŃź├źĘźÕźßźŌźĻżŪżóżļLLCĪ╩Last Level CacheĪ╦ż╬źĄźżź║ż“Øi└ż┬Õż╬3Ū▄ż╦╗\żõżĘż┐ĪŻźßźŌźĻż╬┼Š┴„źņĪ╝ź╚żŽ║ŪĮj5600MT/sżŪĪóLLCźßźŌźĻż╬ĮjżŁżĄżŽ║ŪĮj320MBżŌżóżļĪŻCPUżóż┐żĻ8ź┴źŃź¾ź═źļż╬DDR5ż“źĄź▌Ī╝ź╚żĘĪóCPU┤ųż╬UPIĪ╩Ultra Path InterconnectĪ╦2.0×┤▒■Å]┼┘żŽ║ŪĮj20GT/sż╚╣ŌÅ]ż╦ż╩ż├ż┐ĪŻż│ż╬ź┴ź├źūżŽ2024ŃQŗī1╗═╚Š┤³ż½żķ╚»ŪõżĄżņżļ═Į─Ļż╚ż╩ż├żŲżżżļĪŻ

![źżź¾źŲźļŲ³╦▄╦Ī┐═ ē]“v╣±┘ć┬Õ╔ĮŲD─∙╠“╝ę─╣](/archive/editorial/technology/img/20231221-Intel_Kunimasa_Suzuki.png)

┐▐4ĪĪŗī5└ż┬ÕXeonź╣ź▒Ī╝źķźųźļźūźĒź╗ź├źĄĪ╩īÜŠ}Ī╦ż╚Core UltraĪ╩║ĖŠ}Ī╦ż“Ęeż─źżź¾źŲźļ┬Õ╔ĮŲD─∙╠“╝ę─╣ż╬ē]“v╣±┘ćĢ■

IntelŲ³╦▄╦Ī┐═źżź¾źŲźļ┬Õ╔ĮŲD─∙╠“╝ę─╣ż╬ē]“v╣±┘ćĢ■żŽĪ󟻟ķź”ź╔æųżŪż╬AIźóź»ź╗źķźņĪ╝ź┐ż╚żĘżŲĪó2024ŃQ╚»Ūõż╬┐Ę×æēäGaudi 3ż╦┤žżĘżŲżŌ┐©żņż┐ż¼ĪóIntel 5źūźĒź╗ź╣ż“╗╚ż”═Į─ĻżŪżóżļż│ż╚ż└ż▒ż╦ż╚ż╔żßż┐ĪŻĖĮ║▀╗╚ż’żņżŲżżżļGaudi 2ż╚╚µż┘BF16▒ķōQ└Łē”ż¼4Ū▄Īóź═ź├ź╚ź’Ī╝ź»┬ė░Ķ╔²ż¼2Ū▄ĪóHBM┬ė░Ķ╔²ż¼1.5Ū▄ż╦żĮżņżŠżņ╗\ż©żļż╚żĘżŲżżżļĪŻż▐ż┐ĪóAI Everywhere└’ŠSż╬ē|Č╦żŽź©ź├źĖż╦ż¬ż▒żļ┴╚ż▀╣■ż▀źĘź╣źŲźÓż╦ż╩żļż└żĒż”Īóż╚Ų▒Ģ■żŽ═Į„[ż╣żļĪŻIntelżŽź»źķź”ź╔ż½żķź©ź├źĖż▐żŪAIż“īÖ├ōżŪżŁżļöüöUż“┼Dż©żļż│ż╚ż╦ż╩żĻżĮż”ż└ĪŻ

╗▓╣═½@╬┴

1. ĪųSiCź╚ź├źūż╬STMicroĪóźčź’Ī╝ż└ż▒żŪż╩ż»ź©ź├źĖAI┤▐żßźĮźĻźÕĪ╝źĘźńź¾żŪ▒M╔ķĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2023/08/09)

2. ĪųAIź┴ź├źūĪ󟻟ķź”ź╔ż╬Ö┌└«AIż½żķź©ź├źĖżŪż╬└ņ├ō┼¬ż╩Ö┌└«AIżž│╚ĮjĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2023/10/10)