FPGAżŽĮjæä╠Žż½żķ├µĪóżĮżĘżŲŠ«æä╠Žż╬övŽ®ż▐żŪęŖ═ūżŽĮjżŁżż

Ų▒żĖFPGAźßĪ╝ź½Ī╝żŪżŌ┴└ż”ż┘żŁ▒■├ōż╦żĶż├żŲĪó╚ŠŲ│öüżžż╬═ūĄßż╚ĪóŲ│Ų■ż╣żļźĮźšź╚ź”ź©źóż¼µ£ż»░Ńż”ĪŻ║ŪŖZ╚»╔Įż╬żóż├ż┐3źßĪ╝ź½Ī╝ż╬┐Ę×æēäż¼×┤Š╚┼¬ż└ĪŻXilinxżŽźŽźżź©ź¾ź╔ż╬HPCżõź╣Ī╝źčĪ╝ź│ź¾źįźÕĪ╝ź┐ż╬żĶż”ż╩╣ŌÅ]▒ķōQż“┴└żżĪóLattice SemiconductorżŽź©ź├źĖAIż“┴└ż”ĪŻ╣±ŲŌżŪżŌźļź═źĄź╣żŽĪóāA╝²żĘż┐Dialogż╬żŌż─Š«æä╠ŽFPGAźėźĖź═ź╣ż“│½╗Žż╣żļĪŻ

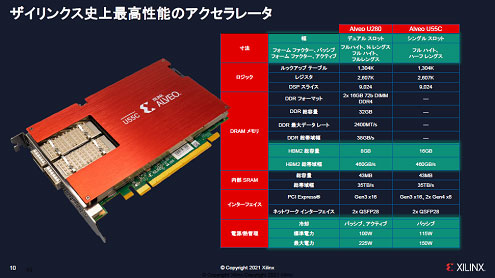

┐▐1ĪĪĮjżŁżĄ╚Š╩¼żŪŲ▒żĖ└Łē”ĪóŠ├õJ┼┼╬üż¼1/2ż╬źŽźżź©ź¾ź╔FPGAĪĪXlinx AlveoĪĪĮąųZĪ¦Xilinx

HPCĪ╩High Performance ComputingĪ╦ż╬╩¼╠ŅżŪżŽĪó╗@╠®ż╩źĘź▀źÕźņĪ╝źĘźńź¾ż“ż│żņż▐żŪżĶżĻżŌŠ»ż╩żżŠ├õJ┼┼╬üżŪ╣ŌÅ]ż╦▒ķōQż╣żļż│ż╚ż¼ĄßżßżķżņżŲżżżļĪŻź¬Ī╝ź╣ź╚źķźĻźóż╬╣±╬®Ė”ē|ĮĻCSIROĪ╩Commonwealth Scientific and Industrial Research OrganisationĪ╦żŪżŽ▒¦├Ķż½żķż╬┐«ęÄż“1km╩┐ä▌ż╬┼┌├Žż╦źóźņźżėXż╦13╦³1000±ś└▀ÅøżĘż┐źčźķź▄źķźóź¾źŲź╩żŪ£p┐«żĘĪó▒¦├Ķż╬ź╩źŠż“▓“£½żĘżĶż”ż╚ŲDżĻ┴╚ż¾żŪżżżļĪŻźóź¾źŲź╩ż½żķż╬źŪĪ╝ź┐ż“ĮĖ╠¾żĘĪó420±śż╬Xilinx Alveo U55Cż“├ōżżżŲĪóĮj╬╠ż╬ćĶ▒RźŪĪ╝ź┐ż“ĮĶ═²ż╣żļĪŻźšźŻźļź┐źĻź¾ź░ż╚ØiĮĶ═²ż╚żżż”Įjæä╠Žż╩▒ķōQź┐ź╣ź»ż“źĻźóźļź┐źżźÓżŪ╝┬╣įż╣żļż╚żżż”ĪŻ

Xilinxż¼Š}²Xż▒żŲżŁż┐FPGAżŽŠ’ż╦źŽźżź©ź¾ź╔ż╬żŌż╬żŪĪó║ŻövżŽźóź»ź╗źķźņĪ╝ź┐ź½Ī╝ź╔Ī╩┐▐1Ī╦ż╩ż¼żķĪó─╣żĄż““£═Ķ║Ū╣Ō└Łē”ż╬Alveo U280ż╬╚Š╩¼ż╦Š«żĄż»żĘż┐ĪŻż│ż╬ż│ż╚żŪĪóFPGAż╬═Ų╬╠ż╚żŌżżż”ż┘żŁźļź├ź»źóź├źūźŲĪ╝źųźļż“2Ū▄ż╬2308KĖ─ż“ź│ź¾źįźÕĪ╝ź┐ż╦┼ļ║▄żŪżŁżļżĶż”ż╦ż╩żļĪŻØŖż╦╣Ō╠®┼┘ż╬ź╣ź╚źĻĪ╝ź▀ź¾ź░ źŪĪ╝ź┐żõĪó╣Ō I/O ōQĮč▒ķōQĪóźėź├ź░źŪĪ╝ź┐╩¼└Žżõ AI źóźūźĻź▒Ī╝źĘźńź¾ż╩ż╔ż╬ź╣ź▒Ī╝źļ│╚Įjż“ØŁ═ūż╚ż╣żļĮjæä╠Žż╩▒ķōQ╠õ¼öż╦ØŖ▓ĮżĘż┐└▀╝Ŗż╚ż╩ż├żŲżżżļĪŻ

Alveo U55Cż╦żŽHBM2ż╬źßźŌźĻż“16GB┼ļ║▄żĘżŲż¬żĻĪó┴Ē┬ė░Ķ╔²żŽ460GB/sż╚ż╩żļĪŻŲ▒╝ężŪż│żņż▐żŪż╬║Ū╣Ōż└ż├ż┐Alveo U280ż╬╚Š╩¼ż╬ĮjżŁżĄż╩ż¼żķŲ▒┼∙└Łē”żŪĪóŠ├õJ┼┼╬üżóż┐żĻż╬└Łē”żŽż█ż▄2Ū▄ż╚ż╩ż├żŲżżżļĪŻ

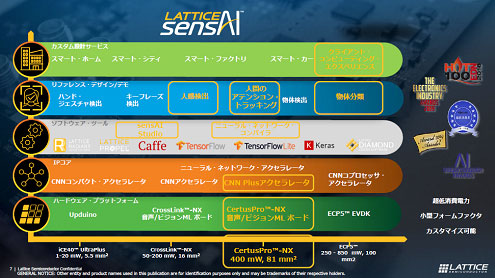

Latticeż╬FPGAżŽĪóź©ź├źĖAI▒■├ōż“┴└ż├ż┐żŌż╬ĪŻż╣żŪż╦SensAIż╚Ō}żųĪóAIźĮźšź╚ź”ź©źóź╣ź┐ź├ź»Ī╩┐▐2Ī╦ż“─¾ČĪżĘżŲżŁż┐ż¼ĪóŲ▒╝ęż╬FPGAżŪżóżļLattice NexusźĘźĻĪ╝ź║ż“┼ļ║▄żĘż┐│½╚»ź▄Ī╝ź╔ż╦AIż╬┐õébĄĪē”ż“ļmżß╣■żÓż│ż╚żŪĪóźµĪ╝źČĪ╝ż¼═▀żĘżżAIĄĪē”ż“╝┬ĖĮżŪżŁżļĪŻLatticeż╬FPGAżŽĪóXilinxżõIntelĪ╩ĄņAlteraĪ╦ż█ż╔źĒźĖź├ź»┐¶żŽ¾Hż»ż╩ż»ĪóżÓżĘżĒ─ŃŠ├õJ┼┼╬üżŪżóżļż│ż╚ż“ØŖ─╣ż╚żĘżŲżżżļĪŻ

┐▐2ĪĪźėźĖźńź¾AIż╦ØŖ▓ĮżĘż┐│½╚»ź─Ī╝źļSensAIĪĪĮąųZĪ¦Lattice Semiconductor

╬Ńż©żąźčźĮź│ź¾żõź╣ź▐Ī╝ź╚źšź®ź¾żŪźūźķźżźąźĘĪ╝╩▌ĖŅż╬ż┐żßĪó┴Ó║Ņ├µż╦┬Š┐═ż¼ŖZż┼żżżŲż»żļż╚śOŲ░┼¬ż╦▓ĶĀCż“ż▄ż½ż╣ĄĪē”ż“└▀ż▒ż┐żĻĪó┴Ó║Ņż╗ż║ż╦£å└■ż¼żĮżņżŲżżżļż╚ĪóźŪźŻź╣źūźņźżż“░┼ż»żĘżŲźąź├źŲźĻÖæ╠┐ż“äPżążĘż┐żĻż╣żļż│ż╚ż¼▓─ē”ż╦ż╩żļĪŻ

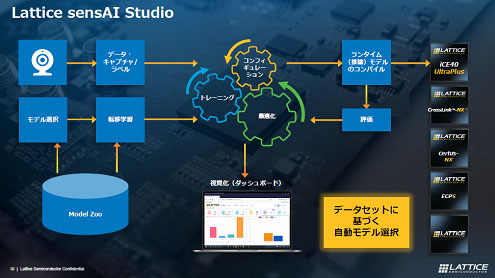

Lattice SensAI Studioż“╗╚ż├żŲĪóAIż“ļmżß╣■żÓŠņ╣ńĪ󟻟ķź”ź╔ż╩ż╔ż½żķ│žØ{║čż▀ż╦źŪĪ╝ź┐żõźŌźŪźļż“┬ō┘IżĘĪóśO╩¼ż╬▒■├ōż╦╣ńż”żĶż”ż╦┼ŠöĪ│žØ{żĄż╗ĪóśO╩¼ż╬▒■├ōż╬źŪĪ╝ź┐ż“ŲDżĻ╣■ż▀Īóź│ź¾źšźŻź«źÕźņĪ╝źĘźńź¾ĪóżĮżĘżŲį~├▒ż╩ź╚źņĪ╝ź╦ź¾ź░ż“╣įżżĪóAIż╬║Ū┼¼▓Įż“┐▐żļĪŻż│ż╬▐kŽóż╬Ų░║Ņż“▓─£å▓Įż╣żļSensAIż╬ź└ź├źĘźÕź▄Ī╝ź╔żŪ│╬Ū¦żŪżŁżļĪ╩┐▐3Ī╦ĪŻ

┐▐3ĪĪź»źķź”ź╔ż╬│žØ{źŪĪ╝ź┐ż½żķźĮźšź╚ź”ź©źóż“öĪ┐óżĘżŲAIź┴ź├źūż“║Ū┼¼▓ĮĪĪĮąųZĪ¦Lattice Semiconductor

│žØ{║čż▀ż╬źŪĪ╝ź┐żŽĪó╬Ńż©żąTensorFlowż╬źšźņĪ╝źÓź’Ī╝ź»ż½żķAIźŪĪ╝ź┐ż“Ęeż├żŲż»żļŠņ╣ńżŽĪóTFźŪĪ╝ź┐ż“TFLiteźŪĪ╝ź┐ż╦╩č┤╣żĘĪ󿥿ķż╦C++ź│ź¾źąĪ╝ź┐żŪC++Ė└Ėņż╬╩č┤╣żĘż┐ĖÕżŪĪóCPUż╦źĮźšź╚ź”ź©źóż“┴╚ż▀╣■żÓż┐żßż╬źĮźšź╚ź”ź©źó│½╚»ź─Ī╝źļLattice Propelż“╗╚ż├żŲźūźĒź░źķźÓż“║Ņ└«ĪóźŪźąź├ź░żõJTAGĖĪØhż╩ż╔ż“ĘążŲĪóFPGAźŽĪ╝ź╔ź”ź©źóż╦ļmżß╣■żÓĪŻżĮż╬Šņ╣ńż╬źūźĒź╗ź├źĄż╚żĘżŲRISC-Vź│źóż“├ōżżżļĪŻLatticeż╬FPGAż╦żŽźūźĒź░źķźÓ▓─ē”ż╩źļź├ź»źóź├źūźŲĪ╝źųźļż└ż▒żŪżŽż╩ż»ĪóĄĪ│Ż│žØ{└ņ├ōövŽ®Ī╩MAC▒ķōQ▀_+źßźŌźĻĪ╦żõźėźĖźńź¾ĮĶ═²övŽ®ż╩ż╔ż“ĮĖ└čżĘżŲżżżļĪŻ

Latticeż╦żĶżļż╚Īó╩Ż┐¶ż╬رöüż“─ŃŠ├õJ┼┼╬üżŪ╩¼╬ÓżŪżŁżļżĶż”ż╦ż╩żļĪŻ33fpsĪ╩źšźņĪ╝źÓ/╔├Ī╦żŪ224Ī▀223▓Ķ┴Ūż╬źšźļź½źķĪ╝źŪźŻź╣źūźņźżż½żķ╩¼╬Óż╣żļŠņ╣ńżŪżŌĪóFPGAż╬CertusPro-NXĪ╩NexusĪ╦ż“╗╚ż├żŲŠ├õJ┼┼╬üżŽ400mWżŪ║čżÓż╚żżż”ĪŻ

╣±ŲŌżŪżŌĪóźļź═źĄź╣ź©źņź»ź╚źĒź╦ź»ź╣żŽĪóDialog Semiconductorż“āA╝²żĘż┐ż│ż╚ż╦żĶż├żŲĪóFPGAźėźĖź═ź╣ż“įuż┐ĪŻDialogżŽĪó2017ŃQż╦Š«æä╠ŽFPGAĪųGreenPAKĪūż“─¾ČĪż╣żļSilego╝ęż“āA╝²żĘżŲżżżļĪŻSilegoż╬FPGAżŽĪó1KżóżļżżżŽ2Kµć┼┘ż╬źļź├ź»źóź├źūźŲĪ╝źųźļĪ╩LUTĪ╦ż“ĮĖ└čżĘżŲż¬żĻĪó5000ź▓Ī╝ź╚░╩▓╝ż╬źĒźĖź├ź»ż“×┤ō■ż╚żĘżŲżżżļĪŻ

║ŻövĪó│½╚»┤─ČŁżŌ─¾ČĪżĘĪóVerilogź┘Ī╝ź╣ż╬HDLźŌĪ╝ź╔ż╚ĪóövŽ®┐▐ź┘Ī╝ź╣ż╬ź▐ź»źĒź╗źļźŌĪ╝ź╔ż╬2¹|╬Óż“─¾ČĪż╣żļĪŻŠ«æä╠Žż╬źĒźĖź├ź»ż“┴╚żÓźĘĪ╝ź¾ż╚żĘżŲżŽĪóź┘Ī╝ź╣ż╚ż╩żļźūźĒź╗ź├źĄżŽ╩čż©ż║ż╦ĄĪē”ż“źŽĪ╝ź╔ź”ź©źóżŪ╝{▓├ż╣żļŠņ╣ńżõĪóź▄Ī╝ź╔ż╦ÜgżķżążļźŪźŻź╣ź»źĻĪ╝ź╚żõCMOSźĒźĖź├ź»ż╩ż╔ż“┼D═²ż╣żļŠņ╣ńż╩ż╔ż¼żóżļĪŻ┴T│░ż╚ęŖ═ūżŽĮjżŁż»Īóż┴żńż├ż╚żĘż┐ĮĖ└čż¼ØŁ═ūż╩övŽ®Ė■ż▒ż╦GreenPAKżŽ10▓»Ė─░╩æųż╬Įą▓┘╝┬└ėż¼żóżļĪŻ

╗▓╣═½@╬┴

1. Īų┤ļČ╚āA╝²ż╬┴ĻŠĶĖ·▓╠ż“2ŃQ░╩ŲŌż╦┐āżĘż┐DialogĪūĪóź╗ź▀ź│ź¾ź▌Ī╝ź┐źļ (2019/05/23)