XilinxĪóNoCŪ█└■Č\Įčż╚źžźŲźĒźūźĒź╗ź├źĄżŪ┼┼╬üĖ·╬©ż╬╬╔żżSoCż“│½╚»

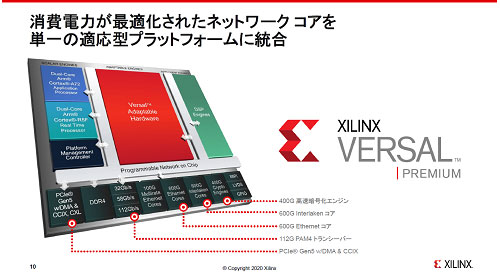

XilinxżŽFPGAż╦żĶżļź└źżź╩ź▀ź├ź»ż╦║Ų╣Į└«▓─ē”ż╩źŽĪ╝ź╔ź”ź©źóövŽ®ż½żķCPUż╦żĶżļźĮźšź╚ź”ź©źóŗēäĪ󿥿ķż╦żŽAIĄĪē”ż▐żŪżŌ┼ļ║▄żĘż┐ACAPĪ╩Adaptive Compute Acceleration PlatformĪ╦źūźķź├ź╚źšź®Ī╝źÓż“╚»╔ĮżĘżŲ░╩═ĶĪóżĮż╬×æēäż╚żĘżŲVersalźĘźĻĪ╝ź║ż“╝ĪĪ╣ż╚ĮążĘżŲżżżļĪŻż│ż╬ż█ż╔Versalźūźņź▀źóźÓż╚Ō}żųź╗źŁźÕźóż╩╣ŌÅ]ź═ź├ź╚ź’Ī╝ź»ż╦Ė■ż▒ż┐×æēäĪ╩┐▐1Ī╦ż“╚»╔ĮżĘż┐ĪŻ

┐▐1ĪĪź═ź├ź╚ź’Ī╝ź»ź╣źżź├ź┴ĄĪē”ż“äė▓ĮżĘż┐Versal PremiumĪĪĮąųZĪ¦Xilinx

ż│ż╬SoCż╬┴└żżżŽĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żõź│źó┤├ŽČ╔ż╬żĶż”ż╦ĪóźĘźĻźóźļźŪĪ╝ź┐ż“╣ŌÅ]ż╦└┌żĻü÷ż©żķżņĪóżĘż½żŌź╗źŁźÕźóż╦żĘż┐ż│ż╚ĪŻ5G╗■┬Õż╦ż╩żļż╚Īó├»żŪżŌĄżĘ┌ż╦ź╣ź▐ź█ż½żķźėźŪź¬▒Ū楿“ź└ź”ź¾źĒĪ╝ź╔ż└ż▒żŪżŽż╩ż»źóź├źūźĒĪ╝ź╔ż╣żļż┐żßĪó┤├ŽČ╔żŪżŽżĮż╬ź╚źķźšźŻź├ź»ż¼ĮjżŁż»╗\ż©żļż┐żßźĘźĻźóźļźŪĪ╝ź┐ż“╣ŌÅ]ź╣źżź├ź┴ź¾ź░żĘż╩ż▒żņżąż╩żķż╩żżĪŻż│żņż▐żŪż╬100GbpsżŪżŽź│źó┤├ŽČ╔żŪżŽ×┤▒■żŪżŁż╩ż»ż╩żļĪŻż│ż╬ż┐żß400Gbpsżžż╬ØŹ×óż¼ĖĮ╝┬┼¬ż╦ż╩żļĪŻżĄżķż╦żĮż╬└Ķż╦żŽ800Gbpsż¼┌ģżķżņżļĪ╩┐▐2Ī╦ĪŻ

┐▐2ĪĪź╗źļźķĪ╝ź═ź├ź╚ź’Ī╝ź»ż╬┤├ŽČ╔ż╚żĘżŲĪóźóź»ź╗ź╣ÅUż½żķź│źó┤├ŽČ╔ż▐żŪµ£żŲż╬źņźżźõĪ╝ż“ź½źąĪ╝żŪżŁżļĪĪĮąųZĪ¦Xilinx

┐Ę×æēäVersalźūźņź▀źóźÓż╬ØŖ─╣żŽĪóź│ź═ź»źŲźŻźėźŲźŻż╚ź╗źŁźÕźĻźŲźŻź│źóż“ĮĖ└čżĘżŲź═ź├ź╚ź’Ī╝ź»ĄĪē”ż“äė▓ĮżĘż┐ż│ż╚żŪżóżļĪŻĖ„źšźĪźżźąż½żķż╬źŪĪ╝ź┐żŌźĄź▌Ī╝ź╚żĘżŲż¬żĻĪóCPUż╚FPGAĪóDSPż“żĮżņżŠżņĮĖ└čżĘżŲżżżļĪŻżĮżņżŠżņż¼3ż─ż╬ź©ź¾źĖź¾ż╚Ō}żųĄĪē”ż“├┤┼÷żĘżŲżżżļĪŻ

CPUż“├µ┐┤ż╦żĘż┐▒ķōQĪ”öUĖµż╬źĮźšź╚ź”ź©źóżŪĮĶ═²ż╣żļź╣ź½źķź©ź¾źĖź¾(┐▐1ż╬║Ėæų)ĪóFPGAżŪ╣źżŁż╩źŽĪ╝ź╔ź”ź©źóövŽ®ż“╣Į└«żŪżŁżļźóź└źūź┐źųźļź©ź¾źĖź¾(┐▐1ż╬┐┐ż¾├µż╬śĘżżŗ╩¼)ĪóżĮżĘżŲDSPżŽ▒ķōQźėź├ź╚╔²ż“ź╣źķźżź╣żĘż┐├▒╗@┼┘ż╚ź▀ź»ź╣╗@┼┘ż╬źżź¾źŲźĻźĖź¦ź¾ź╚ź©ź¾źĖź¾Ī╩┐▐1ż╬Ū÷£uż╬ŗ╩¼Ī╦Īóż╚żżż”3¹|╬Óż╬ź©ź¾źĖź¾ż“ĮĖ└čżĘżŲżżżļĪŻ

DSPżŽĖĄĪ╣ĪóMACĪ╩└čŽ┬▒ķōQĪ╦└ņ├ōż╬ź▐źżź»źĒźūźĒź╗ź├źĄżŪżóżļĪŻ“£═ĶżŽ▒ķōQ╗@┼┘ż“æųż▓żļż┐żßĪó├▒╗@┼┘(32źėź├ź╚)ż½żķŪ▄╗@┼┘(64źėź├ź╚)ż╦║┘ż½ż»żĘĪóżĘż½żŌ╔ŌŲ░Š«┐¶▒ķōQż“╣įż©żļżĶż”ż╦żĘżŲżżż┐ĪŻ║ŻövżŽĄĪ│Ż│žØ{ż╬MACż“╩┬š`ż╦¾H┐¶╩┬ż┘żŲż¬żĻĪó┼D┐¶▒ķōQż└ż▒żŪĪó8źėź├ź╚Īó16źėź├ź╚Īó32źėź├ź╚ż╚ź▀ź├ź»ź╣ż╬╗@┼┘ż“├ō┴TżĘż┐ĪŻ

ż│żņżķ3¹|╬Óż╬╝ń═ūź│źóż╦▓├ż©Īó╣ŌÅ]ż╬SerDesĪ╩źĘźĻźóźķźżźČ/źŪźĘźĻźóźķźżźČĪ╦ż╚żĘżŲż╬źĘźĻźóźļźżź¾ź┐Ī╝źšź¦źżź╣żŪżóżļ600Gbpsż╬Interlakenź│źóĪó600Gbpsż╬Ethernetź│źóĪó112Gbpsż╬PAM4ź╚źķź¾źĘĪ╝źąĪóPCIeż╬Gen5Ī╩DMA¤²żŁĪ╦ż╩ż╔źŽĪ╝ź╔ź’źżźõĪ╝ź╔övŽ®ż“ĮĖ└čżĘż┐ĪŻ

║Żövż╬─_═ūż╩Č\Į迎ĪóNoCĪ╩Network on ChipĪ╦Č\ĮčżŪżóżĻĪóNoCżŪµ£żŲż╬ź©ź¾źĖź¾ż“ż─ż╩ż«─╠┐«żŪżŁżļżĶż”ż╦żĘż┐ż│ż╚ż└ĪŻźŁźŃź├źĘźÕźßźŌźĻż“ĘQź│źóżŪČ”Ń~ż╣żļż┐żßż╬ź│źęĪ╝źņź¾źĘżŌ×óż©żŲżżżļĪŻ▓├ż©żŲĪóŲ■Įą╬üźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż½żķźŪĪ╝ź┐ż“░┼ęÄ▓ĮżĘżŲĮą╬üż╣żļż┐żßż╬400Gbpsż╬╣ŌÅ]░┼ęÄ▓Įź©ź¾źĖź¾żŌĮĖ└čżĘĪó┴„żļż┘żŁźŪĪ╝ź┐ż╬ź╗źŁźÕźĻźŲźŻż“æųż▓ż┐ĪŻ

“£═Ķż╬FPGAżŪżŽĪóźĒźĖź├ź»ż╚źķź”źŲźŻź¾ź░(Ū█└■└▄¶ö)ż╦20╦³LUTĪ╩Look-up TableĪ╦ż“╗╚ż├żŲżżż┐ĪŻ║ŻövżŽLUTż“╗╚ż’ż║ż╦źżź¾ź┐Ī╝źšź¦Ī╝ź╣övŽ®ż“źŽĪ╝ź╔ź’źżźõĪ╝ź╔▓ĮżĘż┐ż│ż╚ż╦▓├ż©ĪóNOCź╣źżź├ź┴Č\Įčż╦żĶż├żŲĪó╠ĄŠGż╩┼┼╬üż“═Ņż╚żĘż┐ĪŻż│żņż╦żĶż├żŲĪóXilinx╝ęż╬ż│żņż▐żŪż╬×æēä16nmż╬Virtex Ultrascale+2Ė─┴╚ż╚╚µż┘Īó40%ż╬Š├õJ┼┼╬üżŪ800Gbpsż╬DCIź╣źļĪ╝źūź├ź╚ż“╝┬ĖĮżŪżŁż┐ĪŻ

┐▐3ĪĪĘQ¹|AIż╦×┤żĘżŲźßźŌźĻ┬ė░Ķ╔²ż¼╣Łż¼żĻ╣ŌÅ]ż╦ĪĪĮąųZĪ¦Xilinx

ż▐ż┐AIĄĪē”ż“╝┬╣įż╣żļŠņ╣ńżŪżŌĪó“£═Ķż╬GPUżõCPUżŪż╬▒ķōQżĶżĻżŌÅ]żż(┐▐3)ĪŻResNet50żŪ224Ī▀224ż╬▓ĶćĄŪ¦╝▒Ī”╩¼╬ÓżŪżŽĪóGPUż╬1.6Ū▄Ī┴2.3Ū▄ĪóYolov2Ī╩608Ī▀608Ī╦ż╬رöüĖĪē¶żŪżŽGPUż╬4.6Ū▄Ī┴7.7Ū▄Īó╣ŌÅ]ż╦ż╩ż├ż┐ĪŻż▐ż┐Īó░█Š’ĖĪē¶ż╦╗╚ż’żņżļAIĪ╩Random ForestĪ╦żŪżŽIntelż╬Xeonż╬65Ū▄ż╚żżż”±T▓╠ż“įużŲżżżļĪŻ

×æēäźĘźĻĪ╝ź║żŽĪóźĘź╣źŲźÓźĒźĖź├ź»ź╗źļż¼1.6Mż╬VP1102ż½żķŲ▒7.4Mż╬VP1082ż▐żŪ┬Ęż©żŲżżżļĪŻżĮżņż╦żĶż├żŲSoCźčź├ź▒Ī╝źĖźĄźżź║ż¼35 mmĪ▀35mmż╚Īó4ż─ż╬źĘźĻź│ź¾ź┴ź├źūż“┼ļ║▄żĘżŲżżżļ65mmĪ▀65mmż¼żóżļĪŻźčź├ź▒Ī╝źĖź¾ź░ż╦żŽĪóTSMCż╬SSITĪ╩Stacked Silicon Interconnect TechnologyĪ╦ż╚CoWoSĪ╩Chip on Wafer on SiliconĪ╦Č\Įčż“╗╚ż├ż┐ż╚źėźŪź¬▓±Ė½żŪĮęż┘żŲżżżļĪŻ

XilinxżŽĪóCPUźĮźšź╚ź”ź©źó│½╚»ż╚AIźķźżźųźķźĻżõ│½╚»┤─ČŁĪ╩CaffeżõTensorFlowĪóPyTorchĪ╦ż“┼²╣ńżĘż┐Vitis│½╚»źŁź├ź╚ż“ż╣żŪż╦─¾ČĪżĘżŲż¬żĻĪóźŽĪ╝ź╔ź”ź©źóäh▓┴źŁź├ź╚żŌ20ŃQĖÕ╚Šż╦─¾ČĪż╣żļ╝Ŗ▓Ķż└ĪŻ