Western DigitalĪóźķźżź╗ź¾ź╣źšźĻĪ╝ż╬CPUź│źóRISC-Vżžµ£ĀC└┌żĻü÷ż©

Western Digitalż¼śO╝ężŪ└▀╝ŖżĘżŲżżżļICż╦ĮĖ└迥żņżŲżżżļCPUź│źóż““£═Ķż╬ź│źóż½żķĪóźķźżź╗ź¾ź╣źšźĻĪ╝ż╬RISC-Vź│źóĪ╩╗▓╣═½@╬┴1Ī╦ż╦µ£ĀC┼¬ż╦└┌żĻü÷ż©żŲżżż»Īóż╚Ų▒╝ęCTOż╬Martin FinkĢ■(┐▐1)ż¼Ėņż├ż┐ĪŻ“£═Ķż╬ArmżõMIPSż╩ż╔ż╬CPUź│źóżŽźķźżź╗ź¾ź╣╬┴ż¬żĶżėźĒźżźõźļźŲźŻ╬┴ż¼ż½ż½żļĪŻRISC-VżŽUC Berkeleyż¼│½╚»żĘż┐ź│źóĪŻ

┐▐1ĪĪWestern Digital CTOż╬Martin FinkĢ■

Western DigitalżŽ┼ņėøźßźŌźĻż╬źūźĒź╗ź╣Č©╬ü▓±╝ęż╚żĘżŲŃ~ć@ż└ż¼ĪóĖĄĪ╣żŽHDDĪ╩źŽĪ╝ź╔źŪźŻź╣ź»ź╔źķźżźųĪ╦ż“Ö┌ŠÅ╚╬ŪõżĘżŲżŁż┐ĪŻ2016ŃQż╦┼ņėøż╚Č”Ų▒żŪNANDźšźķź├źĘźÕźßźŌźĻż“│½╚»żĘżŲżżż┐SanDiskż“āA╝²żĘĪóŲ³╦▄ż╬╚ŠŲ│öüČ╚─cżŪ▐k╠÷Ń~ć@ż╦ż╩ż├ż┐ĪŻ║ŻżŽSSDĪ╩╚ŠŲ│öüźŪźŻź╣ź»Ī╦żŌÖ┌ŠÅżĘżŲż¬żĻĪóHDDż╚SSDż╬╬ŠöĄżŪźėźĖź═ź╣ż“·t│½żĘżŲżżżļĪŻHDDżõSSDżŪżŽĪóŲ╔ż▀ĮążĘź┴źŃź¾ź═źļ├ōż╬ASICżõNANDźšźķź├źĘźÕź│ź¾ź╚źĒĪ╝źķż╩ż╔ż╬└ņ├ōż╬ICż¼ØŁ═ūżŪĪóWDżŽż│żņż▐żŪ10▓»Ė─ż╬CPUź│źóż“┼ļ║▄żĘż┐ICż“Įą▓┘żĘżŲżŁż┐ż╚żżż”ĪŻ║ŻĖÕżŌź╣ź╚źņĪ╝źĖźŪźąźżź╣żŽĪóż▐ż╣ż▐ż╣äPżėżŲżµżŁĪó╗■┤³żŽ£½│╬ż╦Ė└ż’ż╩ż½ż├ż┐ż¼Īóżżż║żņ20▓»Ė─ż╦├Żż╣żļż└żĒż”ż╚FinkĢ■żŽĮęż┘żŲżżżļĪŻ

WDż¼RISC-Vź│źóż╦└┌żĻü÷ż©żĶż”ż╚żĘżŲżżżļŪžĘ╩ż╦żŽĪóĮj╬╠ż╬źŪĪ╝ź┐ż“░Ęż”╗■┬Õż¼═Ķżļż│ż╚ż“„[─ĻżĘżŲżżżļż│ż╚ż¼żóżļĪŻż│żņż▐żŪż╬└Lź┘Ī╝ź╣ż╬ĄŁŹ{źŪĪ╝ź┐ż½żķĪó┼┼╗ęźßĪ╝źļż╬─╠┐«źŪĪ╝ź┐ż╦┬Õż’żĻĪóż│żņż½żķżŽźŪĪ╝ź┐ż“īÖ├ōżĘżŲÖ┌ŠÅżõÖ┌īÖż╬Ė·╬©ż“æųż▓ż┐żĻĪóźŪĪ╝ź┐ż“źėźĖź═ź╣ż╚żĘżŲź▐ź═ź┐źżź║żĘż┐żĻż╣żļż│ż╚ż╦ż╩żļĪŻź╣ź╚źņĪ╝źĖżõźßźŌźĻżŽ║ŻĖÕżŌż▐ż╣ż▐ż╣ØŁ═ūż╦ż╩żļż│ż╚żŽ┤ų░Ńżżż╩żżĪŻWDż╬ź╣ź╚źņĪ╝źĖźŪźąźżź╣├ōź│ź¾ź╚źĒĪ╝źķASICżŽżóż»ż▐żŪżŌ╝ęŲŌĖ■ż▒ż╬ź┴ź├źūżŪżóżĻĪóIPź│źóżŌź┴ź├źūżŌ│░╚╬żĘż╩żżĪŻ×æļ]żŽTSMCż╚GlobalFoundriesż╦░č▓mżĘżŲżżżļĪŻ

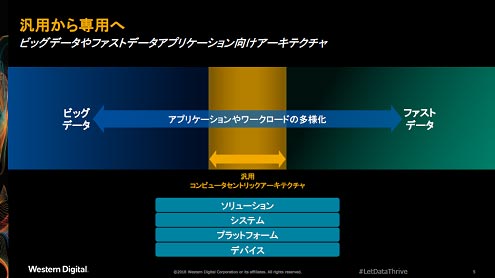

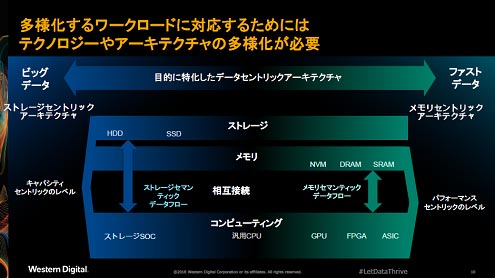

WDżŽźŪĪ╝ź┐ż“2¹|╬Óż╦╩¼ż▒ĪóĮj╬╠ż╬źėź├ź░źŪĪ╝ź┐ż╚Īó╣ŌÅ]ż╦źóź»ź╗ź╣żĘż┐żżźšźĪź╣ź╚źŪĪ╝ź┐Ī╩Fast dataĪ╦ż╦·t│½żĘżŲżżż»ż╚żĘż┐ĪŻż│żņż▐żŪżŽĪóź│ź¾źįźÕĪ╝ź┐źĘź╣źŲźÓż╬źßźŌźĻ│¼┴žż½żķ╣Į└«żĄżņżļź│ź¾źįźÕĪ╝ź┐ź╗ź¾ź╚źĻź├ź»ż╩źóĪ╝źŁźŲź»ź┴źŃżŪżóż├ż┐ż¼Īóż│żņż½żķżŽŲ¾ż─ż╬╬ŠČ╦├╝ż╬źßźŌźĻ▒■├ōżžż╚╣Łż¼ż├żŲżżż»ż╚ż╣żļ(┐▐2)ĪŻ

┐▐2ĪĪźŪĪ╝ź┐żŽ└@├ōż½żķĪóĮjæä╠ŽĪ”╣ŌÅ]ż╬╬ŠČ╦├╝ż╦·t│½żĄżņżŲżżż»ĪĪĮąųZĪ¦Western Digital

ż│żņż“FinkĢ■żŽĪóŠĶżĻرż╦╬Ńż©żŲĪó└@├ōźóĪ╝źŁźŲź»ź┴źŃż└ż╚4ź╔źóź╗ź└ź¾ż╬żĶż”ż╩żŌż╬żŪĪóźėź├ź░źŪĪ╝ź┐żŽĮjĘ┐▓▀ر═ó┴„ļ`żõ▓▀رš`┘Zż└ż╚żĘĪóźšźĪź╣ź╚źŪĪ╝ź┐żŽźĒź▒ź├ź╚żõźčĪ╝źĮź╩źļźĖź¦ź├ź╚ĄĪĪó┐Ęäō└■ż╬żĶż”ż╩żŌż╬ż└ż╚żĘż┐ĪŻż─ż▐żĻżĄż▐żČż▐ż╩ŠĶżĻرż¼Č”┘TżĘżŲżżżļżĶż”ż╦ź╣ź╚źņĪ╝źĖźŪźąźżź╣żŌ“£═Ķż╬└ņ├ōż╬HDDżõSSDż½żķźėź├ź░źŪĪ╝ź┐żõźšźĪź╣ź╚źŪĪ╝ź┐ż╦Ė■żżż┐ź╣ź╚źņĪ╝źĖżžż╚·t│½żĄżņżŲżżż»ż╚żĘżŲżżżļĪŻ│╬ż½ż╦ĪóČŌ═╗▌xŠņżŪżŽHDDżŪżŽęÆż╣ż«żŲ╣ŌÅ]ŲD░·ż╦Ė■ż½ż╩żżż½żķż╚żĘżŲSSDżžĖ■ż½ż├żŲżżżļż¼Īóµ£żŲSSDż╬┬Õż’żļż’ż▒żŪżŽż╩żżĪŻĮj╬╠ż╬źŪĪ╝ź┐żŽHDDżõźŪźĖź┐źļźŲĪ╝źūż╬öĄż¼╩▌┘Tż╦Ė■żżżŲżżżļĪŻ

źšźĪź╣ź╚źŪĪ╝ź┐żŽĪóź╣ź╚źņĪ╝źĖ╚ŠŲ│öüżŪżŽż╩ż»źßźŌźĻż╚żĘżŲĪó└õż©ż║Į±żŁ┤╣ż©żļRAMż“„[─ĻżĘżŲżżżļĪŻDRAMĪóSRAMĪó╔įĦ╚»└ŁRAMż╩ż╔ż¼źšźĪź╣ź╚źŪĪ╝ź┐ż“ܦż©żļ(┐▐3)ĪŻż│ż”żżż├ż┐╣ŁżżšJ░Žż╬ĪųźŪĪ╝ź┐ź╗ź¾ź╚źĻź├ź»ż╩źóĪ╝źŁźŲź»ź┴źŃĪūż¼ż│żņż½żķż╬┐ʿʿżź│ź¾źįźÕĪ╝ź┐źĘź╣źŲźÓż“║Ņżļż└żĒż”ż╚ż▀żŲżżżļĪŻ

┐▐3ĪĪź╣ź╚źņĪ╝źĖżŽźėź├ź░źŪĪ╝ź┐żžĪóźßźŌźĻżŽźšźĪź╣ź╚źŪĪ╝ź┐żžĪĪĮąųZĪ¦Western Digital

┼÷ĀCż╬▒■├ōż╚żĘżŲĪóźėź├ź░źŪĪ╝ź┐ż╦żŽ╩¼└ŽżõĄĪ│Ż│žØ{ż╦╗╚ż’żņĪóźšźĪź╣ź╚źŪĪ╝ź┐żŽźųźĒź├ź»ź┴ź¦Ī╝ź¾żõź╗źŁźÕźĻźŲźŻĖĪĮąĪóźżź┘ź¾ź╚┴Ļ┤žż╩ż╔ż╬▒■├ōż“„[─ĻżĘżŲżżżļĪŻź│ź¾źįźÕĪ╝ź┐źĘź╣źŲźÓż“ż│żņż½żķ│╚─źżĘżŲżżż»ż”ż©żŪĪóĪųź¬Ī╝źūź¾└ŁĪūż¼ØŁ═ūż╚ż▀żŲż¬żĻĪóCPUź│źóż╚żĘżŲżŽ└@├ōż╬IntelżõArmżŪżŽż╩żżĪóŗī3ż╬ź│źóżŪ░ķżŲżŲżżż»Īóż╚╣═ż©żŲżżżļĪŻRISC-Vż╬źčĪ╝ź╚ź╩Ī╝źĘź├źūż╬┴╚“Eż╚żĘżŲĪóLinuxżõTensorFlowĪóHadoopż╩ż╔ż╬├─öüż¼żżżļĪŻ

źķźżź╗ź¾ź╣źšźĻĪ╝ż╬RISC-VżŽĮj╬╠Ī”╣ŌÅ]ż╬└ņ├ō┼¬ż╩CPUźóĪ╝źŁźŲź»ź┴źŃż╚żĘżŲ╗╚ż’żņżļżŌż╬żŪżóżĻĪó└@├ōż╬źóĪ╝źŁźŲź»ź┴źŃż╦ż╚ż├żŲ┬Õż’żļżŌż╬żŪżŽż╩żżĪóż╚FinkĢ■żŽĖ½żŲżżżļĪŻ╬Ńż©żąĪóĄĪ│Ż│žØ{żõ╩¼└ŽżŪżŽźūźĒź╗ź├źĄż“źŪĪ╝ź┐ż╬ŖZż»ż╦Åøż»ĪŻż│żņż▐żŪżŽźŪĪ╝ź┐ż“źūźĒź╗ź├źĄż╬ŖZż»ż╦Åøż»żĶż”ż╦żĘżŲżŁż┐ĪŻźŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░Ė■ż▒ż╬AIź┴ź├źūżŪżŽĪó1ź┴ź├źūŲŌż╦¾H┐¶ż╬AIźųźĒź├ź»ż“╣Į└«żĘĪóżĮż╬ĘQAIźųźĒź├ź»żŽCPUż╚źßźŌźĻż“ŖZż»ż╦Ū█Åøż╣żļźņźżźóź”ź╚ż¼¾HżżĪŻź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»żŪżŽĪóźŪĪ╝ź┐Ī▀─_ż▀ż╬╝ŖōQż“╩┬š`ż╦ź▐ź├źĘźųź│źóżŪ╣įż”ż│ż╚ż¼¾Hżżż½żķż└ĪŻ║ŻĖÕż╬AI╔ߥ┌ż╦Ė■ż▒ż┐└ņ├ōź┴ź├źūż╦żŽRISC-Vż¼Ė■ż»ż╚ż▀żŲżżżļĪŻ

UC Berkeleyż¼RISC-Vż“│½╚»żĘż┐┴T┐▐żŽĪóArmż╚×┤Ń^ż╣żļż┐żßżŪżŽż╩ż»ĪóCPUżŪżŌIntelż╬x86ÅUż╚Armż╬ź│źóż╚żŪżŽISAĪ╩╠┐╬ßź╗ź├ź╚źóĪ╝źŁźŲź»ź┴źŃĪ╦ż¼░█ż╩żļż┐żßĪó▐kĮ’ż╦ŠĶż╗żķżņż╩żżż│ż╚ż╦×┤ż╣żļ╔į╦■ż“▓“»éż╣żļż┐żßżŪżóż├ż┐Īóż╚2017ŃQ12ĘŅż╦═ĶŲ³żĘż┐UC Berkeleyż╬Krste AsanovicČĄĶbżŽĖņż├żŲżżżļ(╗▓╣═½@╬┴2)ĪŻż│żņż½żķżŽĪó1ź┴ź├źūSoCæųż╦CPUżŌGPUżŌDSPĪóISPż╩ż╔══Ī╣ż╩źūźĒź╗ź├źĄż“ĮĖ└čż╣żļ╚ŠŲ│öüź┴ź├źūż¼╗\ż©żŲżżż»ż┐żßĪóżĮż╬ż┐żßż╦żŌ▐kż─ż╬Č”─╠ż╚ż╩żļISAż¼ØŁ═ūż╚ż╩żļż╚Įęż┘żŲżżż┐ĪŻ

┐▐4ĪĪRISC-V Foundation▓├╠┴╝ę┐¶żŽ2ŃQØiż╬3Ū▄ż╦ĪĪĮąųZĪ¦Western Digital

RISC-Vź│źóż“╔ߥ┌żĄż╗żļż┐żßż╬├─öüĪóRISC-V Foundationż╬╗▓▓├źßź¾źąĪ╝żŽ2016ŃQ9ĘŅ╗■┼└żŪż╬40╝ęż½żķĖĮ║▀129╝ęż╦╗\ż©ĪóżĮż╬┐¶żŽ╗\▓├├µż└ż╚żżż”Ī╩╗▓╣═½@╬┴1Ī╦ĪŻ┬Õ╔Į┼¬ż╩źßź¾źąĪ╝ż╦żŽĪóGoogleżõNvidiaĪóIBMĪóQualcommĪóTeslaĪóNXPĪóSamsungĪóMicronĪóSiemensż╩ż╔ż╬źėź├ź░ź═Ī╝źÓż¼ź║źķźĻż╚╩┬ż¾żŪżżżļ(┐▐4)ĪŻ

╗▓╣═½@╬┴

1. ╚ŠŲ│öüż╬Linuxż╦ż╩żļż½ĪóźšźĻĪ╝ż╬CPUź│źóRISC-V (2016/09/06)

2. ╚ŠŲ│öüźūźĒź╗ź├źĄźßĪ╝ź½Ī╝ż¼ĮĖ±TżĘż┐╗š┴÷(IoT/ź╗źŁźÕźĻźŲźŻįć) (2017/12/22)