LatticeĪóżĶżĻź©ź├źĖŖõżŪź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż“·t│½

Š«æä╠ŽFPGAżŪ┘T║▀┤Čż“┐āż╣Lattice Semiconductorż¼ź©ź├źĖźŪźąźżź╣ż╬źżź¾źŲźĻźĖź¦ź¾ź╚▓Įż╦Š«æä╠ŽFPGAż╬ØŁ═ū└Łż“┴╩ĄßżĘżŲżżżļĪŻIoTźĘź╣źŲźÓżŪżŽĪóźŪĪ╝ź┐ż“µ£żŲź»źķź”ź╔ż╦æųż▓Ī󟻟ķź”ź╔æųżŪźŪĪ╝ź┐ĮĶ═²ż╣żļż╩żķżóż▐żĻż╦żŌź»źķź”ź╔ż╬╔ķ├┤ż¼ĮjżŁż»ż╩żļĪŻż│ż╬ż┐żßĪóIoT├╝¼ŹŖõżŪżóżļµć┼┘źŪĪ╝ź┐ĮĶ═²ż╣ż┘żŁż╚żżż”ż╬ż¼ź©ź├źĖź│ź¾źįźÕĪ╝źŲźŻź¾ź░żŪżóżļĪŻ

▐köĄĪóź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╬└ż─cżŪżŽĪóØŖż╦ź»źķź”ź╔ż╬źŽĪ╝ź╔ź”ź©źóżŪżóżļźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żŪż╬▒ķōQż“▓├Å]ż╣żļż┐żßĪó“£═Ķż╬CPUżõGPUż╦▓├ż©ĪóFPGAżŪ└ņ├ōövŽ®ż“║ŅżĻ▒ķōQż“╣ŌÅ]▓ĮżĘżĶż”ż╚żżż”╬«żņżŌżóżļĪŻCPUżŽŲ▒żĖźŽĪ╝ź╔ź”ź©źóæųżŪĪ󿥿▐żČż▐ż╩źĮźšź╚ź”ź©źóż“Ų░ż½żĘŲ╚śOż╬ĄĪē”ż“╝┬ĖĮż╣żļź┴ź├źūżŪżóżļż¼ĪóGPUżŽCPUż█ż╔źšźņźŁźĘźėźĻźŲźŻż¼ż╩żżż¼ĪóżõżŽżĻźĮźšź╚ź”ź©źóż“╗╚ż├żŲź░źķźšźŻź├ź»ź╣ż╬┐¦┼╔żĻ(źņź¾ź└źĻź¾ź░)ż╬żĶż”ż╩╩┬š`▒ķōQż╦Ė■ż»ĪŻżĄżķż╦╣ŌÅ]▓ĮżĘż┐żżŠņ╣ńż╦żŽĪóźĮźšź╚ź”ź©źóżŪżŽż╩ż»Īó╔w─Ļż╬źóźļź┤źĻź║źÓ▒ķōQż“źŽĪ╝ź╔ź”ź©źóżŪ╣įż”ż╬ż╦żŽFPGAż¼Ė■ż»ĪŻ╬Ńż©żąź▐źļź┴CPUźĘź╣źŲźÓżŪźąź╣żõźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż¼ź▄ź╚źļź═ź├ź»ż╩żķĪóżĮż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣övŽ®ż“FPGAżŪ╝┬ĖĮż╣żļĪŻ

Intelż¼Alteraż“āA╝²żĘż┐ż╬żŽĪóż▐żĄż╦FPGAżŪźŽĪ╝ź╔ź”ź©źó└ņ├ōövŽ®ż“║Ņżļ├ō²ŗżŌź½źąĪ╝ż╣żļż┐żßż└ĪŻIntelżŽCORE i5żõi7ż╩ż╔ż╬║Ū┐ĘźūźĒź╗ź├źĄżŪżŌśO╝ę│½╚»ż╬ź▐źļź┴GPUź│źóż“ĮĖ└čżĘżŲżżżļż¼ĪóĄĪ│Ż│žØ{żõźŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░ż╩ż╔ż╬AI├ō²ŗżŪżŽGPU└ņ╠ńż╬źšźĪźųźņź╣źßĪ╝ź½Ī╝Nvidiaż╚─¾Ę╚żĘżŲżżżļĪŻż│żņż╦żĶżĻIntelżŽ═źżņż┐CPUĪóGPUĪóFPGAż“Š}ż╦Ų■żņżŲż¬żĻĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż¼ż╔ż╬żĶż”ż╦┐╩▓ĮżĘżŲżŌ×┤▒■żŪżŁżļżĶż”ż╦żĘż┐ĪŻQualcommżŽXilinxż╚─¾Ę╚żĘżŲż¬żĻĪ󟎟żź©ź¾ź╔ż╬HPCĪ╩╣Ō└Łē”ź│ź¾źįźÕĪ╝źŲźŻź¾ź░Ī╦Ė■ż▒ż╬╚ŠŲ│öüż“░Ęż”Qualcomm Datacenter Technologiesż“Š«▓±╝ęż╚żĘżŲ┴╚“E▓ĮżĘĪóż│ż╬ż█ż╔HPC╩¼╠ŅĖ■ż▒ż╦ARMź┘Ī╝ź╣ż╬ź▐źżź»źĒźūźĒź╗ź├źĄCentric 2400ż“Įą▓┘żĘż┐ĪŻ

┐▐1ĪĪLattice Semiconductor COOż╬Glen HawkĢ■

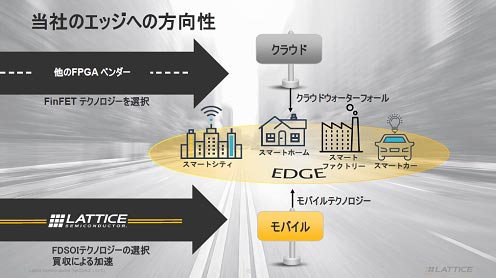

FPGAż“└ņ├ōż╬źŽĪ╝ź╔ź”ź©źóövŽ®ż╚żĘżŲ╗╚ż”├ō²ŗżŽź│ź¾źįźÕĪ╝ź┐ż└ż▒żŪżŽż╩żżĪŻĄĪ│Ż│žØ{żõźŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░ż╬żĶż”ż╩AIż╦żŌĖ■żżżŲż¬żĻĪóLatticeż╬COOĪ╩║Ū╣Ō╝╣╣į└šŪżŪvĪ╦ż╬Glen HawkĢ■Ī╩┐▐Ż▒)żŽĪóĪųź│ź¾źįźÕĪ╝źŲźŻź¾ź░żŽź©ź├źĖźŪźąźżź╣ż╦żŌżõż├żŲż»żļżĶż”ż╦ż╩ż├ż┐Īūż╚Įęż┘żŲżżżļĪŻØŖż╦Īóźżź¾źŲźĻźĖź¦ź¾ź╚▓ĮĪóź╣ź▐Ī╝ź╚▓ĮżŽź©ź├źĖż╦Ė■ż½ż├żŲż¬żĻĪóż│żņż▐żŪźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żŪ╗╚ż’żņżŲżŁż┐ź╦źÕĪ╝źķźļź│ź¾źįźÕĪ╝źŲźŻź¾ź░żŌź©ź├źĖż╦═ĶżļżĶż”ż╦ż╩ż├żŲżżżļż╚żżż”ĪŻ

ź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»ź│ź¾źįźÕĪ╝ź┐żŽĪó╩┬š`ĮĶ═²ż¼żŪżŁżļż│ż╚Īó┐ʿʿżźóźļź┤źĻź║źÓż“╩čż©żķżņżļż╚żżż”źßźĻź├ź╚żŌżóżļĪŻżĘż½żŌĪóLatticeż╬żĶż”ż╩Š«æä╠ŽFPGAżŽź╦źÕĪ╝źķźļź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╦żŌĖ■ż»ż╚HawkĢ■żŽĖ└ż”ĪŻĖĮ║▀AIż╬źŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░ż╬▒■├ōż╚żĘżŲźčź┐Ī╝ź¾Ū¦╝▒ż╦Ė■żżż┐øQż▀╣■ż▀ź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»Ī╩CNNĪ╦ż¼¾Hż»╗╚ż’żņżŲżżżļĪŻ│žØ{ż╣żļŠņ╣ńż╬─_ż▀ĘĖ┐¶żŽ“£═Ķ8źėź├ź╚Īó16źėź├ź╚ż¼╗╚ż’żņżŲżżżļż¼ĪóżŌż├ż╚╗@┼┘ż“═Ņż╚żĘżŲżŌż½ż▐ż’ż╩żżĪŻ4źėź├ź╚ĪóżóżļżżżŽ1źėź├ź╚Ī╩1ż╚0ż╬źąźżź╩źĻĪ╦ż╚żżż”─_ż▀żĄż©żŌ─¾░ŲżĄżņżŲżżżļĪŻLatticeż╬FPGAż╦╗╚ż’żņżŲżżżļLUTĪ╩źļź├ź»źóź├źūźŲĪ╝źųźļĪ╦żŽ4Ų■╬ü1Įą╬üż╩ż╬żŪĪóżÓżĘżĒCNNż╦żŽźįź├ź┐źĻż└Īóż╚HawkĢ■żŽĖ└ż”ĪŻ

┐▐2ĪĪLatticeż╬┴└żżżŽŠ«æä╠Žż╬▒■├ōż½żķź©ź├źĖżžĖ■ż½ż”ĪĪĮąųZĪ¦Lattice Semiconductor

ź╦źÕĪ╝źķźļź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż└ż▒żŪżŽż╩ż»ĪóLatticeżŽź©ź├źĖżõ░cÖ┌ż╩ż╔Š«æä╠Žż╬ĮĖ└čövŽ®ż“└▀╝ŖżĘżŲżżżļż┐żßĪóXilinxżõAlteraż╚żŽżųż─ż½żķż╩żż(┐▐2)ĪŻżĘż½żŌĪóŠ«æä╠ŽżŪżóżļż½żķŠ├õJ┼┼╬üż╬║’žōż¼═ź└ĶżĄżņĪóØiŪvżŽ╚∙║┘▓Įż╚FinFETźūźĒź╗ź╣ż“╗╚ż├żŲżżżļż╬ż╦×┤żĘżŲĪóLatticeżŽź│ź¾źįźÕĪ╝źŲźŻź¾ź░├ō²ŗżŪżŌ─ŃŠ├õJ┼┼╬üż╬FD-SOIźūźĒź╗ź╣ż“┬ō┘Iż╣żļĪŻ

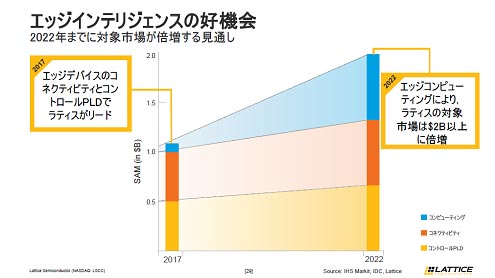

ź│ź¾źįźÕĪ╝źŲźŻź¾ź░├ō²ŗż“┴└ż”ż╬żŽĪó┐ʿʿż└«─╣╩¼╠Ņż└ż╚ż▀żŲżżżļż½żķż└ĪŻLatticeż╬PLDżŽż│żņż▐żŪöUĖµÅUżŪż┐ż»żĄż¾╗╚ż’żņĪóż│ż│┐¶ŃQżŽź│ź═ź»źŲźŻźėźŲźŻżŪäPżążĘżŲżŁż┐ĪŻżĘż½żĘĪóź│ź═ź»źŲźŻźėźŲźŻżõźŌźąźżźļżŽżĮżĒżĮżĒŲ¼æ]ż┴ż╦ż╩ż├żŲż¬żĻĪó╝Īż╬┐Ę╩¼╠Ņż╚żĘżŲź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╦┴└żżż“¤²ż▒ż┐(┐▐3)ĪŻ

┐▐3ĪĪź©ź├źĖź│ź¾źįźÕĪ╝źŲźŻź¾ź░żŪ║ŻĖÕ└«─╣żžĪĪĮąųZĪ¦Lattice Semiconductor

║Żż½żķ5ŃQĖÕż╬2022ŃQż╦żŽź©ź├źĖź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż¼└«─╣ż╣żļż│ż╚żŪĪóLatticeżŌ▐kĮ’ż╦└«─╣żĘżŲżżż»ż╚┤³┬įż╣żļĪŻ