ä▌╣±ź┘ź¾ź┴źŃĪ╝Netronomeż¼«ĆźŽźżź©ź¾ź╔ż╩ź═ź├ź╚ź’Ī╝ź»źšźĒĪ╝źūźĒź╗ź├źĄż“└▀╝Ŗ

ä▌Intelż½żķź╣źįź¾źóź”ź╚żĘĪó▒čMarconiż╬ź░źļĪ╝źūżŌ▓├ż’ż├żŲ┴Ž╬®żĄżņż┐ä▌NetronomeĪ╩ź═ź╚źĒź╬Ī╝źÓż╚╚»▓╗Ī╦╝꿎ĪóIntelż½żķIXP28xxźŽźżź©ź¾ź╔źūźĒź╗ź├źĄż╬źķźżź╗ź¾ź╣ż“£pż▒2003ŃQż╦ź╣ź┐Ī╝ź╚żĘż┐ź┘ź¾ź┴źŃĪ╝żŪżóżļĪŻ2övų`ż╬½@ČŌ─┤├ŻżŌĮ¬ż’żĻ5200╦³ź╔źļż“įużŲĪóż│ż╬ż█ż╔ź═ź├ź╚ź’Ī╝ź»źšźĒĪ╝źūźĒź╗ź├źĄ┐Ę×æēäNFP-3200ż╬źĻźĻĪ╝ź╣żžż╚ż│ż«ż─ż▒ż┐ĪŻ«ĆźŽźżź©ź¾ź╔ż╬▒■├ōżžż╬ŪõżĻ╣■ż▀ż“┴└ż”ĪŻ

Netronome╝ęCEOż╬Niel ViljoenĢ■

┴ŽČ╚ŪvżŪCEOż╬Niel ViljoenĢ■żŽĪó3Pż“×óż©żŲżżżļż│ż╚ż¼ź═ź├ź╚ź’Ī╝ź»źūźĒź╗ź├źĄżŪżŽ─_═ūż└ż╚żżż”ĪŻ3Pż╚żŽźčźšź®Ī╝ź▐ź¾ź╣Ī╩└Łē”Ī╦ĪóPower consumptionĪ╩Š├õJ┼┼╬üĪ╦ĪóżĮżĘżŲProgrammabilityĪ╩źūźĒź░źķźÓżŪżŁżļż│ż╚Ī╦ĪŻ

ż│ż╬ź═ź├ź╚ź’Ī╝ź»źšźĒĪ╝źūźĒź╗ź├źĄżŽĪó10Gźėź├ź╚Ethernetż½żķż╬Ų■╬üż╦×┤żĘżŲĪóź╗źŁźÕźĻźŲźŻż“ż½ż▒ż┐żĻ▓“Į³żĘż┐żĻż╣żļż┐żßż╬░┼ęÄ▓ĮĪ”▓“Ų╔▓ĮĮĶ═²Īó▓Š„[▓Įź│ź¾źįźÕĪ╝ź┐ĮĶ═²ĪóDPIĪ╩deep packet inspectionĪ¦źčź▒ź├ź╚╣Įļ]ż“▓“└ŽżĘ▓┐ż¼żóżļż╬ż½ż“─┤ż┘żļĪ╦ĮĶ═²ż╚żżż├ż┐╣Ō┼┘ż╬╝ŖōQĮĶ═²ż“═ūĄßż╣żļUnified Computing ArchitectureĖ■ż▒ż╦│½╚»żĄżņż┐ĪŻżĘż½żŌź═ź├ź╚ź’Ī╝ź»ż╬╬«żņż“┤Ų£åĪóĮĶ═²ż╣żļČ╦żßżŲĮĖ└č┼┘ż╬╣ŌżżĮĶ═²ż“1ź┴ź├źūżŪ╝┬ĖĮżĘĪ󿥿▐żČż▐ż╩ź═ź├ź╚ź’Ī╝ź»ż╦×┤▒■żŪżŁżļżĶż”ż╦źūźĒź░źķźÓżŪżŁżļICżŪżóżļĪŻ

┘J┘Tż╬źūźĒź╗ź├źĄż└ż╚Īóź╗źŁźÕźĻźŲźŻ┤Ų£åĪ”ĮĶ═²ż╣żļĄĪē”ż└ż▒ż“Ęeż─źūźĒź╗ź├źĄĪóIPżõź═ź├ź╚ź’Ī╝ź»ż╬źūźĒź╚ź│źļż“źūźĒź░źķźÓż╣żļź═ź├ź╚ź’Ī╝ź»źūźĒź╗ź├źĄĪ󿥿ķż╦└@├ōż╬─╠┐«├ōźūźĒź╗ź├źĄż╚żżż”3ż─ż╬źūźĒź╗ź├źĄż“╗╚ż├żŲź═ź├ź╚ź’Ī╝ź»ż╬ĮĶ═²ż“╣įż├żŲżżż┐ĪŻ║ŻövżŽż│żņżķ3ż─ż╬źūźĒź╗ź├źĄż“┼²╣ńżĘżŲźĘź¾ź░źļź┴ź├źūżŪĮĶ═²Ų░║Ņż╣żļČ╦żßżŲźŽźżź©ź¾ź╔ż╩źūźĒź╗ź├źĄż╦ż╩ż├żŲżżżļĪŻ

æųż╬┐▐ż╦żóżļżĶż”ż╦Īóź«ź¼źėź├ź╚źżĪ╝źĄĪ╝żõź╗źŁźÕźĻźŲźŻĄĪē”ż“╣ŌżßĪóź▐źļź┴ź│źóż“Ęeż┴Īó▓Š„[▓Įż╦×┤▒■ĪóDPIĄĪē”ż“Ęeż┴ĪóźßźŌźĻĪ╝źąź¾ź╔╔²żŌ╣Łżżż╚żżż”ØŖ─╣ż“ż╣ż┘żŲĘeż─ĪŻ

┴└ż”▌xŠņżŽĪó▓Š„[▓ĮČ\Įčż¼äėż»ĄßżßżķżņżŲżżżļźŪĪ╝ź┐ź╗ź¾ź┐Ī╝żõĪóź═ź├ź╚ź’Ī╝ź»ĄĪ▀_źßĪ╝ź½Ī╝ĪóźšźĪźżźõź”ź®Ī╝źļ┤ļČ╚ĪóźĮźšź╚ź”ź©źóOEM┤ļČ╚Īóź═ź├ź╚ź’Ī╝ź»źżź¾źšźķź╣ź╚źķź»ź┴źŃż“░Ęż”źŽźżź©ź¾ź╔ż╩┤ļČ╚Īóż╩ż╔ĪŻĖĮ║▀IXPź═ź├ź╚ź’Ī╝ź»źūźĒź╗ź├źĄż“╗╚ż├żŲżżżļĖ▄Ąęż¼źóź├źūź░źņĪ╝ź╔ż╣żļż╚żżż”▌xŠņżŌ┴└ż©żļĪŻ

╝ńż╩╗┼══żŽ░╩▓╝ż╬─╠żĻĪ¦

ź▐źļź┴ź│źóźóĪ╝źŁźŲź»ź┴źŃżŪ40Ė─ż╬ź│źóż½żķż╩żĻ1.4GHzżŪŲ░║Ņż╣żļĪŻ╠┐╬ßż╬ĮĶ═²└Łē”żŽ56BIPSĪ╩billion instructions per secondĪ╦Īó320Ų▒╗■ź╣źņź├ź╔╚»╣į▓─ē”żŪĪó30MppsĪ╩packets per secondĪ╦ż╬ź╣źįĪ╝ź╔ż╦ż¬ż▒żļźčź▒ź├ź╚┼÷ż┐żĻż╬╠┐╬ß┐¶żŽ1800╠┐╬ßĪóDPI║ŅČ╚ż“20Gbpsż╚żżż”ź╣źįĪ╝ź╔żŪ╣įżżĪóźŪĪ╝ź┐ż╬źšźĒĪ╝ż“öUĖµż╣żļĪŻ

▓Š„[▓ĮČ\ĮčżŪżŽĪó256źŁźÕĪ╝ż╬SRIOVĪ╩Single Root I/O VirtualizationĪ╦æä│╩ż“Ęeż┴ĪóPCIe v2.0ż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“─╠żĘżŲx86ÅUźūźĒź╗ź├źĄż╚─╠┐«ż╣żļĪŻ

Š├õJ┼┼╬ü└Łē”żŽĪó1Wżóż┐żĻ18▓»3800╦³╠┐╬ßż“ĮĶ═²żĘĪóCPUż╬ź¬Ī╝źąĪ╝źžź├ź╔ż“80%─ŃžōżŪżŁżļż┐żß└Łē”┼¬ż╦żŽ10Ū▄╣ŌżżĪŻ

ź╗źŁźÕźĻźŲźŻż¬żĶżė░┼ęÄĮĶ═²Č\Į迎║YØŹ┼¬ż╩░┼ęÄźóźļź┤źĻź║źÓż“ź½źąĪ╝żĘĪóżĮż╬Å]┼┘żŽ20GbpsĪŻ

65nmCMOSźūźĒź╗ź╣żŪ×æļ]ĪŻ

NFP-3200ź═ź├ź╚ź’Ī╝ź»źšźĒĪ╝źūźĒź╗ź├źĄżŪź═ź├ź╚ź’Ī╝ź»ż╬źšźĒĪ╝ż“▓“└ŽżĘĪóx86ÅUź┴ź├źūź╗ź├ź╚ż“─╠żĘżŲź▐źļź┴ź│źóCPUżŪ▓Š„[▓ĮźĘź╣źŲźÓż“╝┬ĖĮż╣żļ╬Ńż¼▓╝ż╬┐▐żŪżóżļĪŻ

10Gbps Ethernetż“─╠żĘżŲźŪĪ╝ź┐ż“┤Ų£åĪ”ĮĶ═²żĘĪó▓Š„[▓ĮźĘź╣źŲźÓż“╝┬╣įż╣żļĪŻNFP-3200ż╬SRIOVż½żķPCI Express Gen2ż╬8źņĪ╝ź¾ż“ĘążŲx86ÅUź┴ź├źūź╗ź├ź╚ż╦╣įżŁĪ󿥿ķż╦ź▐źļź┴ź│źóCPUżžż╚─╠┐«Ī”ĮĶ═²ż╣żļĪŻIntelÅU╣ŌÅ]źĘźĻźóźļI/OżŪżóżļQPIĪ╩AMDÅUż╬HyperTransport┴Ļ┼÷Ī╦ż“żžżŲź▐źļź┴ź│źóCPUż╚─Š└▄żõżĻŲDżĻż╣żļöĄ╝░żŽ2010ŃQż╦ż╩żļ═Į─ĻĪŻ

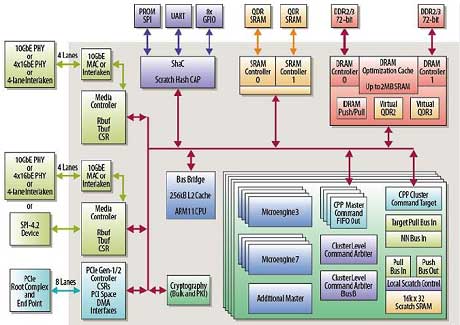

NFP-3200ż╬źųźĒź├ź»┐▐żŽ░╩▓╝ż╬ż╚ż¬żĻżŪĪóIntelż½żķźķźżź╗ź¾ź╣ČĪ═┐ż“£pż▒ż┐║ŪĮķż╬IXP28xxźĘźĻĪ╝ź║ż½żķ╚µż┘żŲĪó16ź│źóż½żķ40ź│źóż╬ź▐źżź»źĒź©ź¾źĖź¾Ī╩MEĪ╦żž│╚ĮjĪóźķź¾źąź╣ż½żķDDR2/3żž─Ńź│ź╣ź╚▓ĮĪóPCIż½żķPCI Express v2.0żž╚¶╠÷┼¬ż╦╣ŌÅ]▓ĮĪóXscaleźūźĒź╗ź├źĄż½żķARM11ź│źóżžöĪ╣įż╦żĶżĻL2źŁźŃź├źĘźÕ└Łē”ż“Ė■æųĪó10Gbps Ethernetż“┼ļ║▄Īó25Gbpsż╬Interlaken╣ŌÅ]źĘźĻźóźļźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“┼ļ║▄Īó░┼ęÄ▓Įźóź»ź╗źķźņĪ╝ź┐ż“┼ļ║▄ĪóPKIźóź»ź╗źķźņĪ╝ź┐ż“┼ļ║▄Īóż╚żĘżŲIXPźūźĒź╗ź├źĄż½żķĄĪē”Ī”└Łē”ż╚żŌĮj╔²ż╦Ė■æųżĘżŲżżżļĪŻ

ź┴ź├źūż╬źčź├ź▒Ī╝źĖżŽ40mmĪ▀40mmżŪĪóźįź¾┐¶żŽ1521źįź¾ĪŻźŽĪ╝ź╔ź”ź©źóĪ”źĮźšź╚ź”ź©źóż╚żŌ│½╚»ź─Ī╝źļż¼┬Ęż├żŲżżżļĪŻ║ŻĖÕĪóPCIeż╦┬Õż’żĻQPIźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“×óż©ż┐ź┴ź├źūżŌ╝Ŗ▓ĶżĘżŲżżżļĪŻ