├µ╣±Įķż╬┐ĘĘ┐NORźšźķź├źĘźÕźßźŌźĻżŪ┴╚ż▀╣■ż▀ÅUż“┴└ż”

├µ╣±ż╦┐ʿʿżźßźŌźĻź┘ź¾ź┴źŃĪ╝ż¼┼ąŠņżĘż┐ĪŻChina FlashĪ╩├µÜW╣░▒¦ĮĖ└«┼┼Ž®Ī╦ż╚Ō}żążņżļźšźĪźųźņź╣ż└ĪŻ×æļ]żŽźšźĪź”ź¾ź╔źĻż╦░══Ļż╣żļĪŻ║Żż½żķ▌xŠņż╦Ų■żļ░╩æųĪóØŖ─╣ż¼ØŁ═ūż└ż¼Īóż│żņż▐żŪż╬├µ╣±ż╬źßźŌźĻźßĪ╝ź½Ī╝ż╚żŽµ£ż»░Ńż”ĪŻĖÕĮęż╣żļż¼Īó┐Ę│½╚»ż╬Ų╚śOźßźŌźĻČ\Įčż“Ęeż┴ĪóĖĄIntelż╬Stefan LaiĢ■Ī╩┐▐1Ī╦ż¼CTOż╚ż╩ż├żŲżżżļ┤ļČ╚ż└ĪŻ

┐▐1ĪĪChina Flash╝ęCTOżŪĖĄIntel VPż╬Stefan Lai

ż│ż╬NORźšźķź├źĘźÕż╬║ŪĮjż╬ØŖ─╣żŽĪóźūźĒź░źķź▀ź¾ź░Š}╦Īż“│½╚»żĘż┐ż│ż╚żŪ─ŃżżźūźĒź░źķźÓź©ź═źļź«Ī╝żŪĮ±żŁ╣■żßżļż│ż╚ż└ĪŻż│ż╬ż┐żßŠ├õJ┼┼╬üżŌĮ±żŁ╣■ż▀┼┼░ĄĪ”Š├ĄŅ┼┼░ĄżŌ─Ńż»żŲ║čżÓĪŻ╬Ńż©żąźūźĒź░źķźÓ┼┼░ĄżŽ3VĪóŠ├ĄŅ┼┼░ĄżŽ7Vż╚─ŃżżĪŻżĘż½żŌ“£═Ķż╬źšźĒĪ╝źŲźŻź¾ź░ź▓Ī╝ź╚Ę┐NORźšźķź├źĘźÕżŪżŽĪóø]ź┴źŃź¾ź═źļĖ·▓╠ż╬ż┐żßż╦źčź¾ź┴ź╣źļĪ╝ż¼ÅŚż│żĻżõż╣ż»Īó╚∙║┘▓ĮżŪżŁż╩ż»ż╩żļż╚żżż”╠õ¼öż¼żóż├ż┐ż¼Īó┐ĘĘ┐NORźšźķź├źĘźÕżŽż│ż╬╠õ¼öż¼ż╩ż»ĪóżÓżĘżĒ╚∙║┘▓ĮżĘż╩ż▒żņżąźßźŌźĻĖ·▓╠ż¼Įąż╩żżż╚żżż”ØŖ─╣ż¼żóżļĪŻżĘż½żŌĪóŲ╔ĮążĘźóź»ź╗ź╣╗■┤ųżŽż’ż║ż½60Ī┴90nsż╚Å]żżĪŻ

źūźĒź░źķź▀ź¾ź░Č\Įčż“Šę▓ż╣żļØiż╦Īó╚∙║┘▓Į▓─ē”ż╩┐ʿʿżNORźšźķź├źĘźÕż╬źėźĖź═ź╣źŌźŪźļż╦ż─żżżŲ└Ō£½żĘżĶż”ĪŻż│ż╬NORźšźķź├źĘźÕżŽĪó┐ĘĘ┐żµż©ż╦IPź┘ź¾ź└Ī╝ż╚żżż”źėźĖź═ź╣żŌ╩╠▓±╝ęż╚żĘżŲ├ō┴TżĘż┐ĪŻż│żņż¼LeWay Integrated CircuitĪ╩├µ▒¦ÜW├ęĪ╦╝ężŪżóżļĪŻż╩ż╝IPź┘ź¾ź└Ī╝żŌ├ō┴TżĘż┐ż½ĪŻChina Flashż╬┴└ż”ż┘żŁ▌xŠņż¼┴╚ż▀╣■ż▀źßźŌźĻ╩¼╠Ņż└ż½żķżŪżóżļĪŻżżż’żąźšźķź├źĘźÕź▐źżź│ź¾ż╩ż╔ż¼ż│żņż╦┴Ļ┼÷ż╣żļĪŻźšźķź├źĘźÕź▐źżź│ź¾żŪżŽĪóźšźķź├źĘźÕźßźŌźĻŗ╩¼ż└ż▒ż“IPż╚żĘżŲźķźżź╗ź¾ź╣╚╬Ūõż╣żļż│ż╚ż¼żĶż»╣įż’żņżŲżŁż┐ĪŻ

┐ĘĘ┐NORźšźķź├źĘźÕż╚żżż├żŲżŌĪóźŪźąźżź╣╣Įļ]żŽźĘź¾źūźļżŪ▐k╚╠ż╬źšźķź├źĘźÕź▐źżź│ź¾żŪØŁ═ūż╩ź▐źżź│ź¾żõźĒźĖź├ź»ż╬źūźĒź╗ź╣ż╚ż╬Ė▀┤╣└ŁżŌżóżļĪŻż─ż▐żĻĪó1┴žź▌źĻźĘźĻź│ź¾źūźĒź╗ź╣żŪ║čżÓż┐żßĪó“£═Ķż╬źšźĒĪ╝źŲźŻź¾ź░ź▓Ī╝ź╚╣Įļ]żŪ╗╚ż’żņżŲżŁż┐2┴žź▌źĻźĘźĻź│ź¾źūźĒź╗ź╣żŽØŁ═ūż╩żżĪŻż│ż╬ż┐żßĪóźūźĒź╗ź╣ź│ź╣ź╚żŽź▐źżź│ź¾żõźĒźĖź├ź»ż╚ż█ż╚ż¾ż╔╩čż’żķż╩żżż┐żßŖWż»ż╩żļ▓─ē”└Łż¼╣ŌżżĪŻ

ż│żņż▐żŪż╬NORźšźķź├źĘźÕż¼źūźĒź╗ź╣æųżŪ╣įżŁĄ═ż├ż┐ż╬żŽ╚∙║┘▓ĮżĘż╦ż»ż½ż├ż┐ż½żķż└Īóż╚LaiĢ■żŽĮęż┘żļĪŻIntelż¼NORźšźķź├źĘźÕźßźŌźĻż“└żż╦ĮążĘż┐ż╬żŽ┼ņėøżĶżĻżŌ┴ßż»Īó1986ŃQżŪżóżĻĪóżĮż╬╗■żŽ1.5µmźūźĒź╗ź╣ż“╗╚żżĪóNORźšźķź├źĘźÕźßźŌźĻż╚żŽĖ└ż’ż║ETOXźßźŌźĻż╚Ō}ż¾ż└ĪŻ┼÷Įķż╬├ō²ŗżŽźŪźĖź┐źļź½źßźķż└ż├ż┐ż¼ĪóĘ╚┬ė┼┼ÅBż╬BIOSżõź╣ź╚źņĪ╝źĖżžż╚╩č▓ĮżĘżŲżżż├ż┐ĪŻĮĖ└č┼┘ż“æųż▓źßźŌźĻ═Ų╬╠ż“╗\żõż╣ż┐żßż╦╚∙║┘▓Įż“┐╩żßżŲżżż├ż┐ż¼Īóź╔źņźżź¾-źĮĪ╝ź╣┤ųż╬źčź¾ź┴ź╣źļĪ╝ż¼ÅŚżŁżŲŲ░║ŅżĘż╦ż»ż»ż╩żļż┐żßż│żņ░╩æų╚∙║┘▓ĮżŪżŁż╩żżż╚żżż”ż╚ż│żĒż▐żŪżŁż┐ĪŻż│żņż¼50nmØiĖÕż└ż├ż┐ĪŻ

┐▐2ĪĪ┐ĘĘ┐źšźĒĪ╝źŲźŻź¾ź░źĮĪ╝ź╣ż╬NORźšźķź├źĘźÕźßźŌźĻź╗źļĪĪĮąųZĪ¦├µÜW╣░▒¦

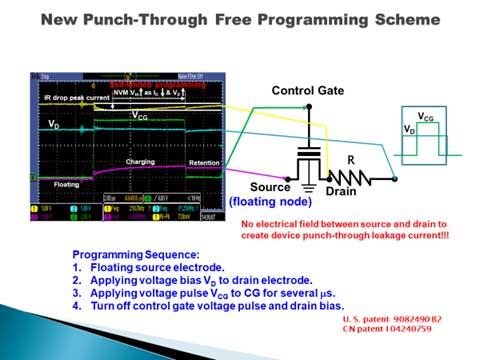

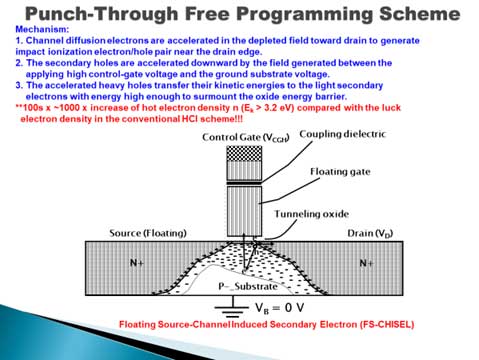

┐ĘĘ┐NORźšźķź├źĘźÕżŪ│½╚»żĄżņż┐źūźĒź░źķź▀ź¾ź░Š}╦Īż╬┤╦▄┼¬ż╩╣═ż©żŽĪóź█ź├ź╚ź©źņź»ź╚źĒź¾ÅRŲ■ż“├ōżżż┐źšźĒĪ╝źŲźŻź¾ź░ź▓Ī╝ź╚ż╦ō¶żŲżżżļĪŻ┐ĘĘ┐NORźšźķź├źĘźÕż╬┤╦▄ź╗źļżŽĪó┐▐2ż╬żĶż”ż╦źšźĒĪ╝źŲźŻź¾ź░ź▓Ī╝ź╚żŪżŽż╩ż»ĪóźšźĒĪ╝źŲźŻź¾ź░źĮĪ╝ź╣ż“║╬├ōż╣żļĪŻ─╠Š’ż╬MOSFETż╬ź╔źņźżź¾┼┼░Ąż“▐k─Ļż╦żĘżŲĪóöUĖµź▓Ī╝ź╚CGż╦źčźļź╣┼┼░Ąż“ż½ż▒żļż╚Īó║ŪĮķżŽźĮĪ╝ź╣żóżļżżżŽźĄźųź╣ź╚źņĪ╝ź╚ż½żķź╔źņźżź¾żž┴÷╣įż╣żļ┼┼╗ęż¼ź╔źņźżź¾┼┼─cż╦żĶż├żŲ▓├Å]żĄżņĪóź█ź├ź╚ź©źņź»ź╚źĒź¾ż╦ż╩żĻĪóź╔źņźżź¾ōļ░Ķż╦╣įż├ż┐żĻĪóŪ÷żż¤©▓Į╦ņż“ź╚ź¾ź═źĻź¾ź░żĘż┐żĻż╣żļĪŻźĮĪ╝ź╣żŽźšźĒĪ╝źŲźŻź¾ź░ż╩ż╬żŪĪó╝Īŗīż╦┼┼▓┘(┼┼╗ę)ż¼╬»ż▐żĻöUĖµź▓Ī╝ź╚ż“ź¬źšż╦żĘżŲżŌ┼┼▓┘ż¼Į╝┼┼żĄżņż┐ėX▌åż“╩▌ż─ĪŻżĘż½żŌźĮĪ╝ź╣┼┼░╠żŽź╔źņźżź¾┼┼░╠ż╦ŖZż┼ż»ż┐żßĪóźčź¾ź┴ź╣źļĪ╝żŽÅŚżŁż╦ż»ż»ż╩żļĪŻ

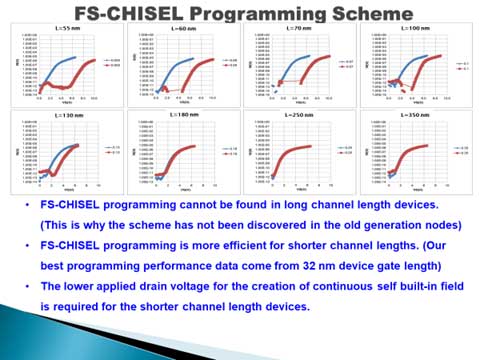

ż│ż╬źūźĒź░źķź▀ź¾ź░╦Īż“╩╠ż╬£å┼└ż½żķĖ½ż┐ż╬ż¼┐▐3żŪżóżļĪŻź╔źņźżź¾ż╚źĄźųź╣ź╚źņĪ╝ź╚┤ųż╬┼┼─cż╦żĶż├żŲź╔źņźżź¾Č§Ēś┴žżŽźĄźųź╣ź╚źņĪ╝ź╚Ŗõż╦╣Łż¼żĻĪóź╔źņźżź¾┼┼─cż╦░·żŁż║żķżņżŲ┼┼╗ęż¼ź╔źņźżź¾żõź▓Ī╝ź╚ź╚ź¾ź═źļ¤©▓Į╦ņŖõż╦┤¾ż├żŲż»żļĪŻźżź¾źčź»ź╚źżź¬ź¾▓ĮĖĮō■ż¼ź╔źņźżź¾┼┼─cżŪÅŚżŁĪó┼┼╗ęż¼│╩╗ęż╦żųż─ż½żĻ┼┼╗ęĪ”┘ć╣”×┤ż“╚»Ö┌żĘĪó╝ĪĪ╣ż╦┼┼╗ężõ┘ć╣”ż“╗\▓├żĄż╗żŲżżż»ĪŻ▓├Å]żĄżņż┐─_żż┘ć╣”żŌ╝ĪĪ╣ż╚ź©ź═źļź«Ī╝ż“įużŲ2╝Ī┼┼╗ęż“╚»Ö┌żĄż╗Īóź╚ź¾ź═źļ¤©▓Į╦ņż“ĘążŲźšźĒĪ╝źŲźŻź¾ź░ź▓Ī╝ź╚żõźĮĪ╝ź╣ż╦ÅRŲ■żĄżņżļż│ż╚ż╦ż╩żļĪŻ

┐▐3ĪĪź╔źņźżź¾-źĄźųź╣ź╚źņĪ╝ź╚┤ųż╬ȧĒś┴žż¼┤łŖõż╦╣Łż¼żĻĪóźšźĒĪ╝źŲźŻź¾ź░źĮĪ╝ź╣ż╦┼┼▓┘ż¼╬»ż▐ż├żŲżżż»══╗ęż“┐āżĘżŲżżżļĪĪĮąųZĪ¦├µÜW╣░▒¦

“£═Ķż╬ź█ź├ź╚źŁźŃźĻźóÅRŲ■ż╬Šņ╣ńż╚╚µż┘żŲĪó┐¶╝åŪ▄Ī┴1000Ū▄ż╬ź█ź├ź╚ź©źņź»ź╚źĒź¾ż¼ÅRŲ■żĄżņżļż┐żßĪóĖ·╬©żĶż»Į╝┼┼żŪżŁżļĪŻż│ż╬ż┐żßźūźĒź░źķźÓĖ·╬©ż¼æųż¼żĻĪóŠ├õJ┼┼╬üżŽ▓╝ż¼żļĪóż╚żżż”Ślż└ĪŻ

ź▓Ī╝ź╚─╣ż“ø]ż»ż╣żļż╚Č”ż╦ĪóźšźĒĪ╝źŲźŻź¾ź░źĮĪ╝ź╣ż╦┼┼▓┘ż¼╬»ż▐żĻĪóź▓Ī╝ź╚żĘżŁżż┼┼░Ąż¼ĮjżŁż»ż╩ż├żŲżżż»══╗ęż“┐▐4ż╦┐āż╣ĪŻ130nmżóż┐żĻż½żķźßźŌźĻĖ·▓╠ż¼╔ĮżņżŲż»żļ══╗ęż“┐āżĘżŲżżżļĪŻ

┐▐4ĪĪź▓Ī╝ź╚─╣ż“350nmż½żķ55nmżžż╚╚∙║┘▓Įż╣żļż╬ż╦ż─żņźßźŌźĻĖ·▓╠ż¼Ė▓├°ż╦ż╩ż├żŲżżż»ĪĪĮąųZĪ¦├µÜW╣░▒¦

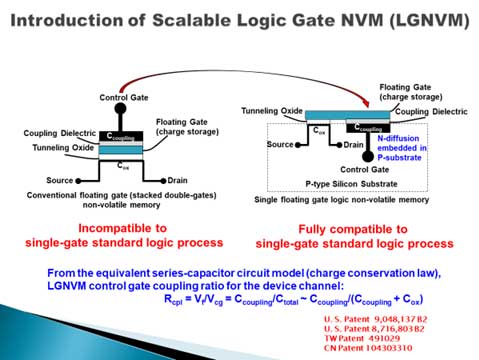

┴└ż”▒■├ō╩¼╠Ņż¼┴╚ż▀╣■ż▀ÅUż╦╣╩ż├ż┐ż╬żŽĪóźĒźĖź├ź»źūźĒź╗ź╣ż╚ż╩żĖż▀ż╬╬╔żżźßźŌźĻźūźĒź╗ź╣ż╦żŪżŁżļż½żķż└ĪŻ╬Ńż©żąĪóźĘź¾ź░źļź▌źĻźĘźĻź│ź¾ź▓Ī╝ź╚ż╬źĒźĖź├ź»źūźĒź╗ź╣ż╚ż╬Ė▀┤╣└Łż“Ęeż┐ż╗żļż┐żßż╦Īó┐▐5ż╬żĶż”ż╩╣Įļ]ż“ŲDżļż│ż╚ż¼żŪżŁżļĪŻ

┐▐5ĪĪ2┴žż╬ź▌źĻźĘźĻź│ź¾╣Įļ]ż╬æųŖõż“╩┐ĀCæųż╦▓╝żĒżĘż┐╣Įļ]ż╬źĒźĖź├ź»ż╚Ė▀┤╣└Łż╬żóżļź╗źļ╣Įļ]ĪĪĮąųZĪ¦├µÜW╣░▒¦

æųż╬┐▐żŽ2┴žź▌źĻźĘźĻź│ź¾ź▓Ī╝ź╚ż╬źšźĒĪ╝źŲźŻź¾ź░ź▓Ī╝ź╚ż“Č”─╠ż╦żĘżŲĪóæųż╬öUĖµź▓Ī╝ź╚ż“ź½ź├źūźĻź¾ź░źŁźŃźčźĘź┐¤©▓Į╦ņż“▓żĘżŲ┤łŖõż╦Ęeż├żŲżŁż┐╣Įļ]ż“┐āżĘżŲżżżļĪŻź▓Ī╝ź╚¤©▓Į╦ņż╬źņźżźõĪ╝ż¼ź▓Ī╝ź╚ź╚ź¾ź═źļ¤©▓Į╦ņż╚Īóź½ź├źūźĻź¾ź░źŁźŃźčźĘź┐¤©▓Į╦ņż“Ų▒żĖŪ÷żĄż╦ż╣żņżąĪó2┴žź▌źĻż“Ų¾ż─ż╦╩¼ż▒żŲ╩┐ĀCż╦╩┬ż┘żŲÅøż»żĶż”ż╩╣Įļ]ż╦ż╩żļĪŻż┐ż└żĘĪóź½ź├źūźĻź¾ź░¤©▓Į╦ņż└ż▒Š»żĘĖ³ż»ż╣żļż│ż╚żŌį~├▒ż╦żŪżŁżļĪŻż│ż╬╣Įļ]ż└ż╚źĒźĖź├ź»├ōż╬MOSFETźūźĒź╗ź╣ż╚Ė▀┤╣└Łż¼╩▌ż┐żņżļĪŻ

źŪźąźżź╣ż╬×æļ]żŽĪ󱜎čż╬UMCż╚├µ╣±ż╬źšźĪź”ź¾ź╔źĻGrace Semiconductorż╦░══Ļż╣żļĪŻ1ŃQ░╩ŲŌĪóż╣ż╩ż’ż┴20ŃQ¼Źż▐żŪż╦×æēä▓Įż╦ż│ż«ż─ż▒ż┐żżż╚żĘżŲżżżļĪŻ┴╚ż▀╣■ż▀├ōNORźšźķź├źĘźÕżŽĪóNANDż█ż╔ż╬═Ų╬╠ż¼═ūżķż╩żżź»źļź▐ż╬ECUżõź╣ź╚źņĪ╝źĖ░╩│░ż╬├ō²ŗżŪĄßżßżķżņżļĪŻż┐ż└żĘĪóča┼┘╗┼══ż“╦■’BżŪżŁżļż½ż╔ż”ż½żŽż│żņż½żķż╬ĖĪŲżż╚ż╩żļĪŻż│żņż▐żŪNANDźšźķź├źĘźÕżõDRAMżŪ▄f╣±żõŲ³╦▄Īóä▌╣±ż╬ĖÕż“╝{ż”źėźĖź═ź╣ż“·t│½żĘżŲżŁż┐ż¼Īóż│ż╬┐ĘĘ┐NORźšźķź├źĘźÕżŽĮķżßżŲż╬├µ╣±Ų╚śOż╬źßźŌźĻČ\Įčż╚żżż©żļĪŻ