AMATĪó3D╣Įļ]ż╬FinFETĪóNANDźšźķź├źĘźÕż╦Ė■ż▒┐ĘCMPż╚CVDż“╚»╔Į

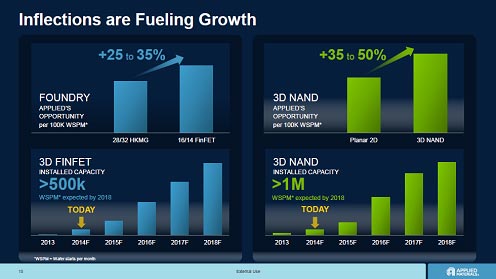

Applied MaterialsżŽĪóźĒźĖź├ź»Ė■ż▒ż╬FinFETźūźĒź╗ź╣ĪóźßźŌźĻĖ■ż▒ż╬3D NANDźšźķź├źĘźÕźūźĒź╗ź╣ż╚żżż”Įj(lu©░)żŁż╩Ų¾ż─ż╬3╝ĪĖĄ╣Įļ](┐▐1)ż“╝┬ĖĮż╣żļż┐żßż╬źūźĒź╗ź╣äóÅøĪ¦ CMPĪ╩▓Į│ž┼¬ĄĪ│Ż┼¬Ė”╦ßĪ╦ż╚CVDĪ╩▓Į│ž┼¬Ąż┴Ļ└«─╣Ī╦ż╬┐Ę×æēäż“╚»╔ĮżĘż┐ĪŻ

![┐▐1ĪĪź╣ź▐ź█ż╬źŁźŌż╚ż╩żļ3╝ĪĖĄ╣Įļ]źŪźąźżź╣FinFETż╚3D NANDĪĪĮąųZĪ¦Applied Materials](/archive/editorial/technology/img/TFE140715-01a.jpg)

┐▐1ĪĪź╣ź▐ź█ż╬źŁźŌż╚ż╩żļ3╝ĪĖĄ╣Įļ]źŪźąźżź╣FinFETż╚3D NANDĪĪĮąųZĪ¦Applied Materials

AMATżŽĪóż│żņż½żķż╬╚ŠŲ│öü▌xŠņż“ĖŻ░·ż╣żļź©źņź»ź╚źĒź╦ź»ź╣żŽżõżŽżĻź╣ź▐Ī╝ź╚źšź®ź¾żŪżóżĻĪóżĮż╬▌xŠņżŽ2017ŃQż╦żŽ70▓»±śż╦żŌ├Żż╣żļĪóż╚Ė½żŲżżżļĪŻż│żņż“ĖŻ░·ż╣żļ╚ŠŲ│öüź┴ź├źūżŽźóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄż╚NANDźšźķź├źĘźÕźßźŌźĻżŪżóżļĪŻż╔ż┴żķżŌ3╝ĪĖĄ▓Įż╣żļöĄ(sh©┤)Ė■ż╦żóżļĪŻźóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄż╬║Ū└Ķ├╝żŽ20nmż╬źūźņĪ╝ź╩źūźĒź╗ź╣żŪżóżļż¼ĪóżĮż╬╝Īż╬14/16nm└ż┬ÕżŽFinFETČ\Įčż╦╣įż»ż╚Ė½żļĖ■żŁż¼¾HżżĪŻż▐ż┐NANDźšźķź├źĘźÕżŽĪóźßźŌźĻź╗źļż“▓ŻöĄ(sh©┤)Ė■ż╦║ŅżĻ╣■ż¾żŪżŁż┐ż│żņż▐żŪż╬źūźĒź╗ź╣ż╦×┤żĘżŲĪóź╗źļż“āeöĄ(sh©┤)Ė■ż╦└čżÓż│ż╚żŪĮĖ└č┼┘ż“æųż▓żļöĄ(sh©┤)Ė■ż╦Ė■ż½ż├żŲżżżļĪŻSamsungżŽ3D NANDż“Įą▓┘żĘżĮżņż“╗╚ż├ż┐SSDż“║“ŃQż╣żŪż╦╚»╔ĮżĘżŲżżżļ(╗▓╣═½@╬┴1)ĪŻ║ŻŃQżŽ║“ŃQż╬24┴žż½żķĪó▐k╩Ō┐╩ż¾żŪ32┴žż╬źßźŌźĻż“│½╚»żĘżŲżżżļĪŻż│ż╬ż┐żßĪóAMATżŽ3╝ĪĖĄ╣Įļ]ż“▓├╣®ż╣żļż┐żßż╬äóÅø│½╚»ż╦╬üż“Ų■żņżŲżŁż┐ĪŻż│ż╬└ĶżŌFinFETż╚3D NANDźšźķź├źĘźÕ├ōź”ź¦Ī╝źŽżŽ╗\▓├żĘżŲżżż»ż╚AMATżŽĖ½żŲżżżļ(┐▐2)ĪŻ

┐▐2ĪĪ3D FinFETż╚3D NANDźšźķź├źĘźÕż╬ź”ź¦Ī╝źŽżŽ╗\ż©żŲżżż»ĪĪĮąųZĪ¦Applied Materials

3╝ĪĖĄ╣Įļ]ż“▓├╣®ż╣żļż│ż╚żŽį~├▒żŪżŽż╩żżĪŻFinFETżŪżŽĖČ╗ę┴žźņź┘źļż╬Ė³żĄż╬Ū÷╦ņż“Ę┴└«żĘż╩ż▒żņżąż╩żķż╩żżĪŻżĮż╬ż┐żßż╬┐ĘCVDäóÅøĪóApplied Producer XP PrecisionżŽ└«╦ņż╬╗@┼┘ż“æųż▓Īó║Ó╬┴ż╬’L(f©źng)┤┘ż╩ż╔ż╬▓▌¼öż“▓“»éż╣żļż╚żżż”ĪŻFinFETźūźĒź╗ź╣żŪżŽĪó10nm░╩æTż╬ź╚źķź¾źĖź╣ź┐ż╦żŽFinFETż╬ź┴źŃź¾ź═źļż╦źŁźŃźĻźõöĪŲ░┼┘ż╬╣ŌżżIII-V▓Į╣ńر╚ŠŲ│öüż“?q©▒)\└迥ż╗żļČ\Įčż“╗╚ż”ż│ż╚ż╦ż╩żĒż”ĪŻż│ż╬ż┐żßĪóCVDź©źįź┐źŁźĘźŃźļäóÅøżŌ’L(f©źng)ż½ż╗ż╩żżĪŻäóÅøż╬Š▄║┘żŽ£½żķż½ż╦żĘżŲżżż╩żżĪŻ

NANDżŪżŽĪó60:1ż╚Č╦żßżŲźĘźŃĪ╝źūż╩źóź╣ź┌ź»ź╚╚µż╬ź│ź¾ź┐ź»ź╚╣”ż“▓├╣®żĘ┼┼Č╦ż“ż─ż╩ż▓ż┐ĖÕĪóCMPżŪ╩┐┘Q(m©żo)ż╦▓├╣®ż╣żļØŁ═ūż¼żóżļĪŻCMP╣®µćżŽĪóFinFETż╚3D NANDżŪżŽ║ŪĮj(lu©░)10╣®µćżŌ╗╚ż’żņżļ▓─ē”└Łż¼żóżļż╚ż╣żļĪŻ║ŻövAMATż¼╚»╔ĮżĘż┐ź─Ī╝źļReflexion LK Primeż╦żŽĪó6ż─ż╬Ė”╦ßź╣źŲĪ╝źĘźńź¾ż╚8ż─ż╬¹ÉŠ¶ź╣źŲĪ╝źĘźńź¾ż“Ęeż─ĪŻź╩ź╬źßĪ╝ź╚źļ╗@┼┘żŪż╬3╝ĪĖĄź▓Ī╝ź╚ż╬╣ŌżĄöU(ku©░)ĖµżŪżŽĪóČč▐k└Łż¼“£═ĶżĶżĻżŌ50Ī¾Ė■æųżĘż┐ż╚żĘżŲżżżļĪŻµ£14ź╣źŲĪ╝źĘźńź¾ż╬╣®µćż“╣įż”ż╚żĘżŲĪó“£═ĶĄĪ¹|ż╚╚µż┘żļż╚Īóź╣źļĪ╝źūź├ź╚żŽ2Ū▄ż╦æųż¼żļż╚żżż”ĪŻ

ż╩ż¬ĪóAMATżŽ║ŻĖÕ┼²╣ńż╣żļ┼ņ»Bź©źņź»ź╚źĒź¾ż╚ż╬┐Ę▓±╝ęż╬ć@Øiż“ĪųEterisĪūż╦ż╣żļż╚╚»╔ĮżĘżŲżżżļĪŻEterisĪ╩ź©źŲźĻź╣Ī╦żŽĪóEternal Innovation for Societyż½żķżŁżŲżżżļĪŻ

╗▓╣═½@╬┴

1. źĄźÓź╣ź¾Īó3╝ĪĖĄNANDż“64Ė─┼ļ║▄żĘż┐SSDż“╬╠ŠÅ│½╗Ž (2013/08/15)