AIż╬└čŽ┬▒ķōQż╦Š«żĄż╩DSPż“┐¶╝åĖ─╩┬ż┘ż┐IPź│źóż¼¶öĪ╣┼ąŠņ

źŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░ż╬ź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»╣įš`▒ķōQż╦«Ć╩┬š`DSPövŽ®ż“ŠW├ōż╣żļIPż¼CEVAż╦¶öżŁĪóFlex Logixż½żķżŌĮążŲżŁż┐ĪŻź©ź├źĖAIź┴ź├źūż╦ĮĖ└čż╣żļż┐żßż╬IPź│źóżŪżóżļĪŻź╦źÕĪ╝źķźļź═ź├ź╚ż╬▒ķōQżŪżŽ8źėź├ź╚żõ16źėź├ź╚ż╬żĶż”ż╦Š«żĄż╩└čŽ┬▒ķōQĪ╩MACĪ╦ż¼┼¼żĘżŲżżżļż┐żßĪóŠ«żĄż╩DSPż“Įj╬╠ż╦ĮĖ└čżĘżŲżżżļĪŻ

ź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»żŪżŽĪó┤╦▄┼¬ż╦1Ė─ż╬ź╦źÕĪ╝źĒź¾ż╦└čŽ┬▒ķōQĪ╩źŪĪ╝ź┐Ī▀─_ż▀Ī╦ż¼¾H┐¶żųżķ▓╝ż¼żļ¾HŲ■╬ü1Įą╬üż╬źčĪ╝ź╗źūź╚źĒź¾ż“źŌźŪźļż╦żĘżŲżżżļĪŻż┐ż└żĘĪóĮą╬üż¼1ż─żŪżŌ¾H┐¶ż╬ź╦źÕĪ╝źĒź¾ż╦źŪĪ╝ź┐ż“┼┴├ŻżĘżŲżżż»ż┐żßĪó┼┼╗ęövŽ®ż╬źšźĪź¾źóź”ź╚Įą╬üż¼ĮążŲżżżļżĶż”ż╩źŌźŪźļż“╗╚ż├żŲżżżļĪŻż│ż╬ż┐żßĪóAIź┴ź├źūżõIPövŽ®żŪżŽĪó└čŽ┬▒ķōQĪ╩MAC: Multiply AccumulationĪ╦ż“¾H┐¶╩┬ż┘ż┐╣Įļ]ż“żĘżŲżżżļĪŻĖĄĪ╣GPUĪ╩ź░źķźšźŻź├ź»ź╣źūźĒź╗ź├źĄĪ╦ż╦żŽMACż¼ĮĖ└迥żņżŲż¬żĻĪóżĘż½żŌ«Ć╩┬š`ż╚Ė└ż©żļż█ż╔Š«żĄż╩GPUź│źóż¼ĮĖ└迥żņżŲżżżļż┐żßĪóNvidiaż╬GPUż¼ź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»ż╬▒ķōQż╦żĶż»╗╚ż’żņżŲżżżļĪŻ

żĘż½żĘĪóMACż“ĮĖ└čżĘżŲżżżļ┼└żŪżŽDSPżŌŲ▒żĖż└ĪŻDSPżŽ└čŽ┬▒ķōQ└ņ├ōż╬ź▐źżź»źĒźūźĒź╗ź├źĄż└ż½żķżŪżóżļĪŻż┐ż└żĘĪóż│żņż▐żŪż╬DSPżŽĪó▒ķōQ╗@┼┘ż“─_£åż╣żļż┐żßĪó32źėź├ź╚ż“┤╦▄ż╬├▒╗@┼┘ż╚żĘżŲ64źėź├ź╚ż╬Ū▄╗@┼┘ż╩ż╔ż╬╗@╠®ż╩▒ķōQż╦Ė■ż▒żķżņżŲżżż┐ĪŻDSPżŽĪóFFTĪ╩╣ŌÅ]źšĪ╝źĻź©╩č┤╣Ī╦ż╩ż╔ż╬żĶż”ż╩─╠┐«źŌźŪźÓ▒ķōQż╦Ė■żżżŲżżż┐ĪŻżĘż½żĘĪóAIź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»ż╦╗╚ż”ź╦źÕĪ╝źĒź¾źŌźŪźļżŪżŽĪó╣Ō╗@┼┘żĶżĻżŌŠ«żĄż╩MACż“ØÖŠ’ż╦¾H┐¶╩┬ż┘żļöĄż¼Ė■żżżŲżżżļĪŻż│ż╬ż┐żßĪó8Ī▀16źėź├ź╚ż╚ż½7Ī▀7źėź├ź╚ż╬żĶż”ż╩Š«żĄż╩DSPż“ź╦źÕĪ╝źĒź¾ż╬┐¶ż└ż▒Įj╬╠ż╦ĮĖ└čżĘżŲżżżļĪŻ

żŌż╚żŌż╚DSPź│źóż“ź╗Ī╝źļź╣ź▌źżź¾ź╚ż╚żĘżŲżŁż┐IPź┘ź¾ź└Ī╝ż╬CEVAżŽĪó║ŪŖZAIĖ■żŁż╬Š«æä╠ŽĪ”Įj╬╠ż╬DSPövŽ®ż“╩┬ż┘ż┐IPź│źóż“└Ķ╣įżĘżŲźĻźĻĪ╝ź╣żĘżŲżŁż┐ĪŻśOŲ░▒┐┼Š┘Zż╩ż╔▓ĶćĄŪ¦╝▒ż╬żĶż”ż╩▒■├ōżŪżŽĪó└@├ōż╬DSPż╚żżż”żĶżĻżŽ▓ĶćĄĪ”▒ŪćĄ├ōż╬DSPź│źóż╚żĘżŲCEVA-XM4×æēäżõĪ󿥿ķż╦▒Ū楿╚└@├ōźŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░├ōż╬DSPź│źóż╚żĘżŲCEVA-XM6×æēäż¼żóżļĪŻ6ĘŅż╦żŽĪóź╔źĒĪ╝ź¾żõźĒź▄ź├ź╚Ė■ż▒ż╬AI SoCż“└▀╝ŖżĘżŲżżżļ├µ╣±ż╬źšźĪźųźņź╣╚ŠŲ│öüźßĪ╝ź½Ī╝Artosyn Microelectronicsż╦źķźżź╗ź¾ź╣ČĪ═┐żĘż┐ż╚╚»╔ĮżĘżŲżżżļĪŻ

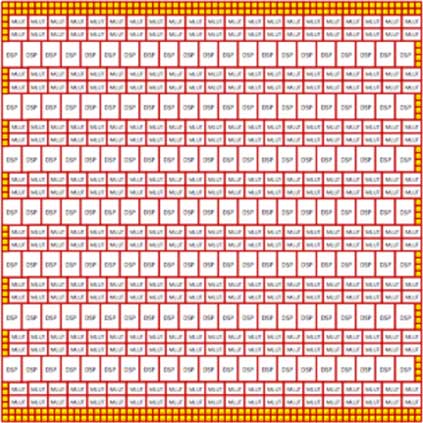

┐▐1ĪĪFlex Logixż╬AI├ōIPź│źóEFLX4K AIźĘźĻĪ╝ź║ż╦żŽ┐¶╝åĖ─ż╬Š«żĄż╩DSPż“ĮĖ└čĪĪĮąųZĪ¦Flex Logix Technologies╝ę

ż│żņż╦×┤żĘFlex Logix Technologies╝ęż¼źĻźĻĪ╝ź╣żĘż┐AI├ōIPź│źóĪ╩EFLX4K AIźĘźĻĪ╝ź║Ī╦żŽĪó┐¶╝åĖ─ż╬DSPź│źóż╚öUĖµövŽ®ż“ĮĖ└čżĘżŲż¬żĻĪóź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»▒ķōQ└ņ├ōż╬övŽ®ż╚ż╩ż├żŲżżżļĪŻCEVAż╬żĶż”ż╩DSPź│źóż“╝ń╬üż╚żĘżŲżŁż┐┤ļČ╚ż╚░ŃżżĪóFlex LogixżŽ┴╚ż▀╣■ż▀FPGAĪ╩eFPGAż╚Ō}żųĪ╦ż“╝ń╬üż╚żĘżŲżŁż┐ĪŻżĮż╬źóĪ╝źŁźŲź»ź┴źŃżŽĪó¾H┐¶ż╬DSPź│źóĪ▄FPGAż╬IPź│źóż╚ż╩ż├żŲżżżļĪŻ

AIż╬źóźļź┤źĻź║źÓżŪżŽĪó║ŻżŽ▓Ķ楿õ▒ŪćĄŪ¦╝▒żõ▓╗╠mŪ¦╝▒ż╬żĶż”ż╩źčź┐Ī╝ź¾Ū¦╝▒ż╦ÅRų`ż¼ĮĖż▐ż├żŲżżżļż┐żßĪóøQż▀╣■ż▀ź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»ż╦┼¼żĘż┐MACövŽ®ż¼¾H├ōżĄżņżŲżŁż┐ĪŻżĘż½żĘĪóźŪźŻĪ╝źūźķĪ╝ź╦ź¾ź░ż╬ź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»żŽ┐═┤ųż╬Įj╦N╚ķ䮿“źŌźŪźļ▓ĮżĘż┐żŌż╬żŪĪóĮj╦N╚ķ䮿Ž£å│ążõ─░│ąĪó╣įŲ░öUĖµĪóĖ└ĖņŪ¦╝▒ż╩ż╔ż“ż─ż½żĄż╔żļ┴╚“Eż╚Ė└ż’żņżŲżżżļĪŻ╦NżŽżĮżņ░╩│░ż╦żŌź╣ź╚Ī╝źĻĪ╝└Łż╬żóżļź©źįźĮĪ╝ź╔ż“ĄŁ▓▒żĘżŲżżżļķLĖ[żõĪóŠ}’Bżõ┐╚öüż╬▒┐Ų░ż“╗@Õ╠ż╦öUĖµż╣żļŠ«╦Nż╩ż╔┬Šż╬┴╚“EżŌ¾HżżĪŻ║ŻĖÕĪó╦Nż“ż╔ż╬żĶż”ż╦źŌźŪźļ▓Įż╣żļż½ż╦żĶż├żŲĪóź╦źÕĪ╝źķźļź═ź├ź╚ź’Ī╝ź»ż╬źŌźŪźļż└ż▒ż¼┼¼żĘżŲżżżļż╚żŽĖ┬żķż╩żżĪŻż╔ż╬żĶż”ż╩źŌźŪźļż╦żŌ└ņ├ōövŽ®żŪ╔ĮĖĮżŪżŁżļźŪźąźżź╣ż¼FPGAżŪżóżļż½żķĪóźóźļź┤źĻź║źÓżõżĮż╬öUĖµż“övŽ®żŪ╔ĮĖĮż╣żļFPGAż“╗─żĘż┐ż”ż©żŪ«Ć╩┬š`ż╬DSPż“ĮĖ└čżĘż┐źŪźąźżź╣żŽ║ŻĖÕżŌÖ┌żŁ╗─żļ▓─ē”└ŁżŽ╣ŌżżĪŻ

║ŻövFlex Logixż¼źķźżź╗ź¾ź╣▓─ē”ż╩IPź│źóż╚żĘżŲźĻźĻĪ╝ź╣żĘż┐EFLX4K AI eFPGAź│źó×æē俎Īó8źėź├ź╚ż╬MACżõ16źėź├ź╚MACż“śOĮyż╦╣Į└«▓─ē”ż╦ż╩ż├żŲż¬żĻĪó╬Ńż©żą16Ī▀8źėź├ź╚ż╩ż╔żŌ▓─ē”żŪżóżļĪŻEFLX4K AIź│źóżŽ16nmźūźĒź╗ź╣ż╩żķ441Ė─ż╬8źėź├ź╚MACż“Ęeż─1.2╩┐öĄmmż╬ź│źóż╚ż╩żĻĪó1GHzżŪŲ░║Ņż╣żļĪŻMAC▒ķōQż╬ź╣źįĪ╝ź╔żŽĪóź’Ī╝ź╣ź╚ź▒Ī╝ź╣żŪ441 GMAC/╔├ż╬ź╣źļĪ╝źūź├ź╚ż“Ęeż─ĪŻ7Ī▀7źėź├ź╚╣Į└«ż╦ż╣żļż╚22 TMAC/╔├ż╚żżż”└Łē”ż¼įużķżņżļż╚ż▀żŲżżżļĪŻIPź│źóŲŌż╬Ū█└■ż╦żŽŲ▒╝ęż╬XFLXŪ█└■Č\Įčż“╗╚ż├żŲĀC└čĖ·╬©ż¼╣Ōż»Īóż½ż─║Ų╣Į└«▓─ē”ż╩övŽ®ż“╣Į└«żŪżŁżļż╚żżż”ĪŻ

ż│ż╬IPź│źóż“╗╚ż├żŲSoCż“└▀╝Ŗż╣żļŠņ╣ńż╦żŽĪóEFLX Compilerż¼╗╚ż©Īó┘J┘Tż╬źĮźšź╚ź”ź©źóźšźĒĪ╝ż¼źĄź▌Ī╝ź╚żĘżŲżżżļĪŻż│ż╬ź│źóżŽ6Ī┴8ź§ĘŅżóżņżąż╔ż╬żĶż”ż╩źūźĒź╗ź╣żžżŌźżź¾źūźĻźßź¾ź╚żŪżŁżļż╚żżż”ĪŻFlex LogixżŽĖĄ┼ņėøż╬ź©ź¾źĖź╦źóż└ż├ż┐Ė┼æčŲ®Ģ■ż¼Ų³╦▄╦Ī┐═ż╬╝ę─╣ż“ē»żßżļ▓±╝ęĪŻ