╩Ż┐¶ż╬ź©ź¾źĖź╦źóż¼Ų▒╗■ż╦övŽ®┐▐Ų■╬üżŪżŁżļź▀ź»ź╣ź╚źĘź░ź╩źļ└▀╝Ŗź─Ī╝źļ

ä▌(sh©¼)źßź¾ź┐Ī╝Ī”ź░źķźšźŻź├ź»ź╣Ī╩Mentor GraphicsĪ╦╝꿎Īóźóź╩źĒź░ż╚ź▀ź»ź╣ź╚źĘź░ź╩źļ├ōż╬└▀╝Ŗź─Ī╝źļżŪżóżļPyxisż“╚»╔ĮżĘż┐ĪŻż│żņżŽ“£═ĶŲ▒╝ęż¼ICStationż╚żżż”ć@Š╬żŪ×æēä▓ĮżĘżŲżżż┐źóź╩źĒź░└▀╝Ŗź─Ī╝źļż“▓■╬╔ĪóövŽ®ż╬ź½ź╣ź┐ź▐źżź║ż“į~├▒ż╦żŪżŁżļżĶż”ż╦żĘ─ŠćĶ┼¬ż╩GUIż╦ü÷ż©ż┐żŌż╬ĪŻ

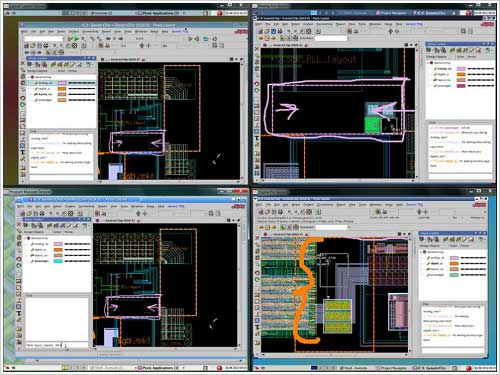

┐▐1ĪĪPyxisövŽ®┐▐Ų■╬ü▓ĶĀCĪĪĮąųZĪ¦Mentor Graphics

PyxisĪ╩źįź»źĘź╣ż╚╚»▓╗Ī╦żŽövŽ®┐▐Ų■╬üż╚źņźżźóź”ź╚żõźšźĒźóźūźķź¾ż“╣įż”ź─Ī╝źļżŪżóżļĪŻź▐ź╦źÕźóźļż╩żĘżŪ╗╚ż©żļż│ż╚ż“Ū░Ų¼ż╦ÅøżżżŲżżżļĪóż╚Ų▒╝ęDeep Submicron Division, Product marketing managerż╬Tom DaspitĢ■(hu©¼)żŽĖ└ż”ĪŻż│ż╬ź─Ī╝źļżŽ└▀╝ŖövŽ®Ų■╬üż╚źĘź▀źÕźņĪ╝źĘźńź¾ż╬└▀─Ļżõź┴ź¦ź├ź»ż¼▓─ē”żŪĪ󿥿ķż╦└▄¶ö└Łż“─_£åżĘż┐źņźżźóź”ź╚ź©źŪźŻź┐Ī╝żŌ┤▐żÓĪŻż▐ż┐Īóź┐źżź▀ź¾ź░ż“╣═╬ĖżĘż┐źķź”ź┐Ī╝ĄĪē”żŌżóżļĪŻ

źŪźČźżź¾ź╣ź▒ź▐źŲźŻź├ź»Ī╩övŽ®┐▐Ī╦Ų■╬ü▓ĶĀCżŪżŽĪó═ź└Ķ┼┘ż╬╣ŌżżĄĪē”ż“æų░╠ż╦╔Į┐āż╣żļżĶż”ż╦żĘżŲżżżļĪŻ┼┼Ąż┼¬ż╩źļĪ╝źļź┴ź¦ź├ź»żŽżŌż┴żĒż¾Īó┤¾Ö┌┴Ū╗ęż“Ė½└čżŌżļż│ż╚żŌżŪżŁĪóźņźżźóź”ź╚Øiż╬źĘź▀źÕźņĪ╝źĘźńź¾źŪĪ╝ź┐ż½żķövŽ®┐▐żõźņźżźóź”ź╚ĖÕż╬SPICEźĘź▀źÕźņĪ╝źĘźńź¾ż¼żŪżŁĪóźŪźąź├ź░ż“źżź¾ź┐źķź»źŲźŻźųż╦╣įż©żļĪŻ

ØŖż╦ż│ż╬ź─Ī╝źļ║ŪĮj(lu©░)ż╬ØŖ─╣żŽĪó╩Ż┐¶ż╬└▀╝ŖŪvż¼▐kż─ż╬ź╗źļżŪŲ▒╗■ż╦└▀╝ŖżŪżŁżļż│ż╚ż└ĪŻ└▀╝Ŗż╣ż┘żŁź©źĻźóż“─Ļ▒IżĘżŲ└▀╝ŖŪvŲ▒╗╬ż¼Ų▒żĖ▐kż─ż╬źŪĪ╝ź┐ź┘Ī╝ź╣æųżŪĪóżĮżņżŠżņŲ▒╗■ż╦└▀╝ŖżŪżŁżļż┐żßĪó└▀╝Ŗ╗■┤ųż╬ø]Į╠ż╦ż╩żļĪŻźĒĪ╝ź½źļŪ█└■æųżŪżŌź░źĒĪ╝źąźļŪ█└■æųżŪżŌĪóśO╩¼ż¼├┤┼÷żŪżŁżļŪ█└■─╣ż╬ź©źĻźóżĄż©─Ļ▒Iż╣żņżą╩Ż┐¶ż╬ź©ź¾źĖź╦źóż¼Ų▒╗■ż╦└▀╝ŖżŪżŁżļĪŻżĘż½żŌĪó▓ĶĀCż╦żŽź┴źŃź├ź╚ż╣żļź”źŻź¾ź╔ź”żŌżóżĻĪó└▀╝ŖżĘż╩ż¼żķź©ź¾źĖź╦źóŲ▒╗╬żŪÅBż¼żŪżŁżļĪŻźĻźóźļź┐źżźÓżŪÅBżĘż╩ż¼żķ└▀╝ŖżŪżŁżļż┐żßĪó┤ų░Ńżżż╬╚»Ö┌żõĖĒ▓“żŽż░ż├ż╚Š»ż╩ż»ż╩żļĪŻ

┐▐2ĪĪśO╩¼żŪ└▀╝ŖżĘż┐żżź©źĻźóż“─Ļ▒Iż╣żļĪĪĮąųZĪ¦Mentor Graphics

Ū█ÅøŪ█└■ż╦┤žżĘżŲżŽĪóź╚źķź¾źĖź╣ź┐Īóź╗źļĪóźųźĒź├ź»Īóź┴ź├źūż╚żżż”ĘQźņź┘źļżŪż╬źóź╩źĒź░övŽ®Īóź▀ź»ź╣ź╚źĘź░ź╩źļövŽ®ż╬Ū█└■ż“śOŲ░┼¬ż╦╣įż”ĪŻŪ█└■ż╣żļ╗■ż╬öU(ku©░)╠¾ż“└▀ż▒ż┐źļĪ╝źļź▄ź├ź»ź╣ż╦żĶż├żŲµ£öü┼¬ż╩ź░źĒĪ╝źąźļŪ█└■żŪżŽ║«╗©ż“▓“Š├żĘĪó║┘ŗż╬Ū█└■żŪżŽź═ź├ź╚ż┤ż╚ż╦šl╔┘ż╩öU(ku©░)╠¾ż“└▀ż▒ż┐ĄĪ╣Įż“╗╚ż”ĪŻTSMCż╬28nmźūźĒź╗ź╣Ū¦─Ļż“£pż▒żŲżżżļĪŻ

źņźżźóź”ź╚Į¬╬╗ĖÕż╬ĖĪŠ┌żŪżŽĪóźßź¾ź┐Ī╝ż╬ĖĪŠ┌ź─Ī╝źļż╬Calibreż¼źąź├ź»ź░źķź”ź¾ź╔żŪ╬«żņżŲż¬żĻĪóź©źķĪ╝ż“Ė½ż─ż▒żļż╚ż╣ż░ż╦T┘ćżŪżŁżļżĶż”ż╦ż╩ż├żŲżżżļĪŻ

ż│ż╬ź─Ī╝źļż“╗╚ż├żŲźšźĪź”ź¾ź╔źĻżž░══Ļż╣żļŚlż└ż¼Ī󟥟▌Ī╝ź╚żĄżņżŲżżżļ¾Hż»ż╬źšźĪź”ź¾ź╔źĻż“┬ō(li©ón)ż┘żļæųż╦ĪóżĮż╬źżź¾ź┐Ī╝ź¬ź┌źķźėźĻźŲźŻżŌżĘż├ż½żĻźĄź▌Ī╝ź╚żĄżņżŲżżżļĪŻ±śŽčż╬TSMCżõUMCżŽżŌż┴żĒż¾Īóä▌(sh©¼)╣±ż╬IBMżõGlobalFoundriesĪóOn SemiconductorĪóź╔źżź─ż╬XFABżõLFoundryĪó▄f╣±ż╬Dongbu HiTekżõMagnaChipĪó├µ╣±SMICĪóźżź╣źķź©źļTowerJazzż╬ĘQźšźĪź”ź¾ź╔źĻ┤ļČ╚ż╦źĄź▌Ī╝ź╚żĄżņżŲżżżļĪŻ▓├ż©żŲĪóźßź¾ź┐Ī╝ż╬PDKĪ╩Process Design KitĪ╦ż└ż▒żŪżŽż╩ż»ź▒źżźŪź¾ź╣ż╬PDKĪ╩ż┐ż└żĘ ╩č┤╣ż¼ØŁ═ūĪ╦żõiPDKż╩ż╔żŌźĄź▌Ī╝ź╚żĘżŲżżżļĪŻźŪźČźżź¾źŁź├ź╚ż“ż│żņż½żķ║YØŹ▓Įż╣żļż┐żßż╬OpenPDKż╦żŌ╗▓▓├żĘżŲż¬żĻĪóźßź¾ź┐Ī╝żŽżĮż╬└▀╬®źßź¾źąĪ╝żŪżŌżóżļĪŻ

ż┴ż╩ż▀ż╦ż│ż╬Pyxisż╚żŽĪóźķźŲź¾ĖņżŪķLż╬ÆņķLż╦╗╚ż”ĪóĪų×│┐╦╚ūĪūĪóź«źĻźĘźŃĖņżŪĪųŠ«żĄż╩╚óĪūż“┴T╠Żż╣żļĖ└±äż└ż╚żżż”ĪŻż▐ż┐ŲŅż╬└▒║┬ż╬ć@ØiżŪĪó┘ć╝░ć@Š╬Pyxis NauticaĪ╩Č”ż╦×│┐╦╚ūż╬┴T╠ŻĪ╦ż╚Ō}żųŠ«żĄż╩└▒║┬żŌżóżļĪŻż│ż╬└▒║┬żŽ┘ć╝░ć@ż½żķ╝Īŗīż╦ø]ż»ż╩żĻĪó├▒ż╦Pyxisż╚Ō}żųżĶż”ż╦ż╩ż├ż┐ż╚żĘżŲżżżļĪŻ

┐▐3ĪĪŲŅż╬ȧż╦«ö(d©Īng)ż»└▒║┬ĪĪż│ż╬┐┐ż¾├µż╦żóżļż╬ż¼Pyxis