ź’źżźõźņź╣Īó─ŃŠ├õJ┼┼╬ü╩¼╠Ņżžż╬ÅR╬üżŪ╦ĶŃQ└«─╣żĘżŲżŁż┐├µŠ«EDAź┘ź¾ź└Ī╝

EDAČ╚─cż╦żŽ70Ī┴80╝ęż¼╗▓Ų■żĘżŲżżżļż╚Ė└ż’żņżŲżżżļĪŻź▒źżźŪź¾ź╣ĪóźĘź╬źūźĘź╣Īóźßź¾ź┐Ī╝ż╬ä▌╣±źėź├ź░3╝ęż└ż▒żŪżŽż╩żżĪŻ╗■╬«ż╦ŠĶżĻ└«Ė∙żĘżŲżżżļ├µŠ«ż╬2╝ęż“Šę▓żĘżĶż”ĪŻ╣Ō╝■āSż╬EDAź─Ī╝źļż“┴└ż”AWR╝ęż╚Īó─ŃŠ├õJ┼┼╬üż╬└▀╝Ŗź─Ī╝źļż╦╣╩ż├ż┐źóźčź├ź┴╝ężŪżóżļĪŻżżż║żņżŌØŖÖzż╩EDA×æēäżŪżŽżóżļż¼Īó└«─╣╩¼╠Ņż╦┴└żżż“─Ļżßż┐×æēäż“─¾ČĪżĘżŲżżżļĪŻ

┐▐1ĪĪAWRź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷Sherry HessĢ■

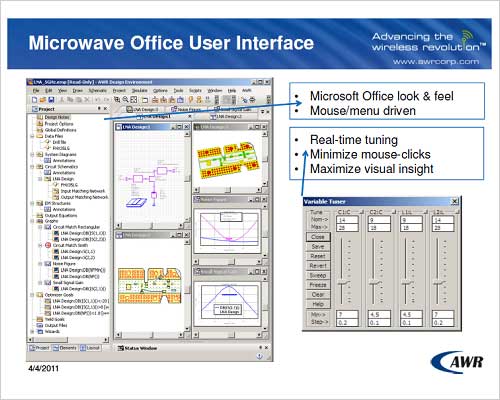

ź▐źżź»źĒāS▓“└Žż½żķź╬źżź║▓“└Žż▐żŪGUIżŪĖ½żõż╣ż»

AWR╝ęż¼ÅR╬üż╣żļż╬żŽĪóFM╝■āS┐¶ż½żķ┐¶╝åGHzż▐żŪż╬╣Ō╝■āSōļ░Ķż╬övŽ®└▀╝Ŗź─Ī╝źļĪŻŲ▒╝ęż╬┴└żżżŽĘ╚┬ė┼┼ÅBżõĘ╚┬ė├╝¼ŹĪó─╠┐«Č\ĮčĪóśOŲ░┘ZżõÆņȧ▒¦├ĶČ\Įčż╩ż╔ż│żņż½żķ└«─╣żĘżĶż”ż╚żżż”ź’źżźõźņź╣╩¼╠ŅżŪżóżļĪŻ╣Ō╝■āSövŽ®ż╬└▀╝ŖĪ╩×æēäć@Microwave OfficeĪ╦ż└ż▒żŪżŽż╩ż»ĪóźŪźĖź┐źļ╩č─┤źĘź╣źŲźÓż╩ż╔ż╬źĘź▀źÕźņĪ╝źĘźńź¾Ī╩Ų▒Visual System SimulatorĪ╦żõĪóź╬źżź║żõ┐«ęÄĮĶ═²ż╬┼┼╝¦─c▓“└ŽĪ╩Ų▒AXIEMĪ╦ĪóźĘźĻź│ź¾żõGaAs/GaNż╩ż╔▓Į╣ńر╚ŠŲ│öü└▀╝ŖĪ╩Ų▒Analog OfficeĪ╦ż╩ż╔ż╦╗╚ż”ź─Ī╝źļż“×æēä▓ĮżĘżŲżżżļĪŻ

Ų▒╝꿎Īóä▌╣±źĒźĄź¾źĖź¦źļź╣ż╦żóżļUCLAĪ╩University of California, Los AngelsĪ╦ż½żķź╣źįź¾ź¬źšżĘĪó1994ŃQż╦└▀╬®żĄżņĪó1998ŃQż╦║ŪĮķż╬×æēäż“źĻźĻĪ╝ź╣żĘż┐ż¼Īó2010ŃQ┼┘ż▐żŪ13┤³(ŃQ)Žó¶öīÜĖ¬æųż¼żĻż╬└«─╣ż“¶öż▒żŲżŁż┐ĪŻĪų╠żæųŠņż╬┤ļČ╚ż╩ż╬żŪ┐¶ÖCżŽĖ└ż©ż╩żżż¼Īó2008ŃQż┤żĒż½żķ▌üÖCż╦ż╩żĻĪóżĮż╬ĖÕżŽĮń─┤ż╦ŠW▒ūĪ”ŪõżĻæųż▓ż╚żŌż╦źūźķź╣└«─╣ĪŻ2011ŃQ┼┘żŽż╣ż┤ż»╬╔żżĪūĪ╩Ų▒╝ęź▐Ī╝ź▒źŲźŻź¾ź░├┤┼÷VPż╬Sherry HessĢ■Ī╦ż╚ĪóGlobalpress╝ń╠¢ż╬e-Summit2011żŪÅBżĘżŲżżż┐ż¼Īó4ĘŅż╦ż╩ż├żŲźūźņź╣źĻźĻĪ╝ź╣ż╦żŲ£½żķż½ż╦żĘż┐ż╚ż│żĒĪó2011ŃQ┼┘Ī╩3ĘŅ31Ų³ż“─∙żßż╚ż╣żļ▓±╝ŖŃQ┼┘Ī╦żŽ×┤ØiŃQ╚µ30%╗\ż╚żżż”±T▓╠ż└ż├ż┐ĪŻżżż║żņ│¶╝░æųŠņż“╣įż”ĪŻ

Ų▒╝ęż╬äėż▀żŽ╚┐╝ożõĻJŠ─ż╩ż╔Ąō╝║ż╬¾Hżż╣Ō╝■āS└▀╝Ŗż╦ż¬żżżŲĪóźµĪ╝źČĪ╝źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż╦źšź®Ī╝ź½ź╣żĘżŲżżżļż│ż╚ż└Ī╩┐▐2Ī╦ĪŻź▐źżź»źĒźĮźšź╚ż╬ź¬źšźŻź╣ż╚Ų▒══ż╩Ė½▒╔ż©Ī╩look and feelĪ╦ż“Ęeż─źĮźšź╚Microwave Officeż“╗╚ż├żŲźčźĮź│ź¾ź┘Ī╝ź╣żŪ└▀╝ŖżĘżõż╣żżż┐żßĪóUNIXź┘Ī╝ź╣ż╬ź│ź¾źįźÕĪ╝ź┐ż“╗╚ż├żŲ└▀╝Ŗż╣żļŠņ╣ńż╚╚µż┘źĮźšź╚ż“Ø{įuż╣żļ╗■┤ųż¼╚Š╩¼żĘż½ż½ż½żķż╩żżĪóż╚HessĢ■żŽĖ└ż”ĪŻMicrowave OfficeżŽĪóMMICĪ╩źŌź╬źĻźĘź├ź»ź▐źżź»źĒāSICĪ╦żõĪóźūźĻź¾ź╚övŽ®┤łĪóźŌźĖźÕĪ╝źļĪóSiPż╩ż╔ż╬ź▐źżź»źĒāSövŽ®ż“└▀╝Ŗż╣żļŠņ╣ńż╦╗╚ż”ĪŻ

┐▐2ĪĪMicrowave Officeż╬övŽ®└▀╝Ŗ▓ĶĀCĪĪź▐źżź»źĒźĮźšź╚ż╬ź¬źšźŻź╣ż╬żĶż”ż╩Ė½ż┐ų`

╚ŠŲ│öüźŪźąźżź╣ĪóØŖż╦RF CMOSżõBiCMOSĪóSOSĪóSi/Geźąźżź▌Ī╝źķż╩ż╔ż╬└▀╝Ŗż╦żŽAnalog Officeż“─¾ČĪżĘżŲżżżļĪŻźĘźĻź│ź¾żõGaAsż╩ż╔ż╬╚ŠŲ│öüż╬övŽ®└▀╝Ŗż╦ØŖ▓ĮżĘż┐ź─Ī╝źļżŪżóżĻĪó▓ĶĀCæųżŪ▓Š„[źŪźąźżź╣ż╚żĘżŲż╬└▀╝Ŗż¼żŪżŁżļĪŻ

Ų▒══ż╦Visual System SimulatorżŽĪóż│ż│ż╬ź▐źżź»źĒāSövŽ®żŪż╬övŽ®┐▐żõĮą╬üāSĘ┴żŪżŽż╩ż»Īóź’źżźõźņź╣źĘź╣źŲźÓż╚żĘżŲż╬Īó╬Ńż©żąźŪźĖź┐źļ╩č─┤ż╬16QAMż╬ėX▌åż“źĘź▀źÕźņĪ╝źĘźńź¾ż╣żļż╚ż½Īóź▐ź»źĒ┼¬ż╦Ė½żŲ▓┐ż¼ÅŚżŁżŲżżżļż½ż“ź┴ź¦ź├ź»ż╣żļż╬ż¼ų`┼¬ż└ĪŻAXIEMżŽźūźņĪ╝ź╩ź▐źżź»źĒź╣ź╚źĻź├źūźķźżź¾ż╬3╝ĪĖĄ┼┼╝¦─c▓“└Ž└▀╝Ŗź─Ī╝źļżŪżóżĻĪó▌ģ┤¼ėXż╬ź│źżźļżõźóź¾źŲź╩ż╬└▀╝Ŗżõ▓“└ŽĪóźūźĻź¾ź╚┤łż╬Ū█└■└▀╝Ŗż╩ż╔ż╦╗╚ż”ĪŻ

żŌż”▐kż─ż╬└«─╣╝┤żŽĪóź¬Ī╝źūź¾ż╩źŪźČźżź¾źšźĒĪ╝żŪżóżļĪŻAWRż╬źĘź▀źÕźņĪ╝ź┐żõ└▀╝ŖźŌźŪźļż“┴╚ż▀╣■żßżļżĶż”ż╦Įą═Ķżļż└ż▒║YØŹ┼¬ż╩ź─Ī╝źļż╚┴╚ż▀╣ńż’ż╗żķżņżļżĶż”ż╦║Ņż├żŲżżżļĪŻ╬Ńż©żąĪóźņźżźóź”ź╚żõövŽ®ź╣źŁź▐źŲźŻź├ź»Ų■╬üż╦żŽźßź¾ź┐Ī╝żõź▒źżźŪź¾ź╣ż╬ź─Ī╝źļĪóövŽ®źĘź▀źÕźņĪ╝ź┐żŽźĘź╬źūźĘź╣ż╬HSPICEĪóĖĪŠ┌ż╦żŌźßź¾ź┐Ī╝żõź▒źżźŪź¾ź╣ż╬ź─Ī╝źļĪóźĘź╣źŲźÓ└▀╝Ŗż╦żŽMATLABż╬źŌźŪźļż╦żŌ┴╚ż▀╣■żßżļĪŻ4ĘŅż╦żŽź╩źĘźńź╩źļźżź¾ź╣ź─źļźßź¾ź─ż╬ź┘ź»ź╚źļźĘź░ź╩źļźóź╩źķźżźČż“│½╚»ż╣żļż┐żßż╦Microwave Officeż╚Visual System Simulatorż“┴╚ż▀Ų■żņż┐Īóż╚╚»╔ĮżĘżŲżżżļĪŻ

Ų³╦▄żŽ─_═ūż╩▌xŠņż╚Ė½żŲż¬żĻĪó2002ŃQż╦ź¬źšźŻź╣ż“│½└▀żĘżŲ░╩═ĶĪóź░źĒĪ╝źąźļż╩ź│źķź▄źņĪ╝źĘźńź¾ż╦╬üż“Ų■żņżŲżżżļĪŻżĮż╬ĖÕ▄f╣±ż╬źĮź”źļĪó2011ŃQ4ĘŅż╦żŽ├µ╣±ż╬æųķLż╦żŌź¬źšźŻź╣ż“│½żżż┐ĪŻ7ĘŅż╦żŽźóźĖźóĪ╩źĮź”źļĪó±śĒ×Īó┼ņ»BĪ╦ż╦ż¬żżżŲźŪźČźżź¾źšź®Ī╝źķźÓż“│½╠¢ż╣żļ═Į─ĻżŪżóżļĪŻ

źóźčź├ź┴Īó─Ń┼┼╬ü└▀╝Ŗż½żķEMCĪóESDż╦żŌ│╚Įj

AWRż¼ź’źżźõźņź╣ÅUż╦ÅR╬üżĘż┐ż╬ż╦×┤żĘżŲĪóźóźčź├ź┴źŪźČźżź¾źĮźĻźÕĪ╝źĘźńź¾ź║Ī╩Apache Design SolutionsĪ╦╝꿎ĪóżŌż”▐kż─ż╬└«─╣ż╬╝┤żŪżóżļ─ŃŠ├õJ┼┼╬üICżžż╬▒■├ōż“┴└ż├ż┐EDAź─Ī╝źļź┘ź¾ź└Ī╝ż└ĪŻ2001ŃQż╦└▀╬®żĘż┐╣{żżź┘ź¾ź┴źŃĪ╝┤ļČ╚ż└ż¼Īóźčź’Ī╝▓“└Žż╚ź╬źżź║▓“└Žż╦ÅR╬üżĘżŲżżżļĪŻ└▀╬®ĖÕĪóż▐ż└źčź’Ī╝ż¼╠õ¼ö£åżĄżņż╩ż½ż├ż┐180nm╗■┬ÕżŽ∙ZŽ½żĘż╩ż¼żķżŌĪóźčź’Ī╝ż╦ÅR╬üżĘżŲżŁż┐±T▓╠Īó║ŪŖZż╬8ŃQ┤ųżŽŽó¶öżĘżŲźūźķź╣└«─╣żĘżŲżżżļĪŻ

Ų▒╝ęż╬┴Ž╬®Ūvż╬▐k┐═żŪCEOż╬Andrew YangĢ■Ī╩┐▐3Ī╦żŽĪóĪų130nmĪó90nm╗■┬Õż½żķźčź’Ī╝ż“╣═╬ĖżĘż╩ż½ż├ż┐ż┐żßż╦└▀╝Ŗź▀ź╣ż¼╗\ż©żŲżŁż┐Īūż╚Įęż┘żļĪŻ╗■┬ÕżŽźŪźĖź┐źļź┴ź├źūż└ż▒żŪżŽż╩ż»IPż╦ż─żżżŲżŌźčź’Ī╝ż¼╔į▓─’Lż╩└▀╝Ŗ═ū┴Ūż╦ż╩ż├żŲżŁż┐ĪŻŲ▒╗■ż╦─ŃŠ├õJ┼┼╬üż└ż▒żŪżŽż╩ż»Īó║ŪĮķż╬źĘźĻź│ź¾ż¼└▀╝Ŗ─╠żĻż╦Ų░ż»ż½ż╔ż”ż½ż╦ż─żżżŲżŽź╬źżź║żõĻJŠ─┬č└ŁĪóESDĪ╩¼ś┼┼Ū╦ŽsĪ╦ż╦żŌźčź’Ī╝żĮż╬żŌż╬ż¼▒Ųūxż“Ą┌ż▄ż╣żĶż”ż╦ż╩ż├żŲżŁż┐ż╚żżż”ĪŻżĮżņżŌźĘźĻź│ź¾ź┴ź├źūż└ż▒żŪżŽż╩ż»Īóźčź├ź▒Ī╝źĖżõź▄Ī╝ź╔źņź┘źļż▐żŪ╣═╬Ėż╦Ų■żņżļØŁ═ūż¼ĮążŲżŁżŲżżżļĪŻ

┐▐3ĪĪApache╝ęCEOż╬Andrew YangĢ■

║ŪŖZżŪżŽĪóTSVż“╗╚ż├ż┐3D ICż╩ż╔ż╬┼┼╬ü▓“└Žż╬═ūĄßżŌĮążŲżŁżŲż¬żĻĪóŠ├õJ┼┼╬üż╚ÕX▓“└Žż╬└▀╝ŖŠ}╦Īż¼ĄßżßżķżņżļżĶż”ż╦ż╩ż├żŲżŁżŲżżżļĪŻżĮż│żŪźóźčź├ź┴żŽźčź’Ī╝ż╚ź╬źżź║ż╬╠õ¼öż“▓“ż»ż┐żßĪó4ż─ż╬×æēäźūźķź├ź╚źšź®Ī╝źÓż“ŠW├ōżĘżŲ╝Īż╬3ż─ż╬źĮźĻźÕĪ╝źĘźńź¾ż“Ė└Ą┌żĘżŲżżżļĪŻ

1. źčź’Ī╝źąźĖź¦ź├ź╚Ī¦źĘź╣źŲźÓż╬éb═²└▀╝Ŗźņź┘źļż½żķŠ├õJ┼┼╬üż“žōżķż╣ż┐żßż╬▓“└Žż╚║Ū┼¼▓Įż“╣įż”

2. źčź’Ī╝źŪźĻźąźĻĪ╝źżź¾źŲź░źĻźŲźŻĪ¦Ū█┼┼ż¼┴T┐▐ż╔ż¬żĻż╦╣įż’żņżŲżżżļż½ż“ź┴ź¦ź├ź»żĘĪóSoCż╬┼┼Ė╗ź╬źżź║ż“▓“└ŽżĘ└▀╝Ŗ┤░╬╗ż▐żŪźĄź▌Ī╝ź╚ż╣żļ

3. źčź’Ī╝źżź¾źŪźÕĪ╝ź╣ź╚ź╬źżź║Ī¦ź┴ź├źūż“źčź├ź▒Ī╝źĖź¾ź░żĘź▄Ī╝ź╔ż╦╝┬äóżĘż┐ĖÕĪóź┴ź├źūż╦ČĪĄļż╣żļ┼┼╬üż¼╩³╝ożĄżņ╠ßż├żŲż»żļż│ż╚żŪÖ┌żĖżļź╬źżź║ż“źŌźŪźļ▓ĮżĘ▓“└Žż╣żļ

3D ICż╚żĘżŲź┴ź├źūż╚ź┴ź├źūż“TSVżŪ└▄¶öżĘż┐╗■ż╬Š├õJ┼┼╬üż└ż▒żŪżŽż╩ż»ĪóÕX╩¼╔█żõź╣ź╚źņź╣ĪóżĮżņżķż╬╗■┤ų╩č▓ĮżŌ▓“└Žż╣żļĪŻżĄżķż╦źßź┐źļŪ█└■ŲŌż╦ż¬ż▒żļ┼┼░ĄæT▓╝(ź©źņź»ź╚źĒź▐źżź░źņĪ╝źĘźńź¾╔į╬╔×┤║÷)ż╦ż─żżżŲż╬ź▐ź├źūżŌ╔Į┐āż╣żļĪ╩┐▐4Ī╦ĪŻ

┐▐4ĪĪ3D ICż╬┼┼░ĄæT▓╝╩¼╔█ż╚ÕX╩¼╔█źĘź▀źÕźņĪ╝źĘźńź¾ĪĪĮąųZĪ¦Apache Design Solutions

║“ŃQźĻźĻĪ╝ź╣żĘż┐PathfinderźĮźĻźÕĪ╝źĘźńź¾żŽĪóESD╠õ¼öż“ź┴ź├źūĪóźčź├ź▒Ī╝źĖż½żķ┤łż╬RCż“├ĻĮążĘż┐żĻĪó┼┼╬«╠®┼┘ż╬ź┴ź¦ź├ź»żõI/Oż╬āį┼Ž▒■┼·ż“źĘź▀źÕźņĪ╝źĘźńź¾żĘż┐żĻżŪżŁżļżĶż”ż╦ż╩ż├żŲżżżļĪŻ┐═öüźŌźŪźļżõźŪźąźżź╣┬ė┼┼źŌźŪźļż╩ż╔żŌźĄź▌Ī╝ź╚żĘżŲżżżļĪŻESDżŽĘQ╝ęĘQ══żŪ▓“»éżĘżŲżŁż┐ż¼Īóźóźčź├ź┴żŽż│żņż“ICż╬ŖWµ£Ų░║Ņōļ░Ķżõ┐«═Ļ└Łæųż╬öU╠¾ĪóÕXż╦żĶżļĖ╬ŠŃ▓“└Žż╩ż╔ż“╣═╬Ėż╦Ų■żņĪóŖWµ£ż╩ESD╩▌ĖŅżŪżŁżļōļ░Ķż“│╬╩▌ż╣żļżĶż”ż╩Š}╦Īż“│½╚»żĘżŲżżżļĪŻ

źóźčź├ź┴żŽż│ż╬ż█ż╔│¶╝░æųŠņż“╣įż”ż┐żßĪóSECĪ╩Š┌─wŲD░·░čµ^▓±Ī╦ż╦ŲŽż▒ż“┐ĮæążĘż┐ĪŻIPOż╦Ė■ż▒ż┐ŲŌ═Ųż╦ż─żżżŲżŽŠ▄║┘ż“Įo╔ĮżĘżŲżżż╩żżż¼Īó┐ĮæąŠ}¶öżŁżŽź╔źżź─Čõ╣įŠ┌─wż¼╣įż”ż│ż╚ż╦ż╩ż├żŲżżżļĪŻ│¶╝░Įo│½ż╦żĶżļźŁźŃźįź┐źļź▓źżź¾żŪ½@ČŌż“─┤├ŻżĘĪ󿥿ķż╩żļ└«─╣ż“┴└ż”ĪŻ