źķźįź└ź╣ĪóEsperantoż╚ż╬─¾Ę╚żŪĪóTSMCż╚ż╬░Ńżżż¼£½│╬ż╦

źķźįź└ź╣ż¼RISC-Vż╬ź╣ź┐Ī╝ź╚źóź├źūEsperanto Technologiesż╚Ė“ż’żĘż┐─¾Ę╚żŽĪó╝┬żŽż│ż│żŪĮķżßżŲTSMCż╚ż╬░Ńżżż¼£½│╬ż╦ĮążŲżżż┐ĪŻEsperantoż╬▓±Ė½żŪżŽÜW║═CPUźŪźČźżź╩Ī╝ż╚żŌĖ└ż’żņżļDave Ditzel CTOĪ╩┐▐1Ī╦żŌŲ▒└╩żĘżŲżżż┐ż╬ż└ĪŻ╚ÓżŽż½ż─żŲźĮźšź╚ź”ź©źóż╦żĶżļ╣®╔ūżŪX86Ė▀┤╣źūźĒź╗ź├źĄż“└▀╝ŖżĘĪó║ŻżŽRISC-Vż╬└▀╝Ŗż“╬©żżżļĪŻ╚Óż¼TSMCż╚ż╬░Ńżżż“£½│╬ż╦żĘż┐ĪŻ

┐▐1ĪĪEsperanto TechnologiesĪĪCTOż╬Dave DitzelĢ■

ż│żņż▐żŪż╬źķźįź└ź╣ż╬└Ō£½żŪżŽĪó├▒ż╦TSMCż╚Ų▒══ż╬└Ķ├╝źšźĪź”ź¾ź╔źĻż“╣įżż▓±╝ęĪóż╚żżż”┬¬ż©öĄ(sh©┤)żŪżĘż½ż╩ż½ż├ż┐ĪŻ2nmźūźĒź╗ź╣ż“╣įż”źšźĪź”ź¾ź╔źĻż╬┬ō(li©ón)┘I╗Ķż¼TSMCż╬┬ŠĪóSamsungĪóIntelż╬╝Īż╦źķźįź└ź╣ż¼żóż├ż┐ĪŻż╣żŪż╦źķźįź└ź╣ż¼─¾Ę╚żĘżŲżżż┐Tenstorrentż╬CEOżŪżóżļJim KellerĢ■ż╚ż╬źżź¾ź┐źėźÕĪ╝ĄŁĄ£Ī╩╗▓╣═½@╬┴1Ī╦żŪżŽĪóż▐ż║GlobalFoundriesĪó╝Īż╦TSMCĪóSamsungĪóżĮż╬└Ķż╦źķźįź└ź╣żŪÖ┌ŠÅż╣żļż╚Įęż┘żŲż¬żĻĪóŲ▒š`ż╬źšźĪź”ź¾ź╔źĻż╚żżż”┬¬ż©öĄ(sh©┤)ż“żĘżŲżżżļĪŻ

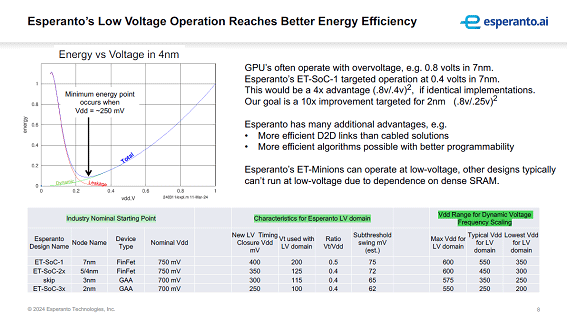

║ŻövĪóEsperanto ż╬┴ŽČ╚ŪvżŪżóżĻCTOżŪżŌżóżļDave DitzelĢ■ż¼źķźįź└ź╣ż“┬ō(li©ón)ż¾ż└ż╬żŽĪóEsperantoż¼╝┬ĖĮżĘż┐żżČ╦─Ń┼┼░Ąż╬ELVĪ╩Extreme Low VoltageĪ╦Č\Įčż“Č”Ų▒│½╚»żĘżŲż»żņżļż½żķż└ż╚żżż”ĪŻEsperantożŽżŌż╚żŌż╚éb═²└▀╝Ŗż½żķéb═²╣ń└«Ī”ź═ź├ź╚źĻź╣ź╚║Ņ└«ĪóŪ█ÅøŪ█└■ż╬ر═²└▀╝ŖĪóź▐ź╣ź»Įą╬üż▐żŪŠ}²Xż▒żļLSI└▀╝Ŗµ£żŲż“żŪżŁżļ▓±╝ężŪżóżļĪŻż─ż▐żĻź▐ź╣ź»Įą╬üż▐żŪż╬LSI└▀╝Ŗż╬µ£żŲż“├┤ż├żŲż»żņżļ┤ļČ╚żŪżóżĻĪóźķźįź└ź╣ŖõżŽźūźĒź╗ź╣ż╦ż└ż▒└ņŪ░żĘĪó▐kĮ’ż╦─Ń┼┼░ĄĪóż╣ż╩ż’ż┴ź▓Ī╝ź╚żĘżŁżż┼┼░ĄVthż“▓╝ż▓żļż┐żßż╬źūźĒź╗ź╣Č\Įčż“│½╚»żĘżŲż»żņżļż╚DitzelĢ■żŽĖ└ż”ĪŻDitzelĢ■ż╬╣═ż©żļELVČ\Į迎źūźĒź╗ź╣Č\Įčż╚ż╬źżź┐źņĪ╝źĘźńź¾ż“Ę½żĻ╩ųżĘż╩ż¼żķ─ŃżżVthż“╝┬ĖĮż╣żļĪŻż│żņżŽTransmeta╗■┬Õż╦ŲDżĻ┴╚ż¾żŪżŁż┐Č\ĮčĪ╩┐▐2Ī╦ż└ż╚żżż”ĪŻż╣ż╩ż’ż┴─ŃVthż╬MOSź╚źķź¾źĖź╣ź┐ż“źķźįź└ź╣żŽ▐kĮ’ż╦│½╚»żĘżŲż»żņżļż½żķĪóEsperantożŽźķźįź└ź╣ż“┬ō(li©ón)ż¾ż└ĪŻ

┐▐2ĪĪź▓Ī╝ź╚żĘżŁżż┼┼░ĄVthż“▓╝ż▓żļźĻĪ╝ź»┼┼╬«ż╚ż╬║Ū┼¼┼┼░ĄżŽ0.25VĪĪĮąųZĪ¦Esperanto TechnologiesĪóCool Chips 27 Invited Talk

TSMCżõSamsungż╩ż╔ż╬źšźĪź”ź¾ź╔źĻżŽĪóPDKĪ╩źūźĒź╗ź╣└▀╝ŖźŁź├ź╚Ī╦ż╚Ō}żążņżļśOżķż╬źūźĒź╗ź╣ż╦╣ńż├ż┐Vthż╬MOSź╚źķź¾źĖź╣ź┐ż“║ŅżļźūźĒź╗ź╣żĘż½Ė▄Ąęż╦─¾ČĪżĘż╩żżĪŻż│żņż╦×┤żĘżŲźķźįź└ź╣żŽĖ▄Ąę╗┼══ż╦╣ńż’ż╗żŲż»żņżļĪóż╚żżż”Ślż└ĪŻż│żņż¼║ŪżŌĮjżŁż╩░Ńżżż╦ż╩żļĪŻżĘż½żŌĪóEsperantożŽĪó└▀╝Ŗ╣®µćż╬µ£żŲż“├┤┼÷ż╣żļĪŻ

żĘż½żĘĪóźšźĪź”ź¾ź╔źĻźėźĖź═ź╣żŪżŽLSI└▀╝Ŗż╦µ£ż»ČĮ╠Żż“┐āżĄż╩żżĖ▄ĄężŌĮążŲż»żļĪŻż╗żżż╝żżéb═²└▀╝ŖżŪRTLĪ╩Register Transfer LevelĪ╦Įą╬üż▐żŪ└▀╝ŖżĘżŲż»żņżļĖ▄ĄężŽ¾Hżżż¼Īóر═²└▀╝Ŗż▐żŪ├┤ż”Ė▄ĄężŽż█ż╚ż¾ż╔żżż╩żżĪŻRTLĮą╬üż½żķź▐ź╣ź»Įą╬üż▐żŪż╬LSI└▀╝ŖżŽ├»ż¼├┤┼÷ż╣żļż╬ż½ĪŻźŪźČźżź¾źŽź”ź╣ż¼żĮż╬╠“│õż“├┤ż”ĪŻTSMCżŽŲ³╦▄ż╬DNPĪ╩ĮjŲ³╦▄░§║■Ī╦żõToppanż╩ż╔ż╬LSI└▀╝Ŗż“╣įż├żŲź▐ź╣ź»Įą╬üGDS-IIźšź®Ī╝ź▐ź├ź╚ż▐żŪ└▀╝ŖżĘżŲż»żņżļźŪźČźżź¾źŽź”ź╣ż“źčĪ╝ź╚ź╩Ī╝ż╚żĘżŲĘeż├żŲżżżļĪŻźķźįź└ź╣ż╬Ė▄Ąęż¼żŌż├ż╚╗\ż©żļż╚ĪóLSI└▀╝Ŗż╬┴Ū┐═ż╬Ė▄ĄężŌĮążŲż»żļĪŻ

ż│ż╬Šņ╣ńż“ż╔ż”ż╣żļż╬ż½ĪŻźķźįź└ź╣ż╬Š«├ėĮ▀▒I┬Õ╔ĮŲD─∙╠“╝ę─╣żŽĪóż│żņż½żķźŪźČźżź¾źŽź”ź╣żŌźčĪ╝ź╚ź╩Ī╝ż╚żĘżŲ┴╚“E▓ĮżĘżŲżżż»ż│ż╚ż“╣═ż©żŲżżżļĪóż╚Įęż┘ż┐ĪŻ

ź╣ź┐Ī╝ź╚źóź├źūż╬EsperantożŽĪó┴ŽČ╚żĘżŲ9ŃQĘąż┴Īó║“ŃQżĶż”żõż»×æēäż“╚»╔ĮżĘż┐ĪŻ╚Óżķż╬×æēäż╬┴└żżżŽAIźĄĪ╝źąĪ╝ż“┤▐żÓźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ĪŻĖĮ║▀╝ń╬«ż╬Nvidiaż╬GPUż╬źóźūźĒĪ╝ź┴żŪżŽżŌżŽżõŠ├õJ┼┼╬üżŪĖ┬─cż╦═ĶżŲżżżļĪŻ║Ū┐Ęż╬Blackwellź╣Ī╝źčĪ╝ź┴ź├źūż╬Š├õJ┼┼╬üżŽ2700Wż╣ż╩ż’ż┴2.7kWżŌżóżļż╚żżż”ĪŻż│żņżŪżŽźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╬└Łē”żŽæųż¼ż├żŲżŌ╚»┼┼ĮĻż“┐Ęż┐ż╦└▀ż▒żļØŁ═ūż¼ĮążŲż»żļĪŻż│żņżŽżŌżŽżõß×═ŲżŪżŁż╩żżĪŻź│ź¾źįźÕĪ╝źŲźŻź¾ź░ź┴ź├źūż“─Ń┼┼░Ą▓Įż╣żļż│ż╚żŽź▐ź╣ź╚ż╦ż╩ż├żŲż»żļĪŻ

żĘż½żŌ└Łē”ż“æųż▓żļż┐żßż╦żŽ╣ŌĮĖ└č▓ĮżŽØŁ┐▄ż└ż¼ĪóżŌżŽżõź┴ź├źūźĄźżź║żŌĮjżŁż»żŪżŁż╩żżĪŻźņź┴ź»źļźĄźżź║żŪ»éż▐żļż½żķż└ĪŻżĘż½żŌ╩Ōé╬ż▐żĻżŽ┤ų░Ńżżż╩ż»═Ņż┴żŲżżż»ĪŻżĮż│żŪź┴ź├źūźņź├ź╚ż╬┼ąŠņż╚ż╩żļĪŻź┴ź├źūźņź├ź╚ż“3╝ĪĖĄ▓Įżõźżź¾ź┐Ī╝ź▌Ī╝źČæųż╦╝┬äóż╣żļż│ż╚żŪ╣ŌĮĖ└č▓Įż“├Ż└«żŪżŁżļĪŻ

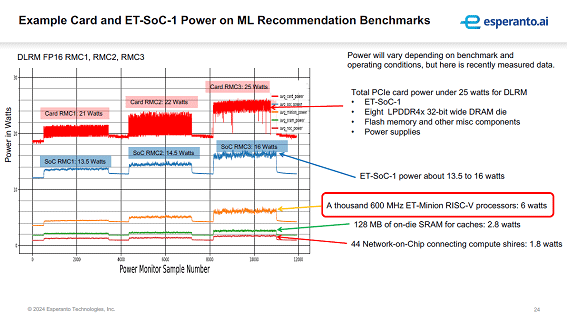

║“ŃQ×æēä▓ĮżĘż┐Esperanto ż╬LSIĪ╩×æēäć@ĪųET-SoC-1ĪūĪ╦ż╬źóĪ╝źŁźŲź»ź┴źŃżŪżŽĪó╝ńż╦2¹|╬Óż╬64źėź├ź╚RISC-CPUź│źóĪ╩ET-Minionż╚ET-MaxionĪ╦ż“├ōżżżļĪŻET-MinionżŽ1000Ė─żŌż╬ź│źóż“╩┬š`Ų░║ŅżŪŲ░ż½żĘĪóET-MaxionżŽ4ż─ż╬ź│źóżŪźóź”ź╚ź¬źųź¬Ī╝ź└Ī╝╠┐╬ßż“╝┬╣įż╣żļźūźĒź╗ź├źĄż└ĪŻżĄżķż╦öUĖµ├ōż╬64źėź├ź╚RISC-źĄĪ╝źėź╣ź│źóż“Ęeż─ĪŻ╠┐╬ß─╣512źėź├ź╚ż“Ęeż─VLIWöĄ(sh©┤)╝░ż“ż╚żļżĶż”ż└ĪŻTSMCż╬7nmźūźĒź╗ź╣żŪ×æļ]żĘż┐ż│ż╬ET-SoC-1ź┴ź├źūżŽ240▓»ź╚źķź¾źĖź╣ź┐ż“ĮĖ└čżĘĪóź└źżĀC└迎570mm2ż╚ĮjżŁżżĪŻŠ├õJ┼┼╬üżŽ15Wż½żķ60Wż▐żŪ─┤┼D▓─ē”ż└ż╚żĘżŲżżżļĪŻ╝┬▒RźŪĪ╝ź┐żŌĮo│½żĘżŲżżżļĪ╩┐▐3Ī╦ĪŻźķźįź└ź╣ż╚ż╬Č©Č╚żŽĪó2nmźūźĒź╗ź╣ż“ŠW├ōż╣żļŗī3└ż┬Õż╬ET-SoCż╚ż╩żļĪŻ

┐▐3ĪĪ║ŪĮķż╬×æēäET-SoC-1ż╬╝┬▒RźŪĪ╝ź┐Īóź½Ī╝ź╔ż╦╝┬äóżĘżŲżŌŠ├õJ┼┼╬üżŽ25WĪĪĮąųZĪ¦Esperanto Technologies

DitzelĢ■żŽĪóź½źĻźšź®źļź╦źóĮj│žźąĪ╝ź»źņźżē“żŪDavid PattersonČĄĶbżķż╚Č”ż╦RISC-VźóĪ╝źŁźŲź»ź┴źŃż“│½╚»żĘż┐Ęą┘xż“Ęeż─ĪŻEsperantoż“┴ŽČ╚ż╣żļØiżŽĪóTransmeta╝ężŪĪóVLIWĪ╩Very Long Instruction WordĪ╦╠┐╬ßżŪ╣Į└«żĄżņĪóź│Ī╝ź╔źŌĪ╝źšźŻź¾ź░Ī╩Code MorphingĪ╦ż╚Ō}żųźĮźšź╚ź”ź©źóż“╗╚ż├żŲX86Ė▀┤╣CPUż“└▀╝ŖżĘż┐ĪŻ1995ŃQ┴ŽČ╚ż╬┤ļČ╚żŪĪó2000ŃQż┤żĒż╦╚»╔ĮżĘż┐Crusouź┴ź├źūżŽŲ³╦▄żŪżŌżŲżŽżõżĄżņż┐ĪŻ

DitzelĢ■żŽŠ├õJ┼┼╬üż╬Š»ż╩żżVLIWźóĪ╝źŁźŲź»ź┴źŃż╬ź┴ź├źū│½╚»Īó╣Ō└Łē”Ī”─ŃŠ├õJ┼┼╬üż“╝┬ĖĮżŪżŁżļRISC-Vź┴ź├źū│½╚»ż“─╠żĘżŲĪó─ŃŠ├õJ┼┼╬üż╬AIź┴ź├źūż“ų`╗žż╣ĪŻź▌ź╣ź╚GPU╗■┬Õż╦Ė■ż▒ĪóźŪĪ╝ź┐źšźĒĪ╝ź│ź¾źįźÕĪ╝źŲźŻź¾ź░żõVLIWźóĪ╝źŁźŲź»ź┴źŃż╩ż╔┐ʿʿżź│ź¾źįźÕĪ╝źŲźŻź¾ź░╗■┬Õż¼żõż├żŲż»żļĪóż╚Ų▒Ģ■żŽ┤³┬įż╣żļĪŻ

╗▓╣═½@╬┴

1. Äh╦▄żĻż”ż│ĪóÄóĪž┼┴└Ōż╬ź©ź¾źĖź╦źóĪ┘ż¼£½ż½ż╣ź©ź╠źėźŪźŻźóż╬Ęx│čÄŻĪó┼ņ═╬Ęą║蟬ź¾źķźżź¾Īó(2024/03/04)