┐ʿʿżźßźŌźĻźĘź╣źŲźÓż¼źŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż“╩č│ūż╣żļĪ┴GSA Memory+▓±Ą─ż½żķ

źßźŌźĻż¼ż│żņż½żķż╬źĘź╣źŲźÓż╬├µ┐┤ż╦ż╩żļĪŻż│ż”żżż├ż┐Ų░żŁż¼GSA Memory+ ConferenceżŪ┼ąŠņżĘż┐ĪŻż│żņż½żķż╬źßźŌźĻż“├ĄżļæųżŪźßźŌźĻź╗źļ├▒öüż½żķĪóźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╬żĶż”ż╩źĘź╣źŲźÓźņź┘źļżŪż╬źßźŌźĻż╬╣ŌÅ]▓ĮĪóĮj═Ų╬╠▓Įż╦ż─ż╩ż¼żļCXLĪ╩Compute Express LinkĪ╦źżź¾ź┐Ī╝ź│ź═ź»ź╚Īó3D-NANDż╦╗╔Ś„żĄżņż┐3D-NORżžż╬╠Oż╩ż╔Īó┐ʿʿżźßźŌźĻż╬Ų░żŁż¼£½żķż½ż╦ż╩żĻż─ż─żóżļĪŻ

┐▐1ĪĪGSA Memory+ Conferenceż╬╦┴Ų¼żŪGSAż╬╠“│õż╦ż─żżżŲĮęż┘żļCEOż╬Jodi SheltonĢ■ĪĪĮąųZĪ¦GSA Memory+ Conferenceż½żķź╣ź»źĻĪ╝ź¾źĘźńź├ź╚

źßźŌźĻż¼┐ʿʿżźšź¦Ī╝ź║ż╦Ų■ż├ż┐ż╚Įęż┘ż┐ż╬żŽĪó▄f╣±SK Hynixż╬CEOĘ¾╝ę─╣ż╬Seok-Hee LeeĢ■ĪŻźŪźĖź┐źļź╚źķź¾ź╣źšź®Ī╝źßĪ╝źĘźńź¾Ī╩DXĪ╦╗■┬Õż╬źßźŌźĻźßĪ╝ź½Ī╝żŽż▐ż╣ż▐ż╣─_═ūż╩╠“│õż“├┤ż”ż╚żĘżŲĪóż│żņż▐żŪż╬╣ŌĮĖ└čĪ”╣ŌÅ]Ī”─ŃŠ├õJ┼┼╬üż╚żżż├ż┐öĄĖ■ż½żķĪó║Żżõ╝ę▓±╠õ¼öż╬▓“»éż╦źßźŌźĻż¼─_═ūż╦ż╩ż├żŲżżżļż╚ĖņżļĪŻżĮż│żŪ3SĪ╩ScalingĪóSocialĪóSmartĪ╦ż╚żżż”Ė└±äżŪĖĮ║▀ż│żņż½żķż╬öĄĖ■ż“╔ĮĖĮżĘż┐ĪŻScalingżŽ“£═Ķż╬ūā─╣ż╬╣ŌĮĖ└čżõ╣ŌÅ]▓Įż╬┐╩▓ĮżŪżóżĻĪóSocialżŽżĮżņż“żĄżķż╦┐╩żßż┐Š╩ź©ź═żõ▓┴├═ż╬Ė■æųż╚żżż├ż┐╝▄┼┘ż“╔Įż╣ĪŻżĮżĘżŲSmartż│żĮż¼DXĖ■ż▒ż╬┐ʿʿżźßźŌźĻČ\Įčż╦ż╩żļż╚żĘżŲĪóźĒźĖź├ź»żŌ┤▐żßżŲźĘź╣źŲźÓż“Ė½─Šż╣╗■┤³ż╦═Ķż┐ż╚ż╣żļĪŻ

ØŖż╦Īóż│żņż▐żŪż╬CPU├µ┐┤ż╬źóĪ╝źŁźŲź»ź┴źŃż½żķźßźŌźĻ├µ┐┤ż╬źóĪ╝źŁźŲź»ź┴źŃżžż╬╬«żņż¼▓├Å]ż╣żļż╚żżż”Ī╩┐▐2Ī╦ĪŻżĄż▐żČż▐ż╩źĘź╣źŲźÓż¼ź╣ź▐Ī╝ź╚ż╦ż╩żĻĪóµ£żŲż╬źŪźąźżź╣ż¼AIż╚żŌ─╠┐«żŪż─ż╩ż¼ż├żŲżżż»ż¼ĪóżĮż”żżż├ż┐źĘź╣źŲźÓż╬63%ż¼źßźŌźĻż╦ż╩żļż╚Įęż┘ż┐ĪŻźßźŌźĻ├µ┐┤ż╬źóĪ╝źŁźŲź»ź┴źŃżŪżŽĪóCPUż╚ż█ż▄▐köü▓Įż╣żļżĶż”ż╩źßźŌźĻ╣Įļ]ż╦ż╩żļż╚żżż”ĪŻ

┐▐2ĪĪCPU├µ┐┤ż½żķźßźŌźĻ├µ┐┤żžĪĪĮąųZĪ¦GSA Memory+ Conferenceż½żķż╬ź╣ź»źĻĪ╝ź¾źĘźńź├ź╚

ź╣ź╚źņĪ╝źĖż╦┤žżĘżŲżŌĪóNANDźšźķź├źĘźÕż“╗╚ż├ż┐SSDĪ╩╚ŠŲ│öüźŪźŻź╣ź»Ī╦ż¼HDDĪ╩źŽĪ╝ź╔źŪźŻź╣ź»äóÅøĪ╦ż“ÅøżŁ┤╣ż©ż¼┐╩ż¾żŪżżżļż¼Īó─ŃŠ├õJ┼┼╬üż╬PLCĪ╩5źėź├ź╚/ź╗źļĪ╦/QLCĪ╩4źėź├ź╚/ź╗źļĪ╦ż╬SSDż“HDDż╦ÅøżŁ┤╣ż©żļż╚Š├õJ┼┼╬üżŽ93%▓╝ż¼żļż╚LeeĢ■żŽĮęż┘ż┐ĪŻżŌżĘ2030ŃQż▐żŪż╦HDDż“µ£żŲSSDż╦ÅøżŁ┤╣ż©żļż╚4100╦³ź╚ź¾ż╬CO2║’žōż╦ż╩żļż╚Ė½└čżŌż├żŲżżżļĪŻ

CXLż¼źŪĪ╝ź┐ź╗ź¾ź┐Ī╝╣Įļ]ż“╩č│ūż╣żļ

Micron Technologyż╬Č\Įč│½╚»├┤┼÷ż╬źĘź╦źóVPż╬Naga ChandrasekaranĢ■żŌżõżŽżĻĪóźßźŌźĻż¼ź½ź╣ź┐ź▐ź©ź»ź╣ź┌źĻź©ź¾ź╣ż“╩čż©żŲżżż»ż╚Įęż┘Īó“£═Ķż╬CPU├µ┐┤ż╬źóĪ╝źŁźŲź»ź┴źŃż╬ź▄ź╚źļź═ź├ź»ż“▓“Š├ż╣żļż╬ż¼DRAMż╚SCMż╬┤ųż╦═ĶżļCXLĪ╩Compute Express LinkĪ╦źżź¾ź┐Ī╝ź│ź═ź»ź╚żŪż─ż╩ż¼żļźßźŌźĻż└ż╚Ėņż├ż┐Ī╩┐▐3Ī╦ĪŻĖĄĪ╣CXLźżź¾ź┐Ī╝ź│ź═ź»ź╚æä│╩żŽMicronż¼┐õ┐╩żĘżŲżŁż┐ź¬Ī╝źūź¾ź╣ź┐ź¾ź└Ī╝ź╔żŪżóżļż¼ĪóCXLż╦żŽźßźŌźĻźßĪ╝ź½Ī╝µ£żŲż¼ÅRų`żĘżŲżżżļĪŻØŖż╦Īó£½Ų³ż╬źŪĪ╝ź┐ź╗ź¾ź┐Ī╝ż╬╣Į└«ż“╩čż©żŲżżż»ż╚Ė½╣■ż▐żņżŲżżżļĪŻ

CXLżŽĪóPCIeźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“ź┘Ī╝ź╣ż╦żĘż┐┐ʿʿżźżź¾ź┐Ī╝ź│ź═ź»ź╚Č\ĮčżŪĪóźßźŌźĻż“Įj╬╠ż╦└▄¶öżŪżŁżļ╣Į└«ż¼ØŖ─╣żŪĪóźżź¾ź┐Ī╝ź│ź═ź»ź╚ż╬ź╣źżź├ź┴ż╬╠“│õż“▓╠ż┐ż╣ĪŻ“£═Ķż╬źąź╣╣Į└«ż└ż╚Īóźąź╣Ēö╣ńż¼ÅŚżŁżõż╣żżż┐żßĄčż├żŲźóź»ź╗ź╣Å]┼┘ż¼ęÆżņżŲżĘż▐ż”ĪŻżĮżņż“ķcż▒żļż┐żßĪóź╣źżź├ź┴ź¾ź░żŪ─┤┼Dż╣żļż╚żżż”Ślż└ĪŻCPUżõGPUź│źóż“Įj╬╠ż╦└▄¶öż╣żļŠņ╣ńżŌźżź¾ź┐Ī╝ź│ź═ź»ź╚ż╦ź╣źżź├ź┴ź¾ź░Č\Įčż“┼¼├ōżĘżŲĪóØŖż╦ź╣Ī╝źčĪ╝ź│ź¾źįźÕĪ╝ź┐żõHPCĪ╩High Performance ComputingĪ╦ż╩ż╔żŪĮj╬╠ż╬CPUżõGPUż“└▄¶öżŪżŁżļżĶż”ż╦żĘżŲżżżļĪŻSmartNICżõ╔┘▀tż╬Tofuźżź¾ź┐Ī╝ź│ź═ź»ź╚ż╩ż╔ż╬ź╣źżź├ź┴źšźĪźųźĻź├ź»ż╬żĶż”ż╦ĪóĮj╬╠ż╬źßźŌźĻż¼╗╚ż©żļżĶż”ż╦żĘżĶż”ż╚żżż”æä│╩żŪżóżļĪŻ

6ĘŅ30Ų³ĪóMicron TechnologyżŽĪ󟵟┐䔟ĻĪ╝źŽźżż╦żóżļźßźŌźĻ╣®Šņż“15▓»ź╔źļżŪTexas Instrumentsż╦ŪõĄčż╣żļż╚╚»╔ĮżĘż┐ĪŻżĮż│żŪżŽ3D-XpointźßźŌźĻż“Ö┌ŠÅżĘżŲżżż┐ĪŻż─ż▐żĻ3D-XpointźßźŌźĻżŌÖ┌ŠÅż“┘Vżßżļż╚żżż”ż│ż╚żŪżóżļĪŻżĮż╬┐┐┴TżŽĪóż╔ż”żõżķCXLźżź¾ź┐Ī╝ź│ź═ź»ź╚ż╦żóżĻżĮż”ż└ĪŻ3D-XpointźßźŌźĻż╬▌xŠņż¼┼÷╩¼Ė½╣■żßż╩żżż¼ĪóCXLźżź¾ź┐Ī╝ź│ź═ź»ź╚æä│╩żŪĮj╬╠ż╬źßźŌźĻż“└▄¶öż╣żļż│ż╚żŪźĘź╣źŲźÓ└Łē”ż╬▓■║¤ż¼Ė½╣■żßżļĪŻ

3D-NORźšźķź├źĘźÕżŌCXLźßźŌźĻż╬Ńt▌öż╦

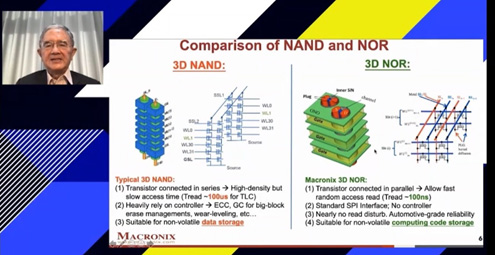

±śŽčż╬NORźšźķź├źĘźÕż“┐õ┐╩ż╣żļMacronix Internationalż╬ź┴Ī╝źšźĄźżź©ź¾źŲźŻź╣ź╚ż╬KC WangĢ■żŽĪóCXLżŽźšźķź├źĘźÕźßźŌźĻż╦Ė■ż»ż╚Įęż┘ż┐ĪŻźßźŌźĻż“Įj╬╠ż╦╗╚ż”CXLżŪżŽźßźŌźĻ├µ┐┤ż╬ź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╬▐kż─ż╚żĘżŲ░╠Åøż┼ż▒żķżņĪóNANDźšźķź├źĘźÕżĶżĻżŌ╣ŌÅ]ż╩NORźšźķź├źĘźÕż╦żŌ╠Oż¼│½ż½żņżŲżżżļĪŻżĮżņż¼3D-NORżŪżóżļĪŻ

“£═Ķż╬NORźšźķź├źĘźÕźßźŌźĻżŽ╚∙║┘▓Įż╦Ė┬─cż¼żóżĻĪó40nm░╩▓╝ż¼žMżĘż»╣ŌĮĖ└č▓ĮżŌżŪżŁż╩ż½ż├ż┐ĪŻż╚ż│żĒż¼Īó3D-NANDČ\Įčż“NORż╦┼¼├ōż╣żņżąGźėź├ź╚ź»źķź╣żŌ▓─ē”ż└ż╚żĘżŲżżżļĪ╩┐▐3Ī╦ĪŻ

┐▐3ĪĪ3D-NORźšźķź├źĘźÕż¼▓─ē”ż╦ĪĪĮąųZĪ¦GSA Memory+ Conferenceż½żķż╬ź╣ź»źĻĪ╝ź¾źĘźńź├ź╚

3D-NORżŪżóżņżąĪ󊻿╩ż»ż╚żŌāeš`└▄¶öż╬NANDżĶżĻżŽ╩┬š`└▄¶öż╬NORż╬öĄż¼╣ŌÅ]żŪżóżĻĪóSCMĪ╩Storage Class MemoryĪ╦ż╚żĘżŲż╬Ńt▌öż╦ż╩żĻż”żļĪŻżŌż┴żĒż¾Īó1źėź├ź╚/ź╗źļż╬NANDźšźķź├źĘźÕżŌSCMż╬Ńt▌öżŪżóżļĪŻ

Samsungż╬CXLźßźŌźĻźŌźĖźÕĪ╝źļ

SamsungżŽż╣żŪż╦CXLźßźŌźĻź©źŁź╣źčź¾ź└Ī╝ż╚Ō}żų×æēäż“2021ŃQ5ĘŅż╦╚»╔ĮżĘżŲżżżļĪŻGSA Memory+ ConferenceżŪżŌż│ż╬└^┐┐ż“Ė½ż╗ż┐ĪŻż│ż╬×æēäż╦żŽDDR5 DRAMźßźŌźĻźŌźĖźÕĪ╝źļż“┼ļ║▄żĘżŲż¬żĻĪóż│żņż“Įj╬╠ż╦└▄¶öż╣żļż╚źŲźķźąźżź╚═Ų╬╠ż▐żŪ│╚─źżŪżŁĪóżĘż½żŌźĘź╣źŲźÓż╬źņźżźŲź¾źĘż“▓╝ż▓żļż│ż╚ż¼żŪżŁżļĪŻźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ŲŌżŪĮj╬╠ż╬źßźŌźĻż“╗╚ż”ĪóAIżõHPCż╩ż╔ż╬▒■├ōż╦Ė■ż»ĪŻ

┐▐4ĪĪSamsungż╬CXLźßźŌźĻź©źŁź╣źčź¾ź└Ī╝

CXLżŪ┬Õ╔ĮżĄżņżļźĘź╣źŲźÓČ\Į迎ĪóźßźŌźĻźßĪ╝ź½Ī╝ż└ż▒żŪ├Ż└«żŪżŁżļżŌż╬żŪżŽż╩żżĪŻźĘź╣źŲźÓźßĪ╝ź½Ī╝ż╚Č”ż╦ź│źķź▄źņĪ╝źĘźńź¾ż“┐▐żĻĪóź©ź│źĘź╣źŲźÓż“╣Į├█żĘżŲżżż»ż│ż╚ż¼─_═ūż└ż╚Īóµ£żŲż╬źßĪ╝ź½Ī╝ż¼Įęż┘żŲżżżļĪŻ