ĪųźĘź╣źŲźÓ┼¬Š}╦ĪżŪŠ├õJ┼┼╬üż“1/10Ī┴1/20ż╦─Ńžōż╣żļĪūĪóMentorż╬RhinesĢ■Ėņżļ

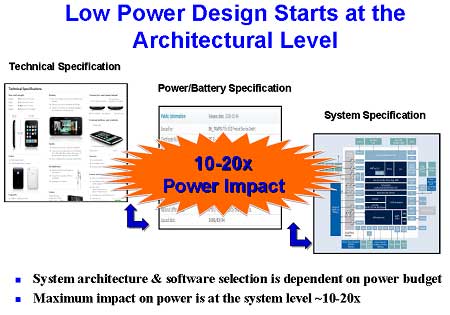

LSIż╬─ŃŠ├õJ┼┼╬ü└▀╝Ŗż¼övŽ®żõźŪźąźżź╣Ī”źūźĒź╗ź╣ż└ż▒żŪżŽż╩ż»ĪóźĘź╣źŲźÓ└▀╝Ŗż╬źņź┘źļż½żķØŁ═ūż╦ż╩ż├żŲżŁż┐ĪŻĪųŠ├õJ┼┼╬üż╬─Ńžōż│żĮż¼żżż▐Īóź©źņź»ź╚źĒź╦ź»ź╣×æēäż“║╣╩╠▓ĮżŪżŁżļź½ź«ż╚ż╩żļźčźķźßĪ╝ź┐ż└ĪūĪŻä▌Mentor Graphics╝ęCEOż╬Walden RhinesĢ■żŽĪóä▌╣±ż╬╣Ł╩¾▓±╝ęGlobalpress Connectionsż¼╝ń╠¢żĘż┐eSummit2009ż╦ż¬żżżŲĪóż│ż╬żĶż”ż╦Įęż┘ĪóźĘź╣źŲźÓźóĪ╝źŁźŲź»ź┴źŃż½żķ─ŃŠ├õJ┼┼╬ü└▀╝Ŗż“╣įż©żą1/10Ī┴1/20ż╦─ŃžōżŪżŁżļż╚żĘż┐ĪŻ

RhinesĢ■żŽĪóżżż½ż╦Š├õJ┼┼╬üżóżļżżżŽź©ź═źļź«Ī╝ż╬─Ńžōż¼─_═ūż½Īó─ŃžōżĘż╩ż▒żņżąźÓĪ╝źóż╬╦Īō¦ż╦Ė½żķżņżļżĶż”ż╦1ź┴ź├źūż╦ĮĖ└迥żņżļź╚źķź¾źĖź╣ź┐┐¶ż¼╗\ż©żŲżżż»ż┐żßŠ├õJ┼┼╬üżŌŲ▒╗■ż╦╗\▓├ż╣żļż╚Įęż┘ż┐ĪŻż┴ż╩ż▀ż╦2007ŃQĖĮ║▀Īóż╣ż┘żŲż╬╚ŠŲ│öüź┴ź├źūż╦ĮĖ└迥żņżŲżżżļź╚źķź¾źĖź╣ź┐┐¶żŽ9.6Ī▀10ż╬18ŠĶĖ─ż└ż╚żĘżŲĪóPentium 4Ī╩PrescottĪ╦ż¼5.7Ī▀10ż╬10ŠĶĖ─╗╚ż’żņżŲżżżļ┐¶ż╦┴Ļ┼÷ż╣żļĪŻż│ż╬┐¶żŽĖČ╚»3638┤╩¼ĪóżóżļżżżŽ14▓»6000╦³└ż┬ėż╦┴Ļ┼÷ż╣żļż╚żżż”Ślż└ĪŻ║Żż╬ż╚ż│żĒĪóź╚źķź¾źĖź╣ź┐┐¶żŽźÓĪ╝źóż╬╦Īō¦ż╚żżż”żĶżĻżŌ╦ĶŃQźĻź╦źóż╦äPżėżŲżżżļĪŻ║ŻĖÕżŽż│żņ░╩æųż╬┐¶ÖCż╦ż╩żļĪŻ

Ę╚┬ė┼┼ÅBĄĪż╦ż¬żżżŲżŌź╣ź▐Ī╝ź╚źšź®ź¾ż└ż▒żŪżŽż╩ż»ĪóMP3źūźņĪ╝źõĪ╝ĄĪē”Īóź½źßźķĄĪē”ż╩ż╔żĄż▐żČż▐ż╩ĄĪē”ż¼║▄żļź│ź¾źąĪ╝źĖź¦ź¾ź╣ż╬╗■┬Õż╦ż╩ż├żŲżżżļĪŻźĻź┴ź”źÓźżź¬ź¾┼┼├ėż╬ź©ź═źļź«Ī╝╠®┼┘ż╬Ė■æųź┌Ī╝ź╣żŽICź┴ź├źūż╬ĮĖ└č┼┘Ė■æųż╬ź╣źįĪ╝ź╔żĶżĻżŌ┤╦żżĪŻ

▐köĄżŪövŽ®żõźŪźąźżź╣ĪóźūźĒź╗ź╣ż╬└ż─cż“Ė½żļż╚Īóź└źżź╩ź▀ź├ź»źčź’Ī╝żŽżŌżŽżõ╩čż’żķż╩ż»ż╩ż├żŲżŁż┐ĪŻź»źĒź├ź»╝■āS┐¶ż“æųż▓żķżņż╩ż»ż╩ż├żŲżŁż┐ż½żķż└ĪŻżĘż½żĘź╔źņźżź¾-źĮĪ╝ź╣ż╬źĻĪ╝ź»┼┼╬«żŽź╚źķź¾źĖź╣ź┐┐¶ż╬╗\▓├ż╚Č”ż╦╗\ż©żļ’łĖ■ż╦żóżļĪŻź▐źżź»źĒźūźĒź╗ź├źĄżŽż╣żŪż╦└Łē”żĶżĻżŌ─ŃŠ├õJ┼┼╬ü▓Įżžż╬×┤▒■ż¼┐╩ż¾żŪżżżļĪŻ

żĮż│żŪżĄżķż╦Š├õJ┼┼╬üż“▓╝ż▓żļż┐żßż╦ĪóżŌżŽżõźĘź╣źŲźÓ└▀╝ŖĪóźóĪ╝źŁźŲź»ź┴źŃ└▀╝Ŗż½żķŠ├õJ┼┼╬üż“╣═╬ĖżĘżŲżżż½ż╩ż▒żņżąż╩żķż╩żżĪŻØŖż╦źĘź╣źŲźÓźóĪ╝źŁźŲź»ź┴źŃż╚źĮźšź╚ź”ź©źóż╬┬ō┘Iż¼Š├õJ┼┼╬üż╬─Ńžōż╦ĮjżŁż»┤¾═┐ż╣żļż╚żĘż┐ĪŻRhinesĢ■żŽĪųiPhoneż╬╔į╦■żŽźąź├źŲźĻÖæ╠┐ż¼ø]żżż│ż╚ĪŻż└ż½żķźŪźČźżź¾ż╦żĶż├żŲ▓“»éż╣żļĪūż╚Įęż┘ĪóĪųźčź’Ī╝ż¼źŪźČźżź¾ż“ź╔źķźżźųż╣żļĪūż╚äė─┤żĘż┐ĪŻ

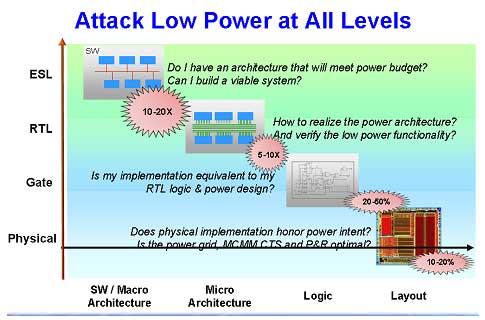

źĘź╣źŲźÓ└▀╝ŖżŪżŽĪóµ£öüż“ż╔ż”źčĪ╝źŲźŻźĘźńź╦ź¾ź░ż╣żļż½Īóźčź’Ī╝ż“ż╔ż”─Ļ▒Iż╣żļż½Īóż╚żżż”ż│ż╚ż¼┐╝ż»┤žĘĖż╣żļĪŻż╦żŌż½ż½ż’żķż║ĪóĪųż│żņż▐żŪż╬źĘź╣źŲźÓ└▀╝ŖŪvż¼Š├õJ┼┼╬üżŽśO╩¼ż╬╠õ¼öżŪżŽż╩żżż╚żąż½żĻż╦övŽ®Č\ĮčŪvĪóźŪźąźżź╣Č\ĮčŪvż╦┼ŽżĘżŲżĘż▐ż├ż┐ĪŻż│żņżŽżżż▐ż└ż╦źĘź╣źŲźÓ└▀╝Ŗż¼ź▐ź╦źÕźóźļ║ŅČ╚ż└ż½żķżĮż╬żĶż”ż╦ż╩ż├żŲżĘż▐ż”Īūż╚Ė└ż”ĪŻPCBæųżŪźčĪ╝źŲźŻźĘźńź╦ź¾ź░ż“ż”ż▐ż»żõżļż│ż╚żŪźĘź╣źŲźÓµ£öüż╬Š├õJ┼┼╬üżŽ1/5Ī┴1/10ż╦žōżļż╚ż▀żŲżżżļĪŻ

żĄżķż╦PCBæųż╬ŗēäż“CPUĪóGPSĪóPMUż╩ż╔ØŁ═ūż╩źŁĪ╝ź│ź¾ź▌Ī╝ź═ź¾ź╚ż╦ż▐ż╚żßżļż╚20%Ī┴50%żŽžōżļĪŻżĮżĘżŲLSI└▀╝ŖżŪICźųźĒź├ź»└▀╝Ŗż╬źčĪ╝źŲźŻźĘźńź╦ź¾ź░żŪ10Ī┴20%║’žōżŪżŁżļĪóż╚żĘż┐ĪŻ

LSI└▀╝Ŗźņź┘źļżŪżŽĪó╝Ī└ż┬ÕLSI└▀╝Ŗż╦┤žżĘżŲĮęż┘ĪóĘQźņź┘źļż╦ż¬ż▒żļ╠õ¼öż“─¾ÅŚżĘż┐ĪŻźūźĒź╗ź╣ż╦ŖZżżØ±═²└▀╝ŖżŪżŽĪóźūźĒź╗ź╣ź│Ī╝ź╩Ī╝ż“ź’Ī╝ź╣ź╚ź▒Ī╝ź╣└▀╝ŖĪ╩ź’Ī╝ź╣ź╚ź│Ī╝ź╩Ī╝Ī╦żŪżõż├żŲżŁż┐ż¼Īó╚∙║┘▓Įż¼┐╩żÓż╦ż─żņĪóź│Ī╝ź╩Ī╝ż╬┐¶żŽŠå╗\ż╣żļĪŻż│ż│żŪź│Ī╝ź╩Ī╝ż╚Š╬żĘżŲżżżļż╬żŽĪóźūźĒź╗ź╣ż╬żążķż─żŁż“╣═╬ĖżĘż╩ż▒żņżąż╩żķż╩żżź½ź«ż╚ż╩żļźūźĒź╗ź╣ż╬ż│ż╚ĪŻ╬Ńż©żąź▓Ī╝ź╚żĘżŁżż┼┼░ĄVthżŽźŽźżź©ź¾ź╔┴Ū╗ęĪóźĒĪ╝ź©ź¾ź╔┴Ū╗ężŪĪ▐5Ī┴10%ż“źąźķż─żŁż╚żĘżŲżŁż┐ż¼ĪóVthż╬żĶż”ż╩ź½ź«ż╚ż╩żļźūźĒź╗ź╣źčźķźßĪ╝ź┐Īóż╣ż╩ż’ż┴ź│Ī╝ź╩Ī╝ż╬┐¶ż¼╗\ż©żŲżżż»ĪŻ130nm└▀╝ŖżŪżŽ4ź│Ī╝ź╩Ī╝ż└ż├ż┐ż╬ż¼Īó90nm└▀╝ŖżŪżŽ10ź│Ī╝ź╩Ī╝Īó65nmż└ż╚21ź│Ī╝ź╩Ī╝░╩æųż╦żŌż╩żļż╚żżż”ĪŻżĄżķż╦ź┐źżź▀ź¾ź░ź▐Ī╝źĖź¾żŌ▓├ż’żļĪŻżĮżņżķż“Ų▒╗■ż╦▓“żŁĪóĖĪŠ┌żĘż╩ż▒żņżą┘抒Ų░║ŅżŽ┤³┬įżŪżŁż╩żżĪŻ

żĮżņżķż“▓“»éżĘż┐æųżŪĪóź═ź├ź╚źĻź╣ź╚źŪĪ╝ź┐ż½żķر═²╣ń└«Ī󟻟Ēź├ź»ź─źĻĪ╝╣ń└«ĪóŪ█└■└▀╝ŖĪóżĮżĘżŲGDS IIĮą╬üż╣żļ┤ųż╦żŌĪó¾H┐¶ż╬VDD┼┼Ė╗ż╬╬«żņżõ┼┼░ĄĪó╝■āS┐¶ż╬║Ū┼¼▓ĮĪóźóź└źūźŲźŻźųż╩ź╣ź▒Ī╝źĻź¾ź░Ī󟻟Ēź├ź»ź─źĻĪ╝ż╬║Ų╣Į└«ż╩ż╔ż╬ź└źżź╩ź▀ź├ź»źčź’Ī╝ż╬─ŃžōĪóź▐źļź┴Vthżõźčź’Ī╝ź▓Ī╝źŲźŻź¾ź░Īóźąź├ź»źąźżźóź╣ż╩ż╔ż╬ź╣ź┐źŲźŻź├ź»źčź’Ī╝ż╬─Ńžōż╩ż╔ż¼ØŁ═ūż╦ż╩żļĪ╩▓╝┐▐Ī╦ĪŻ

æų░╠└▀╝Ŗźņź┘źļżŪżŽĪóESLźņź┘źļż¼RTLźņź┘źļżõPHYźņź┘źļż╩ż╔▓╝░╠źņź┘źļżžż╔ż”▒Ųūxż╣żļż╬ż½ż“─┤ż┘żļż│ż╚ż¼ĮjĄ£Īóż└ż╚żżż”ĪŻż│ż╬źņź┘źļżŪżŽĪóUPFĪ╩Unified Power FormatĪ╦Ę┴╝░ż╦“£ż├żŲĖĪŠ┌ż“╣įż”ĪŻUPFĘ┴╝░żŽż½ż─żŲTIĪóź╬źŁźóż╚źßź¾ź┐Ī╝ż¼Č”Ų▒żŪ│½╚»żĘĪóźĘź╬źūźĘź╣ż╚║YØŹ▓Įż“»éżßż┐źšź®Ī╝ź▐ź├ź╚ż╬ż│ż╚ĪŻż▐ż║ż╣ż┘żŲż╬źčź’Ī╝ż╦┤žĘĖż╣żļŠņĮĻż“Ė½ż─ż▒ĪóźŪĪ╝ź┐źĻźŲź¾źĘźńź¾ż¼┼¼└┌ż½ĪóźĻź╗ź├ź╚żŪżŁżļż½ż╩ż╔ż“ĖĪŠ┌ż╣żļĪŻźčź’Ī╝ż╦┤žĘĖż╣żļźūźĒź░źķźÓż¼└«╬®żĘżŲżżżļż½ż╔ż”ż½ż“µ£öüż╦┼Žż├żŲź½źąĪ╝ż╣żļĪŻż│ż╬żĶż”ż╦żĘżŲźčź’Ī╝ż“┴T╝▒żĘż┐└▀╝Ŗż“źĘź▀źÕźņĪ╝źĘźńź¾żĘż╩ż¼żķĖĪŠ┌żĘżŲżżż»ĪŻ

PCBæųżŪżŽźčź’Ī╝źżź¾źŲź░źĻźŲźŻż“│╬Ū¦żĘĪó╬Ńż©żąŪ█└■ż¼Č╣ż╣ż«żŲź╬źżź║ż¼║▄ż├żŲżżż╩żżż½ż╔ż”ż½ż╩ż╔ż“▓“└ŽżĘ│╬Ū¦ż╣żļĪŻPCBæųżŪżŽÕX▓“└ŽżŌ╣įżżĪóŗēäż╬Ū█Åøż¼┼¼└┌ż½ż╔ż”ż½ż“─┤ż┘żļż┐żßź█ź├ź╚ź╣ź▌ź├ź╚ż“Ė½ż─ż▒ĪóżĮżņż“T┘ćżĘżŲżżż»ĪŻ

OSźņź┘źļżŪżŌźčź’Ī╝ż“┴T╝▒żĘż┐RTOSĪ╩źĻźóźļź┐źżźÓOSĪ╦ż╚żĮż”żŪżŽż╩żż└@├ōż╬LINUXż“╚µż┘żļż╚Īóźčź’Ī╝ż“┴T╝▒żĘż┐RTOSż└ż╚Š├õJ┼┼╬üżŽ╗╚├ōż╣żļźßźŌźĻĪ╝ż╦żŌżĶżļż¼Īó5Ī┴11%║’žōżŪżŁżļż╚żĘżŲżżżļĪŻ

LSI└▀╝Ŗż╬╬Ńż╚żĘżŲ802.11ż╬MACźūźĒź╗ź├źĄż╬źčź’Ī╝ż“źŽĪ╝ź╔ź”ź©źóźĻź├ź┴ĪóźĮźšź╚ź”ź©źóźĻź├ź┴ĪóźĘź¾ź░źļźąź╣Īóź└źųźļźąź╣ż╩ż╔ż╦ż─żżżŲż╬äh▓┴╬Ńż“Šę▓żĘż┐ĪŻżĮż╬±T▓╠ĪóźĘź¾ź░źļźąź╣żŪż╣ż┘żŲźŽĪ╝ź╔ź”ź©źóżŪ╝┬ĖĮż╣żļż╚380.7mWżŪĪóź└źųźļźąź╣ż“╗╚żżżżż»ż─ż½ż╬ĄĪē”ż“źĮźšź╚ź”ź©źóżŪ╝┬ĖĮż╣żļŠņ╣ńżŽ766.8mWżŌ┼┼╬üż“┐®ż”ż│ż╚ż“Ė½ż╗ż┐ĪŻ

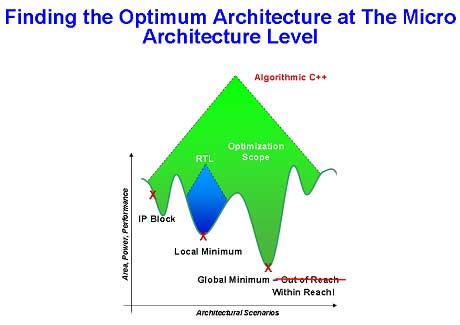

═ūżŽĪóź┴ź├źūĀC└čż╚Š├õJ┼┼╬üĪó└Łē”ż╬║Ū┼¼▓Įż¼IPźųźĒź├ź»ż└ż▒żŪ║Ū┼¼▓ĮżĘżŲżżżŲżŌĪóźĘź╣źŲźÓµ£öüżŪ║Ū┼¼▓ĮżŪżŁżŲżżżļż½ż╔ż”ż½ż’ż½żķż╩żżĪŻRTLźņź┘źļżŪ└▀╝ŖżĘżŲżżżŲżŌ├▒ż╩żļźĒĪ╝ź½źļż╩║Ū┼¼▓Įż½żŌżĘżņż╩żżĪŻżĘż½żĘĪóĪųر═²└▀╝Ŗż“Ņ~╗╚żĘżŲź░źĒĪ╝źąźļż╦║Ū┼¼▓Įż╣żņżąŠ├õJ┼┼╬üż“20Ū▄żŌ▓╝ż▓żķżņżļĪŻżĮż╬ż┐żßż╦żŽØ±═²└▀╝Ŗż“żŌż├ż╚śOŲ░▓Įż╣żļż│ż╚ż¼ź½ź«ż╚ż╩żļĪūż╚RhinesĢ■żŽ±Tż¾ż└ĪŻ