×æļ]äóÅøĪ”║Ó╬┴ż╬·t┐ā▓±ż½żķ╚ŠŲ│öü┴Ē╣ńČ\Įč·tż╦╩čż’ż├żŲżŁż┐ź╗ź▀ź│ź¾J

╚ŠŲ│öü×æļ]äóÅøżõ║Ó╬┴ż╬·t┐ā▓±żŪżóżļź╗ź▀ź│ź¾Ī”źĖźŃźčź¾ż¼╚ŠŲ│öü┴Ē╣ń·tż╬══┴Ļż“Ė½ż╗żŲżŁż┐ĪŻDACĪ╩└▀╝ŖśOŲ░▓Į▓±Ą─Ī╦ż╚żżż”EDAĪ╩┼┼╗ę└▀╝ŖśOŲ░▓ĮĪ╦ŠÅČ╚ż¼SEMIż╬├µż╦┴╚ż▀╣■ż▐żņĪó╚ŠŲ│öü└▀╝Ŗż╚×æļ]ż¼ŖZż┼żżżŲżżżļĪŻ└ĶĮĄ│½╠¢żĄżņż┐2024ŃQż╬ź╗ź▀ź│ź¾żŽĪóķL│░ż½żķżŽIPź┘ź¾ź└Ī╝żõźšźĪźųźņź╣╚ŠŲ│öü┤ļČ╚ż╩ż╔żŌ╗▓▓├ż╣żļżĶż”ż╦ż╩ż├ż┐ĪŻźķźėź└ź╣ż╬żĶż”ż╩źšźĪź”ź¾ź╔źĻżŌ║“ŃQż╦¶öżŁĮą·t╝ęŖõż╦═ĶżŲżżżļĪŻ

┐▐1ĪĪź╗ź▀ź│ź¾Ī”źĖźŃźčź¾2024ż╬╔„Ę╩

“£═ĶĪóź╗ź▀ź│ź¾żŽ╚ŠŲ│öü×æļ]äóÅøż╚▓Į│ž║Ó╬┴żõĄĪ│Ż┼¬ż╩ŗ║Óż╩ż╔ż╬┤ļČ╚ż¼Įą·tżĘżŲż¬żĻĪó═ĶŠņŪvżŽżĮżņżķż“ĻPŲ■ż╣żļäŅ║▀źąźżźõĪ╝żŪżóż├ż┐ĪŻż╚ż│żĒż¼Īóż│ż│┐¶ŃQĪóIoTżõAIĪó5Gż╩ż╔ITŠÅČ╚żŌĮą·tŖõż╦║╬żĻŲ■żņĪóżĮżņżķż“▐kż─ż╬┤ļ▓Ķż╚żĘżŲ░ĘżżĪó╚ŠŲ│öüŠÅČ╚ż╚┤žŽó¤²ż▒żĶż”ż╚żĘżŲżŁż┐ĪŻżŌż┴żĒż¾ĪóŪ█└■żõź▓Ī╝ź╚─╣ż╩ż╔ż╬╚∙║┘▓ĮČ\Įčż¼╣įżŁĄ═ż▐ż├ż┐ż┐żßż╬∙ZŲ∙ż╬║÷żŪżŽżóż├ż┐ĪŻ

źūźĒź╗ź╣ż╦żŽŪ█└■╔²żõ┤ų│ųż╩ż╔ż╬╚∙║┘▓ĮżŽČÉŽ┬żĘżŲż¬żĻĪó3╝ĪĖĄ╣Įļ]ż╬ź╚źķź¾źĖź╣ź┐żõŪ█└■żõźėźóź█Ī╝źļż╩ż╔ż“║╬├ōż╣żļż│ż╚żŪĮĖ└č┼┘ż“æųż▓żŲżŁż┐ĪŻ╬Ńż©żą7nmźūźĒź╗ź╣ż╚żŽĪóŪ█└■╔²żŽ14Ī┴16nmż╚╣Łżżż▐ż▐Īó├▒░╠ĀC└č┼÷ż┐żĻż╬ź╚źķź¾źĖź╣ź┐┐¶ż“╠¾1▓»Ė─Ę┴└«żŪżŁżļźūźĒź╗ź╣ż╚Ė½ż╩żĘżŲżŁż┐ĪŻż│ż╬3╝ĪĖĄ▓ĮČ\Į迎DTCOĪ╩Design Technology Co-OptimizationĪ╦Č\ĮčżóżļżżżŽź©źĻźóź╣ź▒Ī╝źĻź¾ź░ż╩ż╔ż╚Ō}żążņĪó╚∙║┘▓Įż╗ż║ż╦ĮĖ└č┼┘ż“æųż▓Īó├▒░╠ĀC└č┼÷ż┐żĻż╬ź╚źķź¾źĖź╣ź┐┐¶ż╦żĶż├żŲĪó5nmźūźĒź╗ź╣ź╬Ī╝ź╔Īó3nmźūźĒź╗ź╣ź╬Ī╝ź╔Īó2nmźūźĒź╗ź╣ź╬Ī╝ź╔ż╩ż╔ż╚Š╬żĘżŲżŁż┐ĪŻ

ż│ż╬ż┐żß“£═Ķż╚░ŃżżĪóźūźĒź╗ź╣ź╬Ī╝ź╔ż¼┐╩żÓż╦ż─żņĪóźšźĻź├źūźšźĒź├źūż“żŽżĖżßż╚ż╣żļź╣ź┐ź¾ź└Ī╝ź╚ź╗źļż╬źĒźĖź├ź»ź▓Ī╝ź╚ż“└▀╝ŖżĘ─ŠżĘżŲżŁż┐ĪŻ▓Ż┘pż╬ż▀ż╩ż╚ż▀żķżżż╦żóżļTSMCźŪźČźżź¾ź╗ź¾ź┐Ī╝żŪżŽŲ³╦▄┐═IC└▀╝ŖŪvż¼ź╣ź┐ź¾ź└Ī╝ź╔ź╗źļż╬║ŅżĻ─ŠżĘ║ŅČ╚ż╦“£Ą£żĘżŲżżżļĪŻż─ż▐żĻIC└▀╝Ŗż╚źūźĒź╗ź╣ż╬╬ŠöĄż¼ĄßżßżķżņżļżĶż”ż╦ż╩ż├żŲżŁż┐ż╬żŪżóżļĪŻEDAŠÅČ╚ż¼SEMIż╦ŲDżĻ╣■ż▐żņżļż│ż╚żŽśO─śż╬└«żĻ╣įżŁż└ż├ż┐ĪŻ

żżż▀żĖż»żŌNvidiaż╬CEOżŪżóżļJensen HuangĢ■ż¼ĪóĪų╚∙║┘▓ĮČ\Į迎┘Vż▐żĻż─ż─żóżļż¼Īóź│ź¾źįźÕĪ╝źŲźŻź¾ź░źčź’Ī╝ż“æųż▓żĶż╚żżż”═ūĄßżŽż▐ż╣ż▐ż╣äėż▐ż├żŲżżżļĪūĪóż╚Įęż┘ż┐ż│ż╚żŽĪó╚∙║┘▓ĮżĘż╩ż»żŲżŌĮĖ└č┼┘ż“żĄżķż╦æųż▓ĪóICż╬└Łē”Ī”Š├õJ┼┼╬üż“żĄżķż╦▓■║¤żĘżŲż█żĘżżż╚żżż”═ūĄßż¼╗\ż©żŲżżżļż│ż╚ż“┐āżĘżŲżżżļĪŻ

└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░ż╦ÅRų`

żĮż│żŪĮĖ└č┼┘ż“▐kĄżż╦æųż▓żķżņżļČ\Įčż╚żĘżŲĪó└Ķ├╝źčź├ź▒Ī╝źĖČ\Įčż¼┼ąŠņżĘż┐ĪŻNvidiaż╬║Ū┐ĘGPUż╬BlackwellżŽ2ź┴ź├źū╣Į└«ż½żķż╩ż├żŲż¬żĻĪóĪųź┴ź├źū1Ė─żŽźūźĒź╗ź╣Č\ĮčżŪ×æļ]żŪżŁżļ║ŪĮjż╬ĀC└čżŪżóżļĪūż╚Huang CEOżŽĮęż┘żŲżżżļĪŻż─ż▐żĻĪóź┴ź├źūĀC└čż“ĮjżŁż»żĘżŲĮĖ└č┼┘ż“æųż▓ż┐żżż¼Īó╩Ōé╬ż▐żĻż¼ĄK▓Įż╣żļż┐żß2ź┴ź├źū╣Į└«ż╦żĘż┐ż╬żŪżóżļĪŻ2ź┴ź├źūżŪ2000▓»ź╚źķź¾źĖź╣ź┐░╩æųż“ĮĖ└čżĘżŲżżżļĪŻ

ź╗ź▀ź│ź¾ÄźźĖźŃźčź¾żŪżŽĪó└Ķ├╝źčź├ź▒Ī╝źĖż╦ć@ŠĶżĻż“æųż▓ż┐ź│ź═ź»źŲź├ź»źĖźŃźčź¾ż╬źųĪ╝ź╣ż╦┐═ż└ż½żĻż¼żŪżŁż┐ĪŻŲ▒╝꿎╚ŠŲ│öüĖÕ╣®µćż“1Ė─ż╬╗Ņ║Ņż½żķ╬╠ŠÅż▐żŪż“├┤ż”ż┐żßĪó┴╚ż▀╬®żŲż╬╬╠ŠÅż“æąż▒╔ķż”OSATĪ╩Out-Sourced Assembly and TestżŪżŽż╩ż»ĪóśOżķż“OSRDAĪ╩Outsourced Semiconductor Research Development & AssemblyĪ╦ż╚Ō}ż¾żŪżżżļĪŻ80°Cż╚żżż”─ŃčażŪź┴ź├źūż“└▄╣ńżŪżŁżļČ\Įčż“│½╚»Īó2024ŃQ┼┘żŽż╣żŪż╦400°P░╩æųż╬│½╚»░Ų°Pż“£p▓mżĘż┐ż╚żżż”ĪŻĖĮėXżŪżŽż▐ż└20µmĘ┬ż╬TSV▓├╣®ż“Č©╬ü▓±╝ęż╦░č▓mżĘżŲżżżļż¼Īó26ŃQŗī2╗═╚Š┤³ż½żķżŽTSVĪ╩Through Silicon ViaĪ╦ż╬└ņ├ōźķźżź¾ż“╝ęŲŌż╦└▀ż▒Īó10µmĘ┬żŪRDLĪ╩║ŲŪ█└■┴žĪ╦2┴žż╬źżź¾ź┐Ī╝ź▌Ī╝źČĘ┴└«ż“═Į─ĻżĘżŲżżżļĪ╩┐▐2Ī╦ĪŻ

![TSV/RDL ╚∙║┘▓ĮéāĀC╣Įļ] / ź│ź═ź»źŲź├ź»źĖźŃźčź¾](/archive/editorial/industry/img/20241218-connectecjapan.jpg)

┐▐2ĪĪź┴ź├źūźņź├ź╚╝┬äóż╦┐╩Įąż╣żļź│ź═ź»źŲź├ź»źĖźŃźčź¾

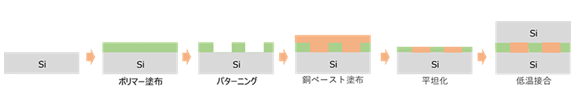

ź│ź═ź»źŲź├ź»ż╬Č©╬ü▓±╝ężŪżŌżóżļź└źżź╗źļżŪżŽĪóź¼źķź╣źżź¾ź┐Ī╝ź▌Ī╝źČż╬TSV╣”ż“ȧż▒żŲCuĪ╩Ų╝Ī╦ż“ļmżß╣■żÓźūźĒź╗ź╣ż╦Īó“£═Ķż╬źßź├źŁżŪżŽż╩ż»ĪóCuź┌Ī╝ź╣ź╚ż“╗╚ż├ż┐░§║■╣®µćż“ŠW├ōż╣żļĪŻĘ┴└«╗■┤ųż╬ø]Į╠ż╚ź▄źżź╔ż╬╚»Ö┌ż“╦╔ż░ż╚żżż”┴└żżż¼żóżļĪŻCuź┌Ī╝ź╣ź╚ż╚żżż©ż╔żŌźĘĪ╝ź╔źßź┐źļż“¤²ż▒żļĮĻż▐żŪżŽŲ▒żĖż└ż¼Īó░§║■żŪŪ█└■ż“Ę┴└«ż╣żļĪŻżĮż╬Øiż╦▐k╗■┼¬ż╩ܦĘeźšźŻźļźÓż“äóŠÆżĘ┐┐ȧ├µżŪ░§║■ĪóŪ█└■żĘż┐ĖÕĪóܦĘeźšźŻźļźÓż“Į³ĄŅżĘźĘź¾ź┐źĻź¾ź░żĘĪóź┌Ī╝ź╣ź╚żŪ═Žż½żĘż┐Ń~ĄĪ═Ž║▐ż“Į^╚»żĄż╗żļĪŻ╔ĮĀCæųż╬═Š╩¼ż╩Cuż“Į³ĄŅżĘĪ󟎟żźųźĻź├ź╔ź▄ź¾źŪźŻź¾ź░żžż╚┐╩żÓĪ╩┐▐3Ī╦ĪŻ

┐▐3ĪĪŲ╝ż“źßź├źŁżŪżŽż╩ż»░§║■żŪĘĻļmżßż╣żļź└źżź╗źļĪĪĮąųZĪ¦ź└źżź╗źļ

└Ķ├╝źčź├ź▒Ī╝źĖź¾ź░żŪżŽĪó╚ŠŲ│öüĖÕ╣®µćŖõż╚źūźĻź¾ź╚┤łČ\ĮčŖõż½żķż╬ż╗żßż«╣ńżżż╚ż╩żļĪŻż│żņż▐żŪźūźĻź¾ź╚┤łż╬CADż“įu┴Tż╚żĘżŲżŁż┐┐▐Ė”żŽĪó2.5D-ICżõ3D-ICĪóź┴ź├źūźņź├ź╚ż╩ż╔ż╬Ū█└■Ī”źņźżźóź”ź╚Ī”ĖĪŠ┌ż╩ż╔ż╦EDAź─Ī╝źļĪųCR-8000Īūż¼╗╚ż©żļż│ż╚ż“┐āżĘż┐ĪŻØŖż╦Īóź▌źĻź▐Ī╝ż╬RDLźżź¾ź┐Ī╝ź▌Ī╝źČż“╗╚ż├żŲ╚∙║┘ż╩źėźóź█Ī╝źļż└ż╚Ū█└■┴ž┐¶ż“Įj╔²ż╦║’žōżŪżŁżļż│ż╚ż“╝┬Š┌żĘż┐ĪŻ“£═Ķż╬Ū█└■╔²Ī”┤ų│ųż¼8µm/8µmż└ż╚║ŲŪ█└■┴žż¼9Ī┴10┴žØŁ═ūż└ż├ż┐ż╬ż╦×┤żĘżŲĪó2µm/2µmż└ż╚2┴žµć┼┘ż╦ż╩żļż│ż╚ż“CR-8000ż¼╝┬Š┌żĘż┐ĪŻ

ź┴ź├źūźņź├ź╚żõ3D-ICżŪżŽĪóź┴ź├źūŲ▒╗╬ż“└č┴žżĘżŲż½żķ╔į╬╔ēäż¼ż’ż½żļżĶż”żŪżŽŠ}ęÆżņż└ĪŻØ±═²│žæųż╬ÕXżõ╬«öüĪó┼┼╝¦Ąż│žż╩ż╔ż╬źĘź▀źÕźņĪ╝źĘźńź¾ż“įu┴Tż╚ż╣żļAnsysżŽTSMCż╬EDAź┘ź¾ź└Ī╝ż╬ĮĖż▐żĻżŪżóżļĪóTSMC 3DFabric Allianceż╬źßź¾źąĪ╝żŪżŌżóżļĪŻ

Ų▒╝꿎└ĶĘŅĪóNvidia Modulusż╚Ō}żążņżļAIźšźņĪ╝źÓź’Ī╝ź»ż“ĪóśO╝ęż╬ź»źķź”ź╔ź┘Ī╝ź╣ż╬źėź├ź░źŪĪ╝ź┐▓“└Žźūźķź├ź╚źšź®Ī╝źÓĪųAnsys SeaScapeĪūż╦┼²╣ńżĘż┐ż╚╚»╔ĮżĘż┐ż¼Īó║ŻövżĮż╬└«▓╠ż“Ė½ż╗ż┐ĪŻSeaScapeż╦żŽAnsysż╬źčź’Ī╝źżź¾źŲź░źĻźŲźŻżõ┐«═Ļ└Łż╩ż╔ż╬źūźķź├ź╚źšź®Ī╝źÓż“ĮĖ└čżĘżŲżżżļĪŻ4mm│čż╬ź┴ź├źūźņź├ź╚ż╬ča┼┘╩¼╔█ż““£═Ķż╬źŌźŪźļź┘Ī╝ź╣ż╬źĘź▀źÕźņĪ╝ź┐ż└ż╚2╝ĪĖĄ╔Į┐āż╦żĶżļ▓“└Ž±T▓╠ż“Ė½żļż╬ż╦1╩¼19╔├ż½ż½ż├ż┐ż¼ĪóNvidia Modulusż╬ĄĪ│Ż│žØ{ż└ż╚0.29╔├żŪŲ▒┼∙ż╬±T▓╠ż“įuż┐Ī╩┐▐4Ī╦ĪŻżĄżķż╦ż│żņż“└č┴žżĘż┐3D-ICżŪżŽ“£═Ķź─Ī╝źļżŪ9╩¼10╔├ż½ż½ż├ż┐ż¼ĪóĄĪ│Ż│žØ{ź─Ī╝źļżŪżŽ0.42╔├żŪŲ▒┼∙ż╬±T▓╠ż“įuż┐ĪŻAIż╬░ę╬üżŽż╣żĄż▐żĖżżĪŻ

┐▐4ĪĪAIż“Ų│Ų■żĘż┐źĘź▀źÕźņĪ╝ź┐żŽ└č┴žżĘż┐2ź┴ź├źūż╬ÕX╩¼╔█źĘź▀źÕźņĪ╝ź┐żŽ1300Ū▄Å]żżĪĪĮąųZĪ¦Ansys

ż▐ż┐Īó║Żövż╬ź╗ź▀ź│ź¾Ī”źĖźŃźčź¾żŪżŽĪó▒č╣±ż╬╚ŠŲ│öü┤ļČ╚ż¼╗╚£I├─ż╚żĘżŲØ▓┐¶╝ęż¼╗▓▓├żĘż┐ĪŻĮą·tż│żĮżĘż╩ż½ż├ż┐ż¼ĪóżĮż╬ż”ż┴ż╬2╝ęż╚źżź¾ź┐źėźÕĪ╝żŪżŁż┐ĪŻż▐ż┐źóźżźļźķź¾ź╔ż½żķżŌ╚ŠŲ│öüżõ┤žŽó┤ļČ╚ż╬═Č├ūż╦Ų▒╣±Ž×ĮBŠÅČ╚│½╚»─Żż¼śOżķżõż├żŲżŁżŲźóźżźļźķź¾ź╔ż╦ż¬ż▒żļ╚ŠŲ│öüŠÅČ╚ż╦ż─żżżŲ▓“└ŌżĘż┐ĪŻ±śŽčż½żķżŽĪó╣±▓╚▓╩│žĄ┌Č\Įč░čµ^▓±ż¼ź╗ź▀ź│ź¾Ī”źĖźŃźčź¾żŪź╗ź▀ź╩Ī╝ż“│½╠¢żĘĪ󱜎čż╬▌xŠņ─┤Øh▓±╝ęTrendForceż¼│½╠¢┤³┤ų├µż╦▓±ŠņŖZż»ż╬ź█źŲźļżŪź╗ź▀ź╩Ī╝ż“│½╠¢żĘż┐ĪŻŲ³╦▄ż╬ź╣ź┐Ī╝ź╚źóź├źūż╬EdgeCortixżŌĮą·tżĘĪóŲ▒╝ęż╬ź©ź├źĖAI├ōź┴ź├źūSakuraźĘźĻĪ╝ź║ż╬źĒĪ╝ź╔ź▐ź├źūż“Ė½ż╗ż┐ĪŻż▐ż┐Īóźóź╔źąź¾źŲź╣ź╚żŽ├µ┤³Ęą▒─╝Ŗ▓Ķż╚żĘżŲż╬┬Š╝ęż╚ż╬ź©ź│źĘź╣źŲźÓ╣Į├█ż╦Ė■ż▒ż┐źūźĒźĖź¦ź»ź╚ż“£½żķż½ż╦żĘż┐ĪŻż│żņżķż╬Č\Įčż╦┤žżĘżŲżŽĪóĖÕŲ³źņź▌Ī╝ź╚ż╣żļĪŻ