TSMCż╬źŲź»ź╬źĒźĖĪ╝źĒĪ╝ź╔ź▐ź├źūĪ╩2Ī╦

TSMC▓±─╣ż╬Mark LiuĢ■Ī╩┐▐5Ī╦ż¼2ĘŅż╬ISSCCĪ╩International Solid-State Circuits ConferenceĪ╦żŪ╣ų▒ķżĘż┐TSMCźŲź»ź╬źĒźĖĪ╝źĒĪ╝ź╔ź▐ź├źūĪ╩╗▓╣═½@╬┴1Ī╦ż╬▓“└ŌĄŁĄ£ż╬¶öżŁżŪżóżļĪ╩╗▓╣═½@╬┴2Ī╦ĪŻĖÕ╚ŠżŽĪó└▀╝Ŗż╚źūźĒź╗ź╣ż╬║Ū┼¼▓Įżõ2╝ĪĖĄ║Ó╬┴Īóź┴ź├źūźņź├ź╚ĪóØŖ─Ļź╔źßźżź¾źóĪ╝źŁźŲź»ź┴źŃż╩ż╔╠ż═Ķż╬źŲĪ╝ź▐ż╚ż╩żļĪŻ

╔«ŪvĪ¦ Pete SingerĪóSemiconductor DigestįćĮĖ─╣

┐▐5ĪĪTSMC▓±─╣ż╬Mark LiuĢ■ĪĪ┼ņ»BĮj(lu©░)│žż╚ż╬─¾Ę╚żŪ═ĶŲ³żĘż┐╗■ż╬└^┐┐

DTCOż¼ĮĖ└č┼┘Ė■æųż╦╣ūĖź

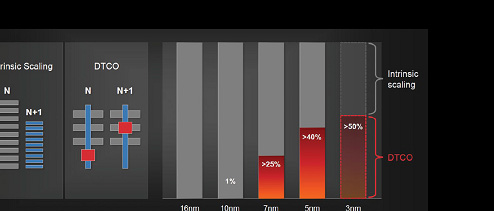

ż│żņż▐żŪż╬Č\Įč└ż┬ÕżŪżŽĪóDTCOĪ╩Design Technology Co-Optimization: └▀╝ŖČ\Įčż╚źūźĒź╗ź╣ż╬║Ū┼¼▓ĮĪ╦żŽź╣ź▒Ī╝źĻź¾ź░ż╚±Tżėż─żżżŲĮĻ╦Šż╬źĒźĖź├ź»╠®┼┘żõź┴ź├źūź│ź╣ź╚ż╬║’žō(f©┤)ż“╝┬ĖĮżĘżŲżŁż┐ĪŻĪųDTCOż╦żĶż├żŲĪóź│ź¾ź┐ź»ź╚ż╬ż─żżż┐ź▓Ī╝ź╚źįź├ź┴żõ║ŪŠ«ż╬źßź┐źļźįź├ź┴ż╬żĶż”ż╩ź╣ź▒Ī╝źĻź¾ź░╝▄┼┘żŽĪó╝┬║▌ż╬Č\Įčż╬źĒźĖź├ź»╠®┼┘ż“╚┐▒ŪżĘż╩ż»ż╩ż├ż┐ż│ż╚ż“╗ž╝~żĘżĶż”ĪŻźóź»źŲźŻźųōļ░Ķż╬æųż╦Ę┴└«ż╣żļź▓Ī╝ź╚ź│ź¾ź┐ź»ź╚żõĪóFinFETŲ▒╗╬ż“╩¼▀`ż╣żļ├▒▐k│╚ÜgźųźņĪ╝ź»Ī╩źóźżźĮźņĪ╝źĘźńź¾Ī╦ĪóźšźŻź¾┐¶ż╬žō(f©┤)Š»Ī󿥿▐żČż▐ż╩śOĖ╩┼D╣ńČ\Įčż╩ż╔ż╬┐ʿʿżČ\Įčż╬ØŖ─╣ż╦ż─ż╩ż¼ż├ż┐Ī╩┐▐6Ī╦Īūż╚LiuĢ■żŽĮęż┘żļĪŻ

┐▐6ĪĪDTCOż╬Ė·▓╠żŽģsĘ▓ĪĪ║ĖżŽź╣ź▒Ī╝źĻź¾ź░ż╚RTCOż╬╚µ│ėĪóīÜż╬ź░źķźšżŽż│żņż½żķż╬3nmźūźĒź╗ź╣ż╦Ė■ż▒─_═ūż╦ż╩żļDTCOż╚“£═Ķż╬ź╣ź▒Ī╝źĻź¾ź░ż╬│õ╣ńĪĪĮąųZĪ¦TSMCĪóSemiconductor Digest

żĄżķż╦Īųż│ż╬±T▓╠ĪóŲ▒żĖ└▀╝ŖźļĪ╝źļżŪ1└ż┬Õżóż┐żĻż╬ź┴ź├źūźĄźżź║ż“35~50%Į╠Š«żŪżŁĪóźĒźĖź├ź»╠®┼┘żŽ1.8Ū▄ż╦æųż¼ż├ż┐ĪŻźóź╩źĒź░żõIOŗ╩¼ż╬żĶż”ż╦żóż▐żĻź╣ź▒Ī╝źĻź¾ź░żŪżŁż╩żżōļ░Ķż“┤▐żÓŠņ╣ńżŪżĄż©żŌĪóż│żņż└ż▒Š«żĄż»żŪżŁż┐ĪŻDTCOż╬╣ūĖźżŽĪóĮø(j©®ng)═Ķż╬ź╬Ī╝ź╔żŪ└«─╣żĘ¶öż▒żķżņżļĪūż╚Ų▒Ģ■żŽ┤³┬įż╣żļĪŻ

─Ń╝ĪĖĄ║Ó╬┴ż╦┤³┬į

LiuĢ■żŽ║ŻĖÕŃ~╦Šż╩Ė”ē|╩¼╠Ņż“║╬żĻæųż▓żŲżżżļĪŻż▐ż║2╝ĪĖĄ║Ó╬┴ż╬żĶż”ż╩─Ń╝ĪĖĄ║Ó╬┴żŪżóżļĪŻż│żņżŽFEOLĪ╩ź╚źķź¾źĖź╣ź┐×æļ]ż╬ØiźūźĒź╗ź╣Ī╦żŪżŌBEOLĪ╩¾H┴žŪ█└■ż╩ż╔ź╚źķź¾źĖź╣ź┐Ę┴└«ĖÕż╬źūźĒź╗ź╣Ī╦żŪżŌż┐ż»żĄż¾ż╬ĄĪ▓±ż¼żóżĻżĮż”ż└ż╚żżż”ĪŻ

Īų─Ń╝ĪĖĄ║Ó╬┴żŽ╚ŠŲ│öüż╦ż╚ż├żŲ┐ʿʿżż¼Īó║ŪŖZżŪżŽ─_═ūż╩źųźņĪ╝ź»ź╣źļĪ╝ż¼Ö┌ż▐żņżŲżżżļĪŻ╬Ńż©żąĪó┼÷╝꿎╣Ōēä䮿╬├▒±TŠĮŽ╗│čŠĮÅUBNż“ź”ź¦Ī╝źŽæä╠ŽżŪ└«─╣żĄż╗ż┐Īūż╚LiuĢ■żŽĮęż┘ĪóżĮż╬Ė”ē|ż¼2020ŃQ3ĘŅż╬▓╩│ž╗’Natureż╦ĘŪ║▄żĄżņż┐ĪŻ╝ĪĖĄż╬─Ńżżź┴źŃź¾ź═źļżõ─cĀCż╬ż│żņżķż╬║Ó╬┴żŽĪóŪż┴Tż╬┤ł║Ó╬┴ż╦─Ńča(b©│)żŪĘ┴└«żŪżŁżļż┐żßĪóźóź»źŲźŻźųż╩źĒźĖź├ź»żõźßźŌźĻż╬┴žż╦3╝ĪĖĄ┼¬ż╦Ę┴└«ż╣żļ╠Oż“│½żżż┐ĪŻ

żŌż”▐kż─Īó─Ń╝ĪĖĄ║Ó╬┴ż╚żĘżŲżŽ1╝ĪĖĄż╬ź½Ī╝ź▄ź¾ź╩ź╬ź┴źÕĪ╝źųż¼żóżļĪŻĮø(j©®ng)═Ķż╬ź╚źķź¾źĖź╣ź┐Ńt▌öżŪżóżļĪŻĪųź½Ī╝ź▄ź¾ź╩ź╬ź┴źÕĪ╝źųż“ź┴źŃź¾ź═źļż╚żĘżŲ╗╚ż”ż┐żßż╬╠õ¼öżŽĪóø]ź┴źŃź¾ź═źļź╚źķź¾źĖź╣ź┐ż“Ę┴└«ż╣żļż┐żßż╬Ū÷żżź▓Ī╝ź╚¤©▓Į╦ņż╬Ę┴└«żŪżóżļĪŻż│żņż▐żŪż╬Ų╝Ū█└■żõSiGeĪ󟎟šź╦ź”źÓ¤©▓Į╦ņĪóżżżĒżżżĒż╩ź▓Ī╝ź╚┼┼Č╦║Ó╬┴ż╩ż╔ż╬╝Īż╦═Ķżļ║Ó╬┴ż╚żĘżŲżŌż├ż╚═źżņż┐║Ó╬┴ż¼ź╚źķź¾źĖź╣ź┐×æļ]żŪŲ│Ų■żĄżņżļżĶż”ż╦ż╩żĒż”ĪŻ┐Ę║Ó╬┴ż╬ŠW(w©Żng)├ōżŽFEOLż└ż▒żŪżŽż╩żżĪŻ┼÷╝ężŪżŽBEOLżŪCoĪ╩ź│źąźļź╚Ī╦żõRuĪ╩źļźŲź╦ź”źÓĪ╦ż“╗╚ż├żŲżĶżż±T▓╠ż“įużŲżżżļĪūż╚LiuĢ■żŽĖņż├ż┐ĪŻ

ź┴ź├źūźņź├ź╚żŪźĘź╣źŲźÓż“║Ū┼¼▓Į

└Ķ┐╩ż╬źčź├ź▒Ī╝źĖź¾ź░żõĮĖ└č▓Įż╬źżź╬ź┘Ī╝źĘźńź¾ż╦┤žżĘżŲżŌLiuĢ■żŽ┐©żņż┐ĪŻ╚ŠŲ│öüČ╚─cżŽż╣żŪż╦ĪóĖ─Ī╣ż╬ź┴ź├źūż╬└▀╝ŖĪ”×æļ]ż╣żļż│ż╚ż“«Ćż©żŲĪóźĘź╣źŲźÓż╦ĮĖ└čż╣żļż│ż╚ż“╗ŽżßżŲżżżļĪŻĪųż│ż”żżż├ż┐ź┴ź├źūżŽź┴ź├źūźņź├ź╚ż╚Ō}żążņĪóź█ź├ź╚ź╚źįź├ź»ź╣ż╦ż╩ż├żŲżżżļĪŻ└Ķ┐╩ż╬╚ŠŲ│öü┤ļČ╚żŽż╣żŪż╦ź┴ź├źūźņź├ź╚ż“ĮĖ└čżĘżŲżżżļĪŻ╬Ńż©żąTSMCżŪżŽCoWoSż╚żżż”źčź├ź▒Ī╝źĖČ\Įčż“2011ŃQż╦Ų│Ų■żĘĪó90░╩æųż╬×æēäż“╬╠ŠÅżĘżŲżżżļĪŻż│żņżŽźßźŌźĻź┴ź├źūż╚źĒźĖź├ź»ż“ĮĖ└čżĘż┐×æēäżŪĪó└Łē”ż“æųż▓żļż┐żßż╦źĒźĖź├ź»ż╦źĒźĖź├ź»ż“ĮĖ└čżĘż┐×æēäżŌżóżļĪūż╚LiuĢ■żŽĖ└ż”ĪŻ

Ų▒Ģ■żŽĪóĪųźĘź¾ź░źļź┴ź├źūż╬SoCĪ╩System on a ChipĪ╦ż└ż▒ż¼żŌżŽżõ║Ū┼¼ż╩źĘź╣źŲźÓż“║Ņżļż╚żŽĖ┬żķż╩żżĪŻ┐¶Ė─ż╬ź┴ź├źūż“1źčź├ź▒Ī╝źĖż╦ĮĖ└čżĘż┐źĘź╣źŲźÓż¼ż▐ż╣ż▐ż╣─_═ūż╦ż╩ż├żŲżŁż┐Īūż╚ĖņżĻĪóźčź├ź▒Ī╝źĖČ\Įčż╬─_═ū└Łż“╗ž╝~ż╣żļĪŻż│ż”żżż├ż┐×æē俎ØŖÖzż╩ĄĪē”ż“╝┬ĖĮżĘĪó└Łē”Īóź©ź═źļź«Ī╝Ė·╬©ĪóĮĖ└č┼┘Īóź│ź╣ź╚ĪóĄĪē”ż¼║Ū┼¼▓ĮżĄżņżŲżżżļĪŻż│ż╬Š}╦ĪżŽØŖ─Ļź╔źßźżź¾Č\ĮčĪ╩Domain specific technologyĪ╦ż╚żĘżŲź│ź¾ź╗źūź╚ż¼ķWż½żņżŲżżżļĪŻĪųØŖ─Ļź╔źßźżź¾Č\Įčż“╗╚ż©żąĪó▒■├ōĄĪ▀_(d©ó)ż╦“£ż├żŲČ\Įčż“║Ū┼¼▓ĮżŪżŁĪóźčź├ź▒Ī╝źĖż╦Ų■ż├ż┐źĘź╣źŲźÓż╚żĘżŲ┼¼└┌ż╩ź│ź╣ź╚żŪ┼¼└┌ż╩└Łē”ż“─¾ČĪż╣żļĪūż╚LiuĢ■żŽĮęż┘żŲżżżļĪŻŲ▒Ģ■żŽĄ£╬Ńż╚żĘżŲĪó12Ė─ż╬źóź»źŲźŻźųż╩ź┴ź├źūż“źóź»źŲźŻźųż╩┤łź┴ź├źūż╦ĮĖ└čżĘ─Ńča(b©│)żŪź▄ź¾źŪźŻź¾ź░żĘżŲżżżļ×æēäż“Šę▓żĘż┐ĪŻĖ³żĄżŽµ£ŗżŪ600 µm░╩ŲŌż╦ż╩żļż╚żżż”ĪŻ

IO┐¶ż“╗\żĘżŲźąź¾ź╔╔²ż“╗\żõż╣

ź┴ź├źū┤ųż╬IOĪ╩Ų■Įą╬üĪ╦┐¶ż╬╗\▓├żŽĪó║ŪĮj(lu©░)źąź¾ź╔╔²ż“╗\żõżĘĪó┼Š┴„ź©ź═źļź«Ī╝ż“žō(f©┤)żķż╣ź½ź«ż╚ż╩żļĪŻĪų║ŻŲ³ż╬ź│ź¾źįźÕĪ╝źŲźŻź¾ź░źĘź╣źŲźÓżŽźąź¾ź╔╔²╔į’Bż╬öU(ku©░)╠¾ż“£pż▒żŲżżżļĪŻ║ŪŖZ┐āżĄżņż┐źŪĪ╝ź┐ż╦żĶżļż╚Īó║ŪĮj(lu©░)źąź¾ź╔╔²żŽ2ŃQżŪ1.6Ū▄ż╬ź┌Ī╝ź╣żŪ╗\ż©żŲżżżļĪŻ║ŪĮj(lu©░)ź╣źļĪ╝źūź├ź╚ż╬╗\▓├╬©żŽĪóźĒźĖź├ź»żŪ1.8Ū▄żŪżóżļĪŻżĶżĻ¾Hż»ż╬ź┐ź╣ź»ź╗ź├ź╚ż“╝┬╣įż╣żļż┐żßż╦źĘź╣źŲźÓź╣źļĪ╝źūź├ź╚ż“öU(ku©░)Ė┬żĘżŲżżżļż╬żŽ£½żķż½ż╦źąź¾ź╔╔²╔į’Bż╬ż┐żßżŪżóżļĪŻźąź¾ź╔╔²ż╚Īó├▒░╠W┼÷ż┐żĻż╬źąź¾ź╔╔²ż“╗\żõż╣ż┐żßż╦Īó║ŪżŌŃ~Ė·ż╩Š}├╩żŽIO┐¶ż“╗\żõż╣ż│ż╚ż└ĪŻīm▒┐ż╦żŌŪ█└■╠®┼┘ż“╗\żõżĘżŲIO┐¶ż“╗\żõż╣═Š├ŽżŽ¾HżżĪūż╚LiuĢ■żŽĮęż┘żŲżżżļĪŻ

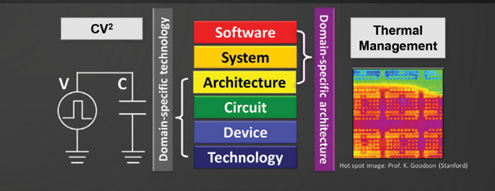

ź©ź═źļź«Ī╝Ė·╬©ż“æųż▓żļ

żżżĒżżżĒż╩Č\Įčż╬├µżŪ░ŃżżżŽżóżļżŌż╬ż╬Īóź│ź¾źįźÕĪ╝źŲźŻź¾ź░Č\Įčż╬▐kż─ż╬Č”─╠ż╬▓▌¼öżŽź©ź═źļź«Ī╝Ė·╬©żŪżóżĒż”Īóż╚LiuĢ■żŽĖ└ż”ĪŻź│ź¾źįźÕĪ╝źŲźŻź¾ź░ż╬ź©ź═źļź«Ī╝Ė·╬©Ī╩W┼÷ż┐żĻż╬ź╣źļĪ╝źūź├ź╚Ī╦żŽĪóCV2ż“žō(f©┤)żķż╣ż│ż╚ż╦żĶż├żŲ▓■║¤żĄżņżļĪŻż│ż│żŪCżŽź╚źķź¾źĖź╣ź┐ż╚Ū█└■ż╬ź╣źżź├ź┴ź¾ź░═Ų╬╠żŪVżŽ┼┼Ė╗┼┼░ĄżŪżóżļĪ╩┐▐7Ī╦ĪŻźŪźąźżź╣Č\Į迎Cż╚Vż“║ŪżŌ─Ńż»ż╣żļż│ż╚ż¼ĄßżßżķżņżļĪŻ

┐▐7ĪĪźóĪ╝źŁźŲź»ź┴źŃźņź┘źļż½żķź╚źķź¾źĖź╣ź┐źņź┘źļż▐żŪź©ź¾ź╔ź─Ī╝ź©ź¾ź╔ż╬║Ū┼¼▓Įż¼ØŁ═ūĪĪĮąųZĪ¦Semiconductor Digest

Ū█└■═Ų╬╠żŽĪó2╝ĪĖĄż╬ź╣ź▒Ī╝źĻź¾ź░ż╚3╝ĪĖĄż╬ĮĖ└č▓Įż╦żĶż├żŲżĄżķż╦▓╝ż▓żļż│ż╚ż¼żŪżŁżļĪŻ┼┼Ė╗┼┼░ĄżŽĪóź╚źķź¾źĖź╣ź┐ż╬¼ś┼┼─cż╚źŁźŃźĻźó═ó┴„ż“▓■║¤ż╣żļż│ż╚żŪ▓╝ż▓żļż│ż╚ż¼żŪżŁżļĪŻż─ż▐żĻĪ󟬟š╗■ż╬źĻĪ╝ź»┼┼╬«ż“─Ńż»╩▌ż┴ż╩ż¼żķź¬ź¾┼┼╬«ż“æųż▓żļż│ż╚ż╦┐įżŁżļĪŻ

ØŖ─Ļź╔źßźżź¾Ė■ż▒źóĪ╝źŁźŲź»ź┴źŃĪ╩Domain Specific ArchitectureĪ╦ż╚ŽóŲ░żĘżŲØŖ─Ļź╔źßźżź¾Č\Į迎Īóź│ź¾źįźÕĪ╝ź┐ż╬ź©ź═źļź«Ī╝Ė·╬©ż“żĄżķż╦┐╩▓ĮżĄż╗żļż┐żßż╬ĄĪ▓±ż╚ż╩żļĪŻź©ź═źļź«Ī╝Ė·╬©ż“▓■║¤ż╣żļż╚Č”ż╦ĪóŠÅČ╚─cżŌÕXż╬Š├õJż╦ŲDżĻ┴╚żÓØŁ═ūż¼ĮążŲż»żļĪŻĪų╚»ÕXż╬źĮźĻźÕĪ╝źĘźńź¾żŽż│żņż½żķż╬╣ŌĮĖ└čź┴ź├źūż╦Ė■ż▒żŲ│½╚»żĘż╩ż▒żņżąż╩żķż╩żżĪūż╚LiuĢ■żŽĖņż├żŲżżżļĪŻ

£½żļżż╠ż═Ķżž

Īųż│żņż▐żŪ15ŃQ░╩æųĪó╚ŠŲ│öüŠÅČ╚żŽżĶżĻ╣Ōżż└Łē”ż╚ĪóżĶżĻ╣Ōżżź©ź═źļź«Ī╝Ė·╬©ż╬ź│ź¾źįźÕĪ╝źŲźŻź¾ź░Č\Įčż“─¾ČĪżĘżŲżŁż┐ĪŻż│żņż╦żĶż├żŲ2ŃQż┤ż╚ż╦ź©ź═źļź«Ī╝Ė·╬©ż“2Ū▄ż╦æųż▓żŲżŁż┐ĪŻż│ż╬ź╚źņź¾ź╔żŽĪó║Żżõ╬╠ŠÅ├╩│¼ż╦ż╩ż├żŲżżżļ║Ū┐Ęż╬5nmČ\Įčż╦żŌż▀żķżņżļĪŻżĄżķż╦TSMCżŽ3nmź╬Ī╝ź╔ż╬│½╚»ż¼═Į─Ļ─╠żĻż╦┐╩ż¾żŪż¬żĻĪóŲ▒══ż╩└Ķ┐╩Č\Įčż“─¾ČĪż╣żļĪŻźĘź╣źŲźÓ└Łē”ż╚ź©ź═źļź«Ī╝Ė·╬©żŽĪó“£═Ķż╬╚»·tÅ]┼┘żŪ┐╩ż▀¶öż▒żļż└żĒż”ĪŻż│żņż╦żŽĪ󿥿▐żČż▐ż╩źżź╬ź┘Ī╝źĘźńź¾ż╦żĶż├żŲ╝┬ĖĮżĄżņżļż└żĒż”Ī©║Ó╬┴żõźŪźąźżź╣ĪóĮĖ└č▓ĮČ\ĮčĪóövŽ®└▀╝ŖĪóźĘź╣źŲźÓźóĪ╝źŁźŲź»ź┴źŃ└▀╝Ŗż╩ż╔żŪżóżļĪūż╚LiuĢ■żŽĮęż┘ĪóĪų╚ŠŲ│öüŠÅČ╚ż╚żŌż├ż╚╣Łżżźóź½źŪź▀ź├ź»ż╩│ž─cż¼▐kĮ’ż╦Š}ż“┴╚żÓż╚Īóż│ż╬ź╚źņź¾ź╔ż“Įø(j©®ng)═Ķż╦┼Žż├żŲż”ż▐ż»ŲDżĻ╣■żÓżĶż”ż╩Č\Įčż“│½╚»ż╣żļżĶż”ż╦ż╩żĒż”Īūż╚±Tż¾ż└ĪŻ

╗▓╣═½@╬┴

1. M. Liu, Unleashing the Future of Innovation, ISSCC 2021.

2. TSMCż╬źŲź»ź╬źĒźĖĪ╝źĒĪ╝ź╔ź▐ź├źūĪ╩1Ī╦ (2021/05/14)