TSMCż╬└Ķ├╝źčź├ź▒Ī╝źĖ╣®Šņż“Ų³╦▄żž═Č├ūż╣żļź’ź▒ż╚żŽĪ®

TSMCż¼Ęą║čŠÅČ╚Š╩ż╚ÅBżĘ╣ńżżż“Ęeż┴ĪóŲ³╦▄ż╦└Ķ├╝ICźčź├ź▒Ī╝źĖČ\Įčż╬╣®Šņ└▀╬®ż“ĖĪŲżż╣żļż╚żżż”ź╦źÕĪ╝ź╣ż¼╬«żņż┐ĪŻż╔ż”żõżķż│ż╬ź╦źÕĪ╝ź╣żŽĄ£╝┬ż╬żĶż”ż└ĪŻŲ³╦▄Ęą║č┐Ę╩╣żŽĪó1ĘŅ5Ų³ż╦ĖĮ├Ž╩¾╠Oż╚żżż”Ę┴żŪ┼┴ż©ż┐ĪŻ│╬ż½ż╦TSMCżŽCoWoSżõInFOż╚Ō}żų2.5D/3D-ICźčź├ź▒Ī╝źĖČ\Įčż“Š}²Xż▒żŲż¬żĻĪóOSATż╬ż¬│¶ż“├źż”└¬żżżŪżóżļż│ż╚żŽĄ£╝┬ż└ĪŻ

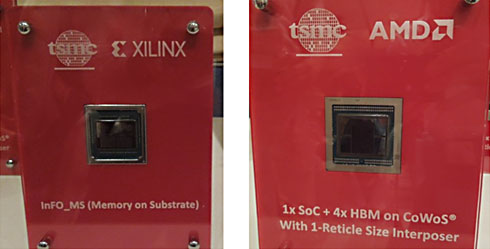

┐▐1ĪĪTSMCż¼Ęeż─InFOżõCoWoSČ\ĮčżŪ╝┬äóżĘż┐ź┴ź├źūĪĪ╔«Ūv╗Ż▒Ų

Ų³╦▄ż╦ż¬ż▒żļ┐Ę╣®ŠņżŽ┼ņ»Bż╦└▀╬®ż╣żļż╚ĖĮ├ŽżŪżŽ╩¾żĖżķżņżŲżżżļż¼Īó┼ņ»Bż╬ż╔ż│ż╦ż╩żļż╬ż½ŠņĮĻż╦ż─żżżŲżŽ┐©żņżŲżżż╩żżĪŻż│żņż▐żŪ£½żķż½ż╦ż╩ż├żŲżżżļż│ż╚żŽĪóĘą║čŠÅČ╚Š╩ż╚└▐╚ŠżŪŲ³╦▄ż╦╣ń╩█▓±╝ęż“└▀╬®ż╣żļż│ż╚ĪóØi╣®µćżŪżŽż╩ż»ĖÕ╣®µćż╬╣®ŠņżŪżóżļż│ż╚ĪŻ

ĘąŠÅŠ╩żŽ║“ŃQĪóØi╣®µćż╬═Č├ūż“TSMCż╦Ęeż┴ż½ż▒żŲżżż┐ż¼ĪóĖ½Ą£ż╦éāżķżņż┐ĪŻŲ▒Š╩żŽ║ŻŃQ┼┘żŽżĮż╬ż┐żßż╬═ĮōQż“ż╣żŪż╦╝ŖæųżĘżŲż¬żĻĪóTSMCż╬╚ŠŲ│öü╣®Šņż“▓┐ż¼▓┐żŪżŌ═Č├ūż╣żļż┐żßĪóØi╣®µćż╬źšźĪź”ź¾ź╔źĻżŪżŽż╩ż»ĪóĖÕ╣®µćż╬╣®Šņż“└▀╬®żĘżĶż”ż╚żżż”ż│ż╚ż╬żĶż”ż└ĪŻż╚ż╦ż½ż»TSMCż╬╚ŠŲ│öü╣®Šņż“Ų³╦▄ż╦Ęeż├żŲż│żņż┐ż╚ż╩żņżąĘąŠÅŠ╩ż╬źßź¾ź─żŽ╩▌ĘeżĄżņĪóTSMCż╬╚ŠŲ│öü╣®Šņż“Ų³╦▄ż╦Ęeż├żŲżŁż┐ż╚żżż”╝┬└ėż¼╗─żļż│ż╚ż╦ż╩żļĪŻ

żŪżŽĪóTSMCżŽż╩ż╝ż│ż╬ÅBż╦ŠĶż├ż┐ż╬ż½ĪŻż│ż╬ÅBż╦żŽżĄż▐żČż▐ż╩Ą£╝┬ż“└čż▀æųż▓żļØŁ═ūż¼żóżļĪŻ▐kż─żŽĪóTSMCż¼ä▌╣±źóźĻźŠź╩䔿╦5nmźūźĒź╗ź╣ż╬║Ū┐Ę▒į╣®Šņż“└▀╬®ż╣żļż│ż╚ż“»éżßĪ╩╗▓╣═½@╬┴1Ī╦Īó35▓»ź╔źļż╚żżż”½@╦▄ČŌż▐żŪŲD─∙╠“▓±żŪ»é─ĻżĘż┐ż│ż╚ż└Ī╩╗▓╣═½@╬┴2Ī╦ĪŻż│ż╬ż┐żßĪóŲ³╦▄ż╦Øi╣®µćż╬╣®Šņż“║Ņżļż╚żżż”┬ō┘IżŽŠ├ż©ż┐ĪŻ

TSMCżŽ±śŽčĒ×ŗż╬┐Ęāńż╬╦▄╝ę╣®Šņż└ż▒żŪżŽż╩ż»Īó±ś├µĪó±śŲŅż╩ż╔Īó├Ž┐╠żõźŲźĒż╩ż╔ż╬źĻź╣ź»ż╦×óż©żŲĄ£Č╚┘M¶öż╬ż┐żßĘQ├Žż╦╣®Šņż“╩¼ÜgżĄż╗żŲżżżļĪŻ±śŽč░╩│░żŪżŌ├µ╣±ż╬ŲŅ»Bż╚źĘź¾ź¼ź▌Ī╝źļż╦żŌ╣®Šņż“╔nŲ»żĄż╗żŲżżżļĪŻä▌╣±ź’źĘź¾ź╚ź¾ä”ż╦żŌ╣®Šņż“Ęeż├żŲżżżļż¼Īó200mmź”ź¦Ī╝źŽźšźĪźųżŪżóżĻĪó║“ŃQż╬źóźĻźŠź╩╣®Šņż█ż╔ż╬æä╠ŽżŪżŽż╩żżĪŻ║ŻövĪóŲ³╦▄ż╦═Č├ūż╣żļż│ż╚żŪĖÕ╣®µć╣®Šņż╬źĻź╣ź»╩¼Ügż╚żżż”ż│ż╚ż╦ż╩żĻżĮż”ż└ĪŻ

żŌż”▐kż─żŽ┼ņ»BĮj│žż╬Ęeż─║Ū└Ķ├╝MOSź╚źķź¾źĖź╣ź┐Č\ĮčżŪżóżļĪŻ2019ŃQż╦TSMCż╚┼ņĮjd.labżŽ─¾Ę╚ż“±TżėĪ╩╗▓╣═½@╬┴3Ī╦Īó┼ņĮjżŪ7nmżõ5nmż╬LSI└▀╝Ŗż“╣įżżĪóżĮż╬×æļ]ż“TSMCż╦░══ĻżŪżŁżļżĶż”ż╦ż╩ż├ż┐ĪŻ┼ņĮjŖõż╚żĘżŲżŌ║Ū└Ķ├╝źūźĒź╗ź╣żŪLSIż“└▀╝ŖżĘż┐żżż╚żżż”╗ūŽŪż¼żóżļĪŻTSMCż╚żĘżŲżŽ║ŻĖÕż╬5nmĪó3nmżžż╚╚∙║┘▓Įż¼¶öż»æųżŪźūźĒź╗ź╣ż“└▀╝Ŗż╣żļż┐żßż╦┼ņĮjż╬MOSź╚źķź¾źĖź╣ź┐Č\Įčż¼═▀żĘż½ż├ż┐ĪŻ┼ņĮjż╦żŽ╬╠╗ę╬ü│žż╬ź╚ź¾ź═źļĖ·▓╠ż“ŠW├ōżĘż┐TFETČ\Įčżõ▓Į╣ńر╚ŠŲ│öüż╚ż╬źžźŲźĒČ\ĮčżŌżóżļĪŻTSMC1╝ęż└ż▒żŪ3nmżóżļżżżŽ2nmźūźĒź╗ź╣ż“│½╚»ż╣żļżĶżĻżŽĮj│žż╬ē¶įLż“╝┌żĻżļöĄż¼│½╚»õJżŽŖWż»║čżÓĪŻSamsungż╬źšźĪź”ź¾ź╔źĻźėźĖź═ź╣ż╬╝{żżæųż▓żŌżóżļĪŻ

żĮżņż└ż▒żŪżŽż╩żżĪŻTSMCżŽż│żņż▐żŪĪóAppleżõźšźĪĪ╝ź”ź¦źżĪóQualcommż“żŽżĖżßż╚ż╣żļź╣ź▐Ī╝ź╚źšź®ź¾źėźĖź═ź╣żõAMDż╬CPUźėźĖź═ź╣ż“├µ┐┤ż╦źšźĪź”ź¾ź╔źĻźĄĪ╝źėź╣ż“╣įż├żŲżŁż┐ĪŻ║ŻĖÕżŽĪóśOŲ░▒┐┼Šżõ┼┼Ų░▓Įż“żŽżĖżßż╚ż╣żļź»źļź▐Ą£Č╚ż╬└«─╣╩¼╠Ņż╦żŌ┐╩ĮążŪżŁżļĪŻż│ż╬ŠÅČ╚żŽŲ³╦▄ż¼ź╔źżź─ż╚╩┬ż¾żŪäėżżż│ż╚ż“TSMCżŽ═²▓“żĘżŲżżżļĪŻżĄżķż╦Ų³╦▄żŽŠÅČ╚├ōźĒź▄ź├ź╚żõPLCĪ╩Programmable Logic ControllerĪ╦ĪóŠÅČ╚ĄĪ▀_żŪżŌ└ż─cż“źĻĪ╝ź╔żĘżŲżżżļĪŻż│żņż½żķżŽ║ŲÖ┌ź©ź═źļź«Ī╝öUĖµĄĪ▀_ż╦żŌ└«─╣ĄĪ▓±ż¼╗\ż©żļĪŻ╝┬żŽŲ³╦▄ż¼įu┴Tż╩╩¼╠Ņż╦ż│ż”żżż├ż┐╠ż═Ķż╬źŲź»ź╬źĒźĖĪ╝ż¼ż┐ż»żĄż¾żóżļĪóż╚ķL│░ż╬ų`ż╦żŽ▒Ūż├żŲżżżļĪŻŲ³╦▄╦Ī┐═ż╦╬üż“Ų■żņżļ│░½@ÅU┤ļČ╚ż╦żŽĪóż│ż”żżż├ż┐Ų³╦▄ż╬Č\Įčż╦ų`ż“Ė■ż▒żŲżżżļĮĻż¼¾HżżĪŻ

TSMCżŽŲ³╦▄ż╦źŪźČźżź¾ź╗ź¾ź┐Ī╝ż“│½└▀ż╣żļż┐żßż╬┐═║Ó╩ńĮĖż“└čČ╦┼¬ż╦╣įż├żŲżżżļĪŻRTLż½żķGDSż▐żŪż╬└▀╝ŖżõźßźŌźĻź│ź¾źčźżźķż╬ź©ź¾źĖź╦źóĪóźņźżźóź”ź╚ź©ź¾źĖź╦źóĪóIP│½╚»ŪvĪóØŖ└Łäh▓┴ź©ź¾źĖź╦źóĪóéb═²╣ń└«/╣Ō░╠╣ń└«ź©ź¾źĖź╦źóż╩ż╔ż“ĄßżßżŲżżżļĪŻźšźĪź”ź¾ź╔źĻźėźĖź═ź╣żŪ─_═ūż╩ż│ż╚żŽĪó└▀╝Ŗ└ņ╠ńż╬źŪźČźżź¾ź╗ź¾ź┐Ī╝ż“Ęeż─ż│ż╚ż└ĪŻżĄżŌż╩ż▒żņżąĖ▄ĄężŽ═Ķż╩żżż½żķż└ĪŻśOØiż╬╚ŠŲ│öüż“═▀żĘżżIT┤ļČ╚żŽ¾HżżĪŻżĘż½żĘLSI└▀╝ŖżŽžMżĘżżæųż╦┬Šż╦▒■├ōż¼ŠWż½ż╩żżż½żķ└čČ╦┼¬ż╦żõżĻż┐ż»ż╩żżĪŻźūźĒź░źķź▀ź¾ź░ż½żķRTLĮą╬üĪóźūźĒź░źķźÓĖĪŠ┌Īóéb═²╣ń└«Īóź═ź├ź╚źĻź╣ź╚Įą╬üĪóźņźżźóź”ź╚ĪóŪ█ÅøŪ█└■ĪóżĮżĘżŲź▐ź╣ź»Įą╬üĪóż╚żżż”└▀╝Ŗ╣®µćż“▐kż½żķ│žżų▓╦ż¼żóżļż╩żķĪóAIż╬źóźļź┤źĻź║źÓżõ┐ʿʿżźĮźšź╚ź”ź©źóż╬│½╚»ż“żĘżŲżżż┐żżĪŻż└ż½żķż│żĮĪóLSI└▀╝Ŗ└ņ╠ńż╬źŪźČźżź¾źŽź”ź╣ż¼’Lż½ż╗ż╩żżż╬żŪżóżļĪŻŲ³╦▄żŪźšźĪź”ź¾ź╔źĻż╚Š╬żĘżŲżżżļ×æļ]╣®ŠņżŽĪó└▀╝Ŗē”╬üż¼ż╩żżż╦żŌż½ż½ż’żķż║źŪźČźżź¾źŽź”ź╣ż╚Š}ż“┴╚ż¾żŪżżż╩żżż┐żßĪóżżż─ż▐żŪż┐ż├żŲżŌĖ▄ĄężŽż│ż╩żżĪŻ

ż│żņż½żķż╬LSIĪóØŖż╦SoCżŽĪóCPUż╚GPUżõDSPĪóISPż╩ż╔źžźŲźĒźūźĒź╗ź├źĄż╚ż╬ĮĖ└čż╚ĪóSiż╦▓Į╣ńر╚ŠŲ│öüż“ĮĖ└čż╣żļČ\Įčż¼─_═ūż╦ż╩żļĪ╩╗▓╣═½@╬┴4Ī╦ĪŻźžźŲźĒźūźĒź╗ź├źĄżŽRISC-VżŪ╠┐╬ßź╗ź├ź╚ż“┼²▐kż╣żļŲ░żŁż“ŠW├ōż╣żļż╚żĘżŲĪ╩╗▓╣═½@╬┴5Ī╦ĪóSiż╚▓Į╣ńر╚ŠŲ│öüż╬ż╚ż╬źžźŲźĒĮĖ└čČ\Į迎Īó╝┬żŽŲ³╦▄ż¼ż▐ż└äėżżĪŻ

2╝ĪĖĄ╩┐ĀCæųż╦ź╚źķź¾źĖź╣ź┐ż“¾Hż»ĮĖ└čż╣żļźÓĪ╝źóż╬╦Īō¦żŽ╣įżŁĄ═ż├żŲżŁż┐ż┐żßĪó5nmż½żķ3nmĪó2nmżžż╬╚∙║┘▓ĮżŽ┐╩żßżļ▐köĄżŪĪó╠Ą═²ż╩ż»×æļ]ż╣żļż┐żßż╬ź┴ź├źūźņź├ź╚Ī╩Š«żĄżżź┴ź├źūżõIPż“ź┴ź├źū▓ĮżĘż┐żŌż╬Ī╦ż“Siźżź¾ź┐Ī╝ź▌Ī╝źČż╩ż╔ż╦ĮĖ└čż╣żļŲ░żŁżŌĖ½Ų©ż╗ż╩żżĪŻ└Ķ├╝źčź├ź▒Ī╝źĖČ\Į迎ĪóIntelż¼╗Žżßż┐ź┴ź├źūźņź├ź╚╝┬äóĪ╩╗▓╣═½@╬┴6Ī╦żŌżĮż╬▐kż─żŪżóżļĪŻż│ż│ż╦2.5Dżõ3Dż╬ICżŌĮĖ└čż╣żļĪŻ

TSMCżŽź│ź╣ź╚┼¬ż╦└▐żĻ╣ńżżż“¤²ż▒ż╩ż¼żķ3╝ĪĖĄ╝┬äóż“ų`╗žż╣Č\ĮčĪóInFOĪ╩Integrated Fan-OutĪ╦żõCoWoSĪ╩Chip-on-Wafer-on-SubstrateĪ╦Č\Įčż╦╬üż“Ų■żņżŲżŁż┐ĪŻż│ż╬└Ķ├╝źčź├ź▒Ī╝źĖżŽWLPĪ╩ź”ź¦Ī╝źŽźņź┘źļźčź├ź▒Ī╝źĖĪ╦żõ╝┬äóżĘż┐źčź├ź▒Ī╝źĖż¼ź┴ź├źūż╚Ų▒µć┼┘ż½żõżõĮjżŁżżµć┼┘ż╬«ĆŠ«Ę┐źčź├ź▒Ī╝źĖżŪżóżļĪŻ║ŪŖZżŪżŽ3╝ĪĖĄ╝┬äóż╬SoICČ\ĮčĪ╩┐▐2Ī╦żŌ│½╚»żĘżŲżżżļĪŻ

┐▐2ĪĪTSMCż╬3╝ĪĖĄICżŪżóżļTSMC-SoICČ\ĮčĪĪĮąųZĪ¦TSMC

ź”ź¦Ī╝źŽż“ź┴ź├źūż╦ź½ź├ź╚ż╣żļØiż╦ź”ź¦Ī╝źŽżžż╬źąź¾źūĘ┴└«żõźŌĪ╝źļźŪźŻź¾ź░ż╩ż╔żŪ▓├╣®ż╣żļż┐żßĪóØi╣®µć×æļ]æą╔ķż╬TSMCż¼Š}²Xż▒żŲżżżļż¼ĪóOSATź╚ź├źūż╬±śŽčASEżŌŲ▒══ż╩└Ķ├╝źčź├ź▒Ī╝źĖż“Š}²Xż▒żŲżżżļĪŻż─ż▐żĻĒö┴Ķż¼Ś„żĘż»ż╩żĻż─ż─żóżļĪŻ

żĄżķż╦ĪóŲ³╦▄ż╦żŽ┐ĘĖ„┼┼Ąż╣®Č╚żõźżźėźŪź¾ż╩ż╔ż╬└Ķ├╝źčź├ź▒Ī╝źĖČ\Įčż“░Ęż”▓±╝ęż¼żóżļĪŻ├▒ż╩żļĖÕ╣®µćż╬OSATżŪżŽż╩żżĪŻ▓├ż©żŲĪóĖÕ╣®µćż╬×æļ]äóÅøŠÅČ╚żŪżŽĪ󟔟¦Ī╝źŽż╬└┌éāż“╣įż”źŪźŻź╣ź│żõ┼ņ»B╗@╠®╣®Č╚ĪóźŌĪ╝źļźŪźŻź¾ź░ż╬źóźįź├ź»źõź▐ź└ż╚ź▄ź¾ź└Ī╝ż╬┐Ę└Ņż“╗▒▓╝ż╦█Eżßż┐źõź▐źŽ╚»Ų░ĄĪż╬╗ę▓±╝ęźõź▐źŽźŌĪ╝ź┐Ī╝źĒź▄źŲźŻź»ź╣ź█Ī╝źļźŪźŻź¾ź░ź╣ĪóźŌĪ╝źļźŪźŻź¾ź░ż╦äėżżTOWAż╩ż╔ż╬äóÅøźßĪ╝ź½Ī╝żŌżóżļĪŻTSMCż╦ż╚ż├żŲżŽäóÅøŠÅČ╚żžż╬źĄźūźķźżź┴ź¦Ī╝ź¾ż“ŠW├ōżĘżõż╣ż»ż╩żļż╚żżż”źßźĻź├ź╚żŌżóżļĪŻ

Ų³╦▄ż╦═Č├ūż╣żļ└Ķ├╝źčź├ź▒Ī╝źĖ╣®ŠņżŽĪóż│ż”żżż├ż┐InFOżõCoWoSČ\ĮčĪó3D-ICż“╗╚ż”╣®Šņż╚ż╩żļż└żĒż”ĪŻ║ŻżõĖÕ╣®µćĪßęÆżņż┐Č\ĮčĪóż╚żżż”┐▐╝░żŽ└«żĻ╬®ż┐ż╩ż»ż╩żĻż─ż─żóżļĪŻ

╗▓╣═½@╬┴

1. TSMCż╬ä▌╣±└Ķ├╝╣®Šņ└▀╬®ż╬ŪžĘ╩ż╦▓┌░┘ż─żųżĘ (2020/05/18)

2. Appleż¼Macż╬CPUż“Intelż½żķŲ╚śOż╦╩čż©ż┐ż╬żŽź╣ź▒Ī╝źķźėźĻźŲźŻ (2020/11/16)

3. ┼ņĮjż╚TSMCż¼╩±│ń─¾Ę╚Īó3nm░╩▓╝ż╬LSI╝┬ĖĮż╦Ė■ż▒ż┐╣±║▌Č©╬üżž (2019/11/28)

4. ISSMżŪźžźŲźĒ╚ŠŲ│öüČ\Įčż╬öĄĖ■ż“┐ā║ȿʿ┐└ż─cż╬ébĄęNicky LuĢ■ (2020/12/18)

5. ╚ŠŲ│öüźūźĒź╗ź├źĄźßĪ╝ź½Ī╝ż¼ĮĖ±TżĘż┐╗š┴÷(IoT/ź╗źŁźÕźĻźŲźŻįć) (2017/12/22)

6. VLSI Sympo╩¾╣Ī¦Intelż╬Mayberry CTOĪóź│ź¾źįźÕĪ╝ź┐ź╚źņź¾ź╔ż“Ėņżļ (2020/06/19)