IntelĪóFPGAż“ź│ź¾źįźÕĪ╝ź┐ż╬╣ŌÅ]▓Į└ņ├ōż╦╗╚żżżõż╣żżź½Ī╝ź╔żŪ╝┬ĖĮ

IntelżŽ2ŃQØiAlteraż“āA╝²żĘĪóFPGAźėźĖź═ź╣ż“Š}ż╦Ų■żņż┐ż¼ĪóFPGAż“ż│żņż▐żŪ░╩æųż╦╗╚żżżõż╣ż»ż╣żļż┐żßĪóFPGAż“┼ļ║▄żĘż┐ź│ź¾źįźÕĪ╝ź┐źĘź╣źŲźÓż╬źóź»ź╗źķźņĪ╝ź┐└ņ├ōż╬ź½Ī╝ź╔(┐▐1)ż“Dell EMCż╚╔┘╗╬─╠ż╚żżż”╝ń═ūOEMż╦Įą▓┘żĘżŲżżżļż│ż╚ż“£½żķż½ż╦żĘż┐ĪŻPCIeźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż╬ż│ż╬ź½Ī╝ź╔ż╩żķ├»żŪżŌź│ź¾źįźÕĪ╝ź┐ż“į~├▒ż╦╣ŌÅ]▓ĮżŪżŁżļżĶż”ż╦ż╩żļĪŻ

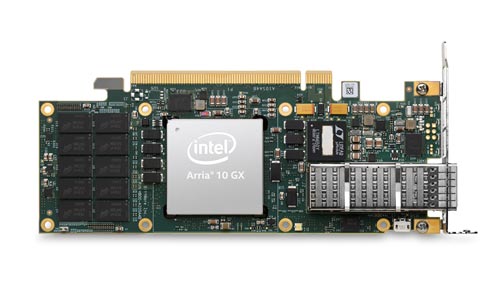

┐▐1ĪĪIntelż╬FPGAż“╗╚ż├ż┐PCIeźóź»ź╗źķźņĪ╝ź┐ź½Ī╝ź╔

PCIeż╦║╣żĘ╣■żÓż└ż▒żŪź│ź¾źįźÕĪ╝ź┐ż“╣ŌÅ]ż╦ż╣żļż│ż╬FPGAź½Ī╝ź╔żŽPACĪ╩Programmable Acceleration CardĪ╦ź½Ī╝ź╔ż╚Ō}żążņĪóźŪĪ╝ź┐▓“└ŽżõAIĪ╩┐═╣®ē¶ē”Ī╦ĪóŲ░▓Ķż╬ź╚źķź¾ź╣ź│Ī╝źŪźŻź¾ź░Ī╩░█ż╩żļ░ĄĮ╠źšź®Ī╝ź▐ź├ź╚żž╩č┤╣ż╣żļż│ż╚Ī╦Ī󟥟żźąĪ╝ź╗źŁźÕźĻźŲźŻĪó║Ōē»╩¼└ŽĪ”▓─£å▓ĮĪóź▓ź╬źÓ▓“└Žż╩ż╔Īó╣ŌÅ]▓Įż¼ØŁ═ūż╩╩¼╠Ņż╦╗╚ż©żļź½Ī╝ź╔ż╚ż╩żļĪŻż│żņż▐żŪżŽĪóźĄĪ╝źąż“╣ŌÅ]▓Įż╣żļż┐żßż╦FPGAż“╗╚ż”ż╚Ė└ż├żŲżŌĪóFPGAżžż╬źūźĒź░źķź▀ź¾ź░żĮż╬żŌż╬ż╦°BŃ^ż¼żóż├ż┐ĪŻ

FPGAżŽĪóĮ±żŁ┤╣ż©▓─ē”ż╩éb═²övŽ®żŪżóżļż¼ĪóźūźĒź░źķźÓĖ└ĖņżŽVHDLżŪĮ±ż½ż╩ż▒żņżąż╩żķż╩żżż│ż╚ż¼¾Hż»Īó▐k╚╠┼¬ż╩C/C++Ė└Ėņż╩ż╔żŪżŽĮ±żżżŲżŌ╩č┤╣ż╣żļż┐żßż╬ź│ź¾źčźżźķż¼ØŁ═ūĪŻźūźĒź░źķźÓżĘżõż╣żżSDKĪ╩źĮźšź╚ź”ź©źó│½╚»źŁź├ź╚Ī╦żŽ’Lż½ż╗ż╩żżĪŻ

żĄżķż╦ż│ż╬FPGAżŽźóź»ź╗źķźņĪ╝ź┐ż╚żĘżŲ╗╚ż’żņżļż│ż╚ż“Øi─¾ż╚żĘżŲż¬żĻĪóCPUż╚▐kĮ’ż╦╗╚ż’żņżļĪŻż│ż╬ż┐żßĪóźóź»ź╗źķźņĪ╝źĘźńź¾źķźżźųźķźĻĪ╝ż“├ō┴TżĘĪ󿥿ķż╦APIż╦┴Ļ┼÷ż╣żļOPAEĪ╩Open Programmable Acceleration EngineĪ╦żŌ├ō┴TżĘż┐ĪŻż│ż╬źĮźšź╚ź”ź©źó│½╚»źĘź╣źŲźÓżŽź│Ī╝ź╔ż╬║ŲŠW(w©Żng)├ōż¼▓─ē”ż╦ż╩ż├żŲż¬żĻĪó│½╚»ŪvČ”─╠ż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“ŠW(w©Żng)├ōż╣żļĪŻż│ż╬ż┐żßĪóźµĪ╝źČĪ╝żŽ╝ŖōQźĘź╣źŲźÓż╬╣ŌÅ]▓ĮĄĪē”ż╦ĮĖ├µż╣żļż│ż╚ż¼żŪżŁżļĪŻźĄĪ╝źążõHPCĪ╩High Performance ComputingĪ╦ż╬żĶż”ż╦╣ŌÅ]▒ķōQż“╝ń╬üż╚ż╣żļź│ź¾źįźÕĪ╝ź┐źĘź╣źŲźÓż╦Ė■ż»ĪŻ

╗╚├ō╬Ńż╚żĘżŲĪó║Ōē»źĻź╣ź»╩¼└Žżõ│¶▓┴╩čŲ░ż╬═Į▒Rż╩ż╔ČŌ═╗▌xŠņż╚ĪóźŪĪ╝ź┐ź┘Ī╝ź╣ż╬źóź»ź╗źķźņĪ╝źĘźńź¾ż“Ą¾ż▓ż┐ĪŻČŌ═╗▌xŠņżŪżŽĪó│¶▓┴ż╬═Į▒Rż╦┤žż╣żļźóźļź┤źĻź║źÓżŽ┐╩▓Įż¼ØÖŠ’ż╦Å]ż»ĪóFPGAżŪ┐╩▓ĮżĘż┐źóźļź┤źĻź║źÓż“╝┬äóżĘż┐żżĪŻż│ż╬FPGAźóź»ź╗źķźņĪ╝źĘźńź¾ż╦żĶżļź¬źūźĘźńź¾ŲD░·ż╬źĘź▀źÕźņĪ╝źĘźńź¾╗■┤ųż“╚ŠžōżŪżŁż┐ż╚żĘżŲżżżļĪŻ

ż▐ż┐ĪóźŪĪ╝ź┐ź┘Ī╝ź╣ż╬źóź»ź╗źķźņĪ╝źĘźńź¾żŪżŽĪóź╚źķź¾źČź»źĘźńź¾ż╬źŪĪ╝ź┐ź┘Ī╝ź╣ż╚╩¼└Ž├ōż╬źŪĪ╝ź┐ź┘Ī╝ź╣ż╬źŽźżźųźĻź├ź╔╣Į└«żŪżŽĪóźĻźóźļź┐źżźÓ╩¼└Žż╬ŠŃ│▓ż╦ż╩ż├żŲżżż┐ĪŻżĮż│żŪĪó▒┐├ōźŪĪ╝ź┐ź┘Ī╝ź╣ż“╩¼└ŽźŪĪ╝ź┐ź”ź¦źóźŽź”ź╣ż╦┼Š┴„ż╣żļŠņ╣ńż╦żŽĪó├ĻĮąĪ”╩č┤╣Ī”Ų╔ż▀╣■ż▀ż╚żżż├ż┐▒ķōQż¼ØŁ═ūżŪĪóż│ż│ż╦FPGAż“├ōżżżŲ╣ŌÅ]▓Įż╣żļĪŻżĮż╬±T▓╠ż“╩¼└ŽźŪĪ╝ź┐ź”ź¦źóźŽź”ź╣ż½żķźėźĖź═ź╣╩¼└Žż╣żļŠņ╣ńż╦żŌ╗■┤ųż¼ż½ż½żļż┐żßĪóźĻźóźļź┐źżźÓ╩¼└Žż╦FPGAż“ŠW(w©Żng)├ōż╣żļĪŻż│żņż╦żĶż├żŲĪóźŪĪ╝ź┐ź”ź¦źóźŽź”ź╣żžż╬╩č┤╣ż╣żļŠņ╣ńż╬źŪĪ╝ź┐├ĻĮąż╦1.5Ū▄░╩æų╣ŌÅ]▓ĮżŪżŁĪóź╣ź╚źņĪ╝źĖżŪż╬░ĄĮ╠ż╦3Ū▄╣ŌÅ]▓ĮĪóźĻźóźļź┐źżźÓźŪĪ╝ź┐╩¼└ŽżŽźóźļź┤źĻź║źÓż╬▓■╬╔żŪ20Ū▄ż╬╣ŌÅ]▓Įż¼┐▐żļż│ż╚ż¼żŪżŁż┐ż╚żĘżŲżżżļĪŻ

ż│ż╬PACź½Ī╝ź╔żŽĪó╗╚żż┤Ężņż┐źĮźšź╚ź”ź©źó│½╚»┤─ČŁ▓╝żŪĪó¾H├ō²ŗż╦źŽĪ╝ź╔ź”ź©źóż╬└Łē”ż“?q©▒)Ö├ōż╣żļż│ż╚ż¼żŪżŁżļż╚żżż”źßźĻź├ź╚ż¼żóżļĪŻż▐ż┐Īóźżź¾ź┐Ī╝źšź¦Ī╝ź╣ż¼PCIeżŪ│╚─ź└Łż¼żóżĻĪóźĘź╣źŲźÓż“żĄżķż╦╣ŌÅ]▓ĮżĘż┐żżŠņ╣ńż╦żŽź½Ī╝ź╔ż“żĄżķż╦└▄¶öżŪżŁżļĪŻ

(2018/04/17)