GaNż╬╩Ōé╬ż▐żĻ90%żõĪó┬č░Ą1200Vż╬āeĘ┐╣Įļ]ż╩ż╔┐ĘGaNźčź’Ī╝FET

GaNż╬╩Ōé╬ż▐żĻż“90%ż╦æųż▓żķżņżļ▓─ē”└Łż╬żóżļ└▀╝ŖŠ}╦ĪĪóGaNż╬┬č░Ąż“1200Vż▐żŪæųż▓żŲżŌź¬ź¾°BŃ^ż¼1.8m”Ėcm2ż╚SiC╩┬ż▀ż╦ŖZż┼ż▒żļż│ż╚ż╬żŪżŁżļMOSFETż╩ż╔ż¼╗Ņ║ŅżĄżņĪóGaNźŪźąźżź╣ż╬Š’╝▒ż¼╩čż’żĻż─ż─żóżļĪŻ╗h±äĖ®╦ļ─źźßź├ź╗żŪ│½╠¢żĄżņż┐źŲź»ź╬źšźĒź¾źŲźŻźó2015żŪżŽĪó┐ʿʿżźčź’Ī╝╚ŠŲ│öüGaNż╦ĮjżŁż╩┐╩╩Ōż¼ż▀żķżņż┐ĪŻ

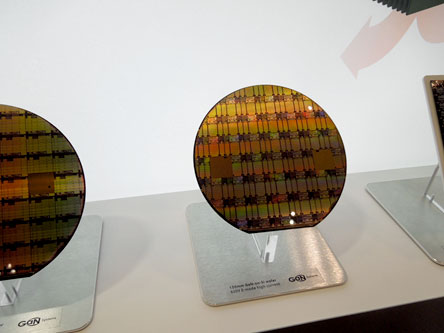

┐▐1ĪĪ6źżź¾ź┴GaN-on-SiżŪ║Ņ×æżĘż┐GaN Systemsż╬GaN FET

GaNż╬’L┤┘żŽĪó▓╝ż¼ż├żŲżŁż┐ż╚żŽżżż©Īóż▐ż└¾HżżĪŻ┼Š░╠╠®┼┘żŪ├▒░╠ĀC└č┼÷ż┐żĻ10ż╬6ŠĶcm-2żŌżóżĻĪóSiCż╚╚µż┘żļż╚3ź▒ź┐¾Hżżż╚żżż”ĪŻż│ż╬ż┐żßźŪźąźżź╣ż╬╩Ōé╬ż▐żĻżŽ─Ńż»Īó▌xŠņż╦Įąż╣ż┐żßż╦żŽ▓┴│╩ż¼╣Ō┘Vż▐żĻż╦ż╩ż├żŲżżżļĪŻ╔ߥ┌ż╣żļż┐żßż╦żŽż▐ż└╗■┤ųż¼ż½ż½żļĪŻż│ż”żżż├ż┐’L┼└ż“▓“Š├ż╣żļż┐żßż╬Č\Įč│½╚»ż¼┴Ļ╝ĪżżżŪżżżļĪŻ

║┘ż½żżź╗źļöĄ╝░żŪ╩Ōé╬ż▐żĻż“æųż▓żļ

ź½ź╩ź└ż╬GaN Systems╝ęż¼Īó6źżź¾ź┴ż╬Siź”ź¦Ī╝źŽæųż╦Ę┴└«żĘż┐GaNźčź’Ī╝ź╚źķź¾źĖź╣ź┐ż╬╩Ōé╬ż▐żĻż“æųż▓żļż┐żßż╬źµź╦Ī╝ź»ż╩źŪźČźżź¾Š}╦ĪżŽĪóĪųźóźżźķź¾ź╔Č\ĮčĪ╩Island TechnologyĪ╦Īūż╚Ō}żążņżŲżżżļĪŻż│żņżŽĪóGaNź©ź¾źŽź¾ź╣źßź¾ź╚Ę┐MOSźčź’Ī╝ź╚źķź¾źĖź╣ź┐ż“Š«żĄż╩Š«┐«ęÄź╚źķź¾źĖź╣ź┐ż╦╩¼│õżĘĪóżĮżņżķż“ż─ż╩ż«╣ńż’ż╗ż┐╣Įļ]ż“Ęeż─ĪŻĖĄĪ╣źčź’Ī╝ź╚źķź¾źĖź╣ź┐ż╬┼∙▓┴övŽ®żŽĪóŠ«┐«ęÄź╚źķź¾źĖź╣ź┐ż“¾H┐¶╩┬š`└▄¶öżĘż┐żŌż╬ż╚ż▀ż╩ż╣ż│ż╚ż¼żŪżŁżļĪŻ

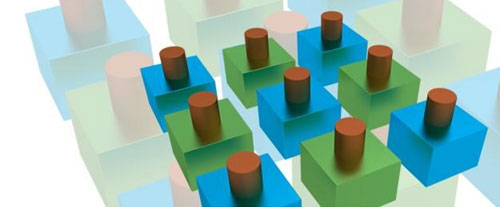

└▄¶öż╬╗┼öĄż╦╣®╔ūż¼żóżĻĪó┐▐2ż╬żĶż”ż╦Š«żĄż╩MOSź╚źķź¾źĖź╣ź┐ż╬źĮĪ╝ź╣┼┼Č╦ż“╔Įż╦ĮążĘż┐ź╗źļ(£u┐¦)ż╚Īóź╔źņźżź¾┼┼Č╦ż“╔Įż╦ĮążĘż┐×Eżżź╗źļż“Ė“Ė▀ż╦╩┬ż┘ĪóĀ¢Ę┐╣Įļ]żŪź╔źņźżź¾ĪóźĮĪ╝ź╣Ū█└■ż“ż─ż╩żżżŪżżż»ĪŻź▓Ī╝ź╚żŽ╩╠ż╬├╝╗ęż╚żĘżŲ╔ĮĀCż½żķŲDżĻĮąż╣ż╚żżż”ĪŻż┐ż╚ż©Īóź╗źļż╬▐kż─ż¼Ė╬ŠŃżĘżŲżżżļż╚żĘżŲżŌź╔źņźżź¾ż▐ż┐żŽźĮĪ╝ź╣ż╬Ū█└■ż╚żĘżŲ└▄¶öżĄżņżŲżżżļż┐żßĪó┼┼╬«ż¼Š»żĘžōŠ»ż╣żļż└ż▒żŪ╔į╬╔ż╦żŽż╩żķż╩żżĪŻż│ż╬ż┐żßĪó╩Ōé╬ż▐żĻż¼90%ż»żķżżż╦ż╩żļż╚żżż”ĪŻ“£═Ķż╬GaNź╚źķź¾źĖź╣ź┐ż╩żķ┐¶%żĘż½╩Ōé╬ż▐żĻżŽż╩ż»Īó╣Ōź│ź╣ź╚ż╚ż╩ż├żŲżżżļĪŻ

┐▐2ĪĪźóźżźķź¾ź╔ż╬ź╗źļż┤ż╚ż╦ź╔źņźżź¾ż½źĮĪ╝ź╣ż╬┼┼Č╦ż¼╔Įż╦ĮążŲż¬żĻĪóżĮżņż“ż─ż╩ż▓żŲŪ█└■┼┼Č╦ż╚ż╣żļĪĪĮąųZĪ¦GaN Systems

źčź├ź▒Ī╝źĖź¾ź░żŌźµź╦Ī╝ź»żŪĪóź▄ź¾źŪźŻź¾ź░ź’źżźõĪ╝ż“µ£ż»╗╚ż’ż║Īó╣Łżż╔²ż╬ź╔źņźżź¾ĪóźĮĪ╝ź╣ż╬Ų╝Ū█└■ż╦─Š└▄ÕX░ĄŠÆż╣żļż┐żßĪó┤¾Ö┌źżź¾ź└ź»ź┐ź¾ź╣ż¼Š«żĄż»Īó╣ŌÅ]▒■┼·ż¼▓─ē”ż╦ż╩żļż└ż▒żŪżŽż╩ż»ĪóÕX°BŃ^żŌŠ«żĄż»żŪżŁżļĪŻż┴ż╩ż▀ż╦dV/dtżŽ100V/nsż╚Č╦żßżŲźĘźŃĪ╝źūż╩╬®ż┴æųż¼żĻØŖ└Łż“Ęeż─ĪŻ┬č░ĄżŽ100Vż╚650VĪó┼┼╬«═Ų╬╠żŽ8A~250Aż▐żŪ┬Ęż©żŲżżżļĪŻ

šl┼─╣ń└«żŽāeĘ┐żŪ1200V╝┬ĖĮ

GaNż╬±TŠĮ’L┤┘ż¼SiCżĶżĻżŌ¾Hżżż│ż╚żŽĄ£╝┬ż└ż¼Īóšl┼─╣ń└«ż╦żĶżļż╚Īó’L┤┘ż¼¾Hż»żŲżŌSiCżĶżĻżŽŲ░║ŅżĘżõż╣żżż╚żżż”ĪŻšl┼─╣ń└«żŽĪóż▐ż└2źżź¾ź┴ż└ż¼GaNż“┤ł±TŠĮż╚ż╣żļMOSFETż“╗Ņ║ŅżĘż┐ĪŻź╔źņźżź¾-źĮĪ╝ź╣┤ųż╦±TŠĮ’L┤┘ż¼100Ė─µć┼┘╣ńż├żŲżŌMOSŲ░║Ņż“╣įż”ż╚żżż”ĪŻŲ▒╝꿎Īóź▓Ī╝ź╚¤©▓Į╦ņż╚żĘżŲALDż╩ż╔ż╬Ū÷╦ņ└«─╣żŪ║Ņż├ż┐āeĘ┐MOSFET(┐▐3)żŪĪó┬č░Ą1200Vż“įużŲżżżļĪŻ└§żżź╚źņź¾ź┴ż└ż¼ĪóGaNż╬FETż““£═Ķż╬▓ŻĘ┐żŪżŽż╩ż»ĪóSiCż╚Ų▒══ĪóāeĘ┐ż╦╗Ņ║ŅżĘż┐ż┐żßĪó┬č░Ąż“ĮjżŁż»ż╚żļż│ż╚ż¼żŪżŁż┐ĪŻ

┐▐3ĪĪšl┼─╣ń└«ż¼│½╚»żĘż┐āeĘ┐GaN MOSFET └§żżź╚źņź¾ź┴ż“ŠW├ōĪĪĮąųZĪ¦šl┼─╣ń└«

ż│żņż▐żŪĪóSiCżŽ 1200V░╩æųĪó600Vż▐żŪżŽGaNż╚żżż”░┼╠█ż╬ČĶ╩¼ż▒ż¼żóż├ż┐ż¼Īó“£═Ķż╬SiCżŽāeĘ┐ĪóGaNżŽ▓ŻĘ┐żŪżóż├ż┐ż┐żßż╦GaNż╦ż¬żżżŲØ▓╩¼ż╩┬č░Ąż“│╬╩▌żĘżĶż”ż╚ż╣żļż╚ź¬ź¾°BŃ^ż“ĄŠ└Ęż╦ż╗żČżļż“įuż╩ż½ż├ż┐ĪŻ║ŻövĪóšl┼─╣ń└«żŽĪóGaNż╬źąźļź»±TŠĮż“║ŅżĻĪóżĮż╬æųż╦āeöĄĖ■ż╦┼┼╬«ż“╬«ż╣╣Įļ]ż╬ź╚źķź¾źĖź╣ź┐ż“║ŅżĻ╣■żÓż│ż╚żŪĪ󟬟¾°BŃ^ż“▓╝ż▓ż┐ėX▌åżŪ┬č░Ąż“1200Vż╦æųż▓żļż│ż╚ż¼żŪżŁżļżĶż”ż╦ż╩ż├ż┐ĪŻ┐▐4ż╦żŽ1200Vż“«Ćż©żļ┬č░Ąż“┐āżĘżŲżżżļĪŻż│ż╬╗■ż╬ź¬ź¾°BŃ^żŽ1.8m”Ėcm2ż╚SiC╩┬ż▀ż╬Š«żĄżĄżŪżóżļĪŻų`║YżŽ0.4m”Ėcm2ĪŻ

┐▐4ĪĪ1200Vż╬┬č░ĄżŪź¬ź¾°BŃ^1.8m”Ėcm2ż╚─ŃżżāeĘ┐GaN MOSFETĪĪĮąųZĪ¦šl┼─╣ń└«

GaN┤łż╬±TŠĮ└«─╣ż╦żŽĪóNa═Žķ]├µżŪGaN¹|±TŠĮż“ĖĄż╦GaNż“└«─╣żĄż╗żŲżżż»öĄ╦Īż“║╬ż├ż┐ĪŻGaNżŽSiCżĶżĻżŌźąź¾ź╔ź«źŃź├źūż¼╣Łż»Īó└õ▒’┬č░ĄżŌĖČ═²┼¬ż╦ĮjżŁżżĪŻż│ż╬ż┐żß═²éb┼¬ż╦żŽSiCż╬═²ébĖ┬─cżĶżĻżŌGaNż╬żĮżņż╬öĄż¼żĄżķż╦Ė┬─cż¼╣ŁżżĪŻ