TSVż╬Š”ēä▓Įż“┴ßżßżļ╩┐ĀCŪ█ÅøŠ}╦Īż╦żĶżĻFPGAż╬ĮĖ└č┼┘ż“æųż▓żļźČźżźĻź¾ź»ź╣

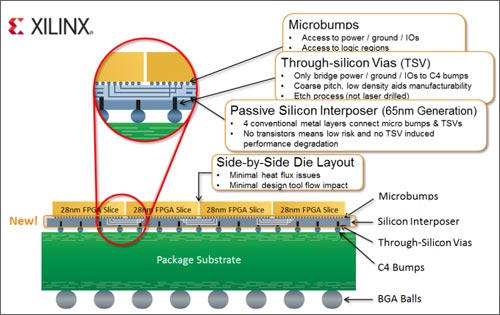

ä▌źČźżźĻź¾ź»ź╣╝꿎ĪóźĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČČ\Įčż“╗╚żżĪóFPGAź┴ź├źūż“╩Ż┐¶ż─ż╩ż░┐ʿʿż╣ŌĮĖ└č▓ĮČ\Įčż“│½╚»żĘż┐ż╚╚»╔ĮżĘż┐ĪŻ3D IC├ōż╬Č\ĮčżŪżóżļTSVĪ╩through silicon viaĪ╦ż“╗╚żżż╩ż¼żķ3╝ĪĖĄż╦ź┴ź├źūż“└čż▀─_ż═żļż╬żŪżŽż╩ż»Īó2╝ĪĖĄż╦Ū█Åøż╣żļĪŻāeż╦└čżÓż╚TSVź█Ī╝źļż╬Ū█Åøż╬öUĖ┬żõźżź¾ź┐Ī╝ź▌Ī╝źČż╦ż¬ż▒żļŪ█└■└▀╝Ŗż╬śOĮy┼┘ż¼Ąōż╩ż’żņżļż┐żßĪóĖĮ├╩│¼żŪżŽ▐kŗż╬źżźßźĖźŃĪ╝ż“Į³żżżŲ×æēä▓ĮżĄżņżŲżżż╩żżĪŻ

┐▐1ĪĪTSVż╚źĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČż“╗╚żż3D ICż╬Š”ēä▓Įżžŗī▐k╩Ōż“Ų¦ż▀Įąż╣

źČźżźĻź¾ź»ź╣ż¼ż│ż╬Č\Įčż“╚»╔ĮżĘż┐ŠņĮĻżŽ±śŽčżŪżóżļĪŻ±śŽčż╦żŽASEż╚żżż”ĖÕ╣®µćźšźĪź”ź¾ź╔źĻ└ż─cź╩ź¾źąĪ╝ź’ź¾ż╬┤ļČ╚ż¼żóżĻĪóØi╣®µćź╩ź¾źąĪ╝ź’ź¾ż╬TSMCżŌżóżļĪŻTSVČ\Į迎Øi╣®µćĪóĖÕ╣®µćż╬ż╔ż┴żķŖõżŪżŌżŪżŁżļźūźĒź╗ź╣żŪżóżļĪŻżĮżņżŠżņż╬└ņČ╚źßĪ╝ź½Ī╝ż¼±śŽčż╦żóżļż│ż╚żŽĪóźµĪ╝źČĪ╝ż½żķĖ½żļż╚╝┬ż╦źėźĖź═ź╣ż╬żõżĻżõż╣żż├Ž░Ķż╚ż╩żĻĪó±śŽčż¼3D ICż╬Ą“┼└ż╦żšżĄż’żĘżżĄ“┼└ż╚ż╩żĻż”żļĪŻ

ż│ż╬Č\Į迎ĪóFPGAż╬ĮĖ└č┼┘ż“źÓĪ╝źóż╬╦Īō¦ż╚Č”ż╦żĄżķż╦æųż▓żĶż”ż╚ż╣żļż╚żŁż╦╗╚ż”Č\ĮčżŪżóżļĪŻFPGAżŽ║ŪĮ¬×æēäż╦╗╚ż”ż│ż╚żŽĄ®żŪĪóż┐żżżŲżżż╬Šņ╣ńSoCż╩ż╔ż╬╣ŌĮĖ└čICż“└▀╝Ŗż╣żļŠņ╣ńż╬└▀╝Ŗż╬źŽĪ╝ź╔ź”ź©źóĖĪŠ┌ż╦╗╚ż”ż│ż╚ż¼¾HżżĪŻż│ż╬ż┐żßź┴ź├źūż╬└ņŃ~ĀC└迎żĮżņż█ż╔╠õ¼öż╦ż╩żķż╩żżĪŻ║Żövż╬Č\Įčż╬żĶż”ż╦╩Ż┐¶ż╬ź┴ź├źūż“▓Żż╦╩┬ż┘żļöĄ╦ĪżŽ3╝ĪĖĄ▓Įż╬║Ūø]š{▀`ż╦żóżļĪŻ

ż┐ż└żĘĪó▓Żż╦╩┬ż┘żļźßźĻź├ź╚żŽ▓┐ż½ĪŻFPGA×æēäż“1Ė─ż║ż─╩┬ż┘żŲżŌŲ▒żĖżĶż”ż╦Ė½ż©żļż¼Īó├▒öüź┴ź├źūż“1Ė─ż║ż─└▄¶öż╣żļźµĪ╝źČĪ╝ż½żķĖ½żļż╚ĪóŪ█└■╣®µćż¼ØÖŠ’ż╦╩Ż╗©ż╦ż╩żļĪŻ╣ŌĮĖ└čż╬FPGAż“µu└▄żĄż╗ż┐ź┴ź├źūŲ▒╗╬ż“ż─ż╩ż░Šņ╣ńż╦żŽ1╦³żŌż╬└▄¶ö┼└ż“źŪĪ╝ź┐ż¼┴÷żļż│ż╚ż╦ż╩żļż╚żżż”ĪŻźżź¾ź┐Ī╝ź▌Ī╝źČż½żķTSVżŪź▄Ī╝źļ├╝╗ęż“Įąż╗żąźūźĻź¾ź╚┤łźßĪ╝ź½Ī╝ż╬╚čż’żĘżĄżŽ“£═Ķż╚╩čż’żķż╩żżĪŻźµĪ╝źČĪ╝ż╦ż╚ż├żŲżŽźĻź╣ź»Ę┌žōż╚ż╩żļĪŻ2ż─ż╬FPGAź┴ź├źūż“źūźĻź¾ź╚┤łæųż╦╩┬ż┘żļŠņ╣ńż╚╚µż┘żļż╚Īó─_ż═ż┐źĘźĻź│ź¾żŪżŽ└▄¶öż╬źąź¾ź╔╔²żŽ1W┼÷ż┐żĻ100Ū▄ż╚ż╩żĻĪóźņźżźŲź¾źĘżŽ1/50ż╦Į╠ż▐żļż╚Ų▒╗■ż╦Īó╣ŌÅ]ż╬źĘźĻźóźļżóżļżżżŽźčźķźņźļI/OżŽ╗╚ż’ż╩ż»żŲ║čżÓĪŻ

źČźżźĻź¾ź»ź╣żŽĪóż│ż╬Č\Įčż“28nmż╬Virtex-7źĘźĻĪ╝ź║ż╬LX2000TźŪźąźżź╣ż╦┼¼├ōżĘĪóż╣żŪż╦Ų■Š}▓─ē”ż╩źĮźšź╚ź”ź©źóźĄź▌Ī╝ź╚ź─Ī╝źļISE Design Suit 13.1ż“╗╚ż├żŲźĮźšź╚│½╚»żŪżŁżļż╚ż╣żļĪŻż│ż╬28nmż╬LX2000TżŽĪóĖĮ║▀║Ū└Ķ├╝ż╬28nmźūźĒź╗ź╣ż“╗╚ż├ż┐║ŪĮjĮĖ└č┼┘ż╬FPGAż╚╚µż┘żŲźĒźĖź├ź»═Ų╬╠żŽ3.5Ū▄░╩æųż╦ż╩żĻĪóźĘźĻźóźļź╚źķź¾źĘĪ╝źąż“ĮĖ└čżĘż┐╣ŌĮĖ└čż╬28nmFPGAż╚╚µż┘żŲżŌźĒźĖź├ź»═Ų╬╠żŽ2.8Ū▄ż╦żŌ├Żż╣żļż╚żżż”ĪŻ

ż│ż╬ź┴ź├źūżŽ╣ŌĮĖ└čĖ■ż▒ź▐źżź»źĒźąź¾źūČ\Įčż“╗╚żżĪóTSMCż╬28nmźūźĒź╗ź╣żŪÖ┌ŠÅż╣żļĪŻ╩Ż┐¶ż╬FPGAż“źūźĻź¾ź╚┤łż╦┼ļ║▄ż╣żļŠņ╣ńż╚╚µż┘żŲĪóŠ├õJ┼┼╬üĪóźĘź╣źŲźÓź│ź╣ź╚Īó┤łövŽ®ż╬╩Ż╗©żĄĪóż╬ż╔żņżŌµ£żŲ═źżņżŲżżżļż╚żĘżŲżżżļĪŻTSMCż╬źĘź╦źóźąźżź╣źūźņźĖźŪź¾ź╚żŪżóżļShang-Yi ChiangĢ■ż╦żĶżļż╚ĪóTSVż╚źĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČż“╗╚ż├żŲźĘźĻź│ź¾ż“żĮż╬æųż╦┼ļ║▄ż╣żļöĄ╦ĪżŽĪóźČźżźĻź¾ź»ź╣ż╦ż╚ż├żŲźĻź╣ź»ż¼Ę┌žōżĄżņĪó╬╠ŠÅ²ŗæųż╦żóżļż╚żżż”ĪŻ