Mentor GraphicsĪóSI/PIżõ3D┼┼╝¦─c▓“└Žż“┤▐żÓ┴Ē╣ńźĘź▀źÕźņĪ╝ź┐ż“╚»Ūõ

LSIż╬└▀╝Ŗż½żķPCB└▀╝ŖĪó┴╚ż▀╣■ż▀źĘź╣źŲźÓż▐żŪ╣Łż»ź½źąĪ╝żĘżŲżżżļMentor GraphicsżŽĪóźūźĻź¾ź╚övŽ®┤łæųż“┼┴┴„└■Ž®ż¼┴÷żļżĶż”ż╩╣ŌÅ]┐«ęÄ┼┴┴„żõź╬źżź║╚»Ö┌ż“źĘź▀źÕźņĪ╝źĘźńź¾żŪżŁżļ┴Ē╣ńźĘź▀źÕźņĪ╝ź┐ź─Ī╝źļHyperLynxż“╚»╔ĮżĘż┐ĪŻ“£═Ķż╬┼┴┴„źĘź▀źÕźņĪ╝ź┐ż╚╚µż┘Īó┐¶Ø▓Ū▄żŌ╣ŌÅ]ż╦±T▓╠ż¼įużķżņżļż╚żĘżŲżżżļĪŻ

┐▐1ĪĪSI/PIżõ3D┼┼╝¦▓“└ŽźĮźļźąĪóDRCż“┼²╣ńżĘż┐HyperLynxĪĪĮąųZĪ¦Mentor Graphics

HyperLynxż╦żŽĪóźĘź░ź╩źļźżź¾źŲź░źĻźŲźŻĪ╩SIĪ╦ż╚źčź’Ī╝źżź¾źŲź░źĻźŲźŻĪ╩PIĪ╦Īó3╝ĪĖĄ┼┼╝¦─cĪ╩EMĪ╦źĮźļźąż╚żżż├ż┐źĘź▀źÕźņĪ╝ź┐ż╚Īó╣ŌÅ]źŪźČźżź¾źļĪ╝źļź┴ź¦ź├ź»Ī╩DRCĪ╦ż╩ż╔ż╬źĮźšź╚ź”ź©źóż¼Ų■ż├żŲżżżļĪŻźżź¾źŲź░źĻźŲźŻż╚żŽĪóŲ■╬üāSĘ┴ż╦×┤żĘżŲĪóĮą╬üāSĘ┴ż¼╩°żņż║ż╦┼┴┴„żĄżņżļż│ż╚ż¼═²„[┼¬żŪżóżļż¼ĪóżĮż╬═²„[ż╦ż╔żņż└ż▒ŖZż┼żżżŲżżżļż╬ż½ż“╩¼└Žż╣żļČ\ĮčżŪżóżļĪŻźčźļź╣┐«ęÄż“żŁżņżżż╩āSĘ┴żŪ┴„┐«żĘż┐ĖÕĪó┼┴┴„└■Ž®ż“┼┴ż’żļż”ż┴ż╦╩°żņżŲżĘż▐ż”ż│ż╚ż¼żĶż»żóżļĪŻ╩°żņż╣ż«żļż╚Ż▒ż╚0ż╬āSĘ┴ż“╚Į╩╠żŪżŁż╩ż»ż╩żļ(┐▐2)ĪŻ▓┐Gbpsż▐żŪ┼┴┴„żŪżŁżļż½Īóż╚żżż”┴T╠ŻżŽĪó┼┴┴„żĘż┐ĖÕż╦Ż▒ż╚0ż“╚Į╩╠żŪżŁżļ║ŪĮjż╬źŪĪ╝ź┐źņĪ╝ź╚ż“╗žżĘżŲżżżļĪŻ

![┐▐2ĪĪ1ż╚0ż“╚Į╩╠ż╣żļźóźżźčź┐Ī╝ź¾ (eye pattern) żŽ╣ŌÅ]▓Įż╣żņżąż╣żļż█ż╔Īóų`(eye)ż¼ż─żųżņżŲżŁżŲ╚Į╩╠żŪżŁż╩ż»ż╩żļĪĪĮąųZĪ¦Mentor Graphics](/archive/editorial/technology/img/TFD160405-01b.jpg)

┐▐2ĪĪ1ż╚0ż“╚Į╩╠ż╣żļźóźżźčź┐Ī╝ź¾ (eye pattern) żŽ╣ŌÅ]▓Įż╣żņżąż╣żļż█ż╔Īóų`(eye)ż¼ż─żųżņżŲżŁżŲ╚Į╩╠żŪżŁż╩ż»ż╩żļĪĪĮąųZĪ¦Mentor Graphics

źĘź░ź╩źļźżź¾źŲź░źĻźŲźŻĪ╩Signal integrityĪ╦żŽĪóövŽ®ż╬┐«ęÄż¼żŁż┴ż¾ż╚żĘż┐źčźļź╣āSĘ┴żŪ├ķ╝┬ż╦┼┴├ŻżĄżņżŲżżżļż½ż“ź┴ź¦ź├ź»ż╣żļČ\ĮčżŪĪó─ŠŚlż╣żļż╚┐«ęÄ├ķ╝┬┼┘ż└ż¼Īó┐«ęÄēä䮿╚ŚlżĄżņżŲżżżļĪŻŪ█└■ż“┼┴ż’żļ┐«ęÄżŽĪó╔ŌŅ^═Ų╬╠żõ╔ŌŅ^źżź¾ź└ź»ź┐ź¾ź╣ż╬▒Ųūxż“£pż▒Īó║ŪĮķż╦Ų■╬üżĘż┐źčźļź╣āSĘ┴żŽ╗═│čĘ┴ż½żķØŁż║╩°żņżļĪŻżĮżņżŪżŌ╩°żņżļµć┼┘ż¼Š»ż╩ż▒żņżąĪóŪ█└■ż╬Į¬├╝ŖõżŪźčźļź╣ż╚żĘżŲŪ¦╝▒żŪżŁżļĪŻ

źčź’Ī╝źżź¾źŲź░źĻźŲźŻżŽĪó┼┼Ė╗źķźżź¾ż╬╩°żņż“╔Įż╣Ė└±äżŪżóżĻĪó┼┼Ė╗źķźżź¾ż¼╬Ńż©żą5Vż╩żķż╔ż╬żĶż”ż╩ż│ż╚ż¼żóż├żŲżŌ5Vż½żķ╩°żņżŲżżż╩żżż½ż“ź┴ź¦ź├ź»ż╣żļĪŻ┼┼Ė╗ēä䮿╚ŚlżĄżņżŲżżżļĪŻ─╠Š’żŽĪó┼┼Ė╗źķźżź¾ż╬ż╔ż│ż½żŪĮj┼┼╬«ż¼░·żŁĮążĄżņżļż╚┼┼░Ąż¼5Vż½żķ▐k╗■┼¬ż╦▓╝ż¼żļżĶż”ż╦ż╩żļĪŻ▓╚ż╬╬«żĘ±śżŪ┐Õ╠O┐Õż“╗╚ż├żŲżżżļ╗■ż╦Īóź╚źżźņż╩ż╔Įj╬╠ż╬┐Õż“▐kĄżż╦╗╚ż©żąĪó┐Õż¼║┘ż»ż╩żļĖĮō■ż╚Ų▒żĖż│ż╚ż└ĪŻźčź’Ī╝źżź¾źŲź░źĻźŲźŻżŽżŁż┴ż¾ż╚5Vż¼│╬╩▌żĄżņżŲżżżļėXČĘż“╔Įż╣╝▄┼┘żŪżóżļĪŻ

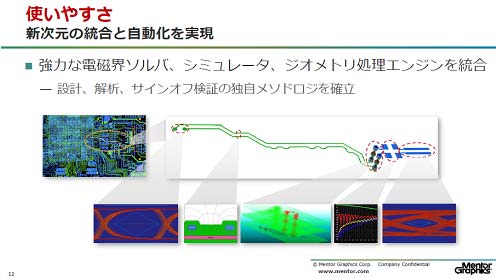

3D┼┼╝¦─c▓“└ŽżŽ┼┼╝¦āSĪóż╣ż╩ż’ż┴┼┼āSż╚żĘżŲż╬└Łä®ż“─┤ż┘żļż┐żßż╬Š}├╩żŪżóżĻĪó├▒ż╩żļŪ█└■ż¼─Š╬«ż╚żŽµ£ż»░█ż╩żļėX▌åż╦ż╩żļż│ż╚ż“ē¶żļż│ż╚ż¼żŪżŁżļĪŻź╬źżź║żŽ┼┼╝¦āSżŪżóżĻĪó╚¶ż¾żŪ═Ķż┐żĻ╚»Ö┌żĘż┐żĻżĘżŲżżżļėX▌åż“ē¶żņżąĪó╦╔ż░Ī”═▐ż©żļż│ż╚ż¼żŪżŁżļżĶż”ż╦ż╩żļĪŻ┼┼╗ęövŽ®żŪżŽźūźĻź¾ź╚┤łżŪżóżĒż”ż╚źĘźĻź│ź¾╚ŠŲ│öüź┴ź├źūżŪżóżĒż”ż╚Ų▒żĖżĶż”ż╦Īó╣ŌÅ]Ī”╣Ō╝■āSŲ░║ŅżõĮj┼┼╬«Ų░║ŅżŪżŽĪóSIżõPIĪó3D┼┼╝¦─c▓“└Žż¼ØŁ═ūż╦ż╩żļĪŻ

╣ŌÅ]źļĪ╝źļź┴ź¦ź├ź»DRCżŽĪóæųż╬żĶż”ż╩źĘź▀źÕźņĪ╝źĘźńź¾ż╚żŽ░ŃżżĪóövŽ®źčź┐Ī╝ź¾żõŪ█└■ż╩ż╔ż╬└▀╝ŖźŪĪ╝ź┐ż¼źŪźČźżź¾źļĪ╝źļż╦░Ń╚┐żĘżŲżżż╩żżż½ż╔ż”ż½ż“ź┴ź¦ź├ź»ż╣żļż┐żßż╬ź─Ī╝źļĪŻövŽ®ż¼╩Ż╗©ż╦ż╩żņżążŌżŽżõ┐═ż╬┤ŃżŪ░Ń╚┐ż“ź┴ź¦ź├ź»ż╣żļż╬ż¼Įj╩čż╩ż█ż╔╦─Įjż╦ż╩ż├żŲż»żļż┐żßĪóź│ź¾źįźÕĪ╝ź┐ż“╗╚ż├żŲźļĪ╝źļ░Ń╚┐ż“─┤ż┘żļĪŻ

ż│ż”żżż├ż┐ź┴ź¦ź├ź»ĄĪē”żŽĪóż│żņż▐żŪĖ─╩╠ż╦żóżĻĪóżĘż½żŌżĮżņżŠżņż╬GUIż“Ęeż├żŲżżż┐ż┐żßĪó╗╚żżż┼żķż»±T▓╠ż╚żĘżŲź┴ź¦ź├ź»╗■┤ųż¼ż½ż½ż├żŲżżż┐ĪŻ▓├ż©żŲĪóźūźĻź¾ź╚övŽ®żŽ¾Hźįź¾▓Įż¼┐╩ż▀└▀╝ŖżŽ╩Ż╗©ż╦ż╩ż├żŲżŁż┐ĪŻ╬Ńż©żąĪóźĖź¦ź├ź╚└’’hĄĪźčźżźĒź├ź╚ż╬źžźļźßź├ź╚ŲŌż╦żŽźšźņźŁźĘźųźļ┤łæųż╦2300┼└░╩æųż╬ŗēäż¼║▄żĻĪó1╦³2000Ė─żŌż╬źėźóż¼│½żżżŲżżżļĪŻ┼┼Ė╗┼┼░ĄżŌ30░╩æųż╬┼┼Ė╗źņĪ╝źļż¼Ę┴└«żĄżņżŲżżżļĪŻż│ż”żżż├ż┐┤łövŽ®ż“╗Ņ║Ņż╣żļØiż╦ĪóźĘź▀źÕźņĪ╝źĘźńź¾ż“╗╚ż├żŲSIżõPIĪóź╬źżź║ż╬▒Ųūxż╩ż╔ż“ź┴ź¦ź├ź»żĘĪóØ▓╩¼ż╩═Š═ĄżŪŲ░║ŅżĘżŲżżżļż½ż╔ż”ż½ż“│╬Ū¦żĘżŲż¬ż»ØŁ═ūż¼╣Ōż▐ż├żŲżżżļĪŻ║Ņż├żŲż½żķT┘ćż└ż╚╗■┤ųż¼ż½ż½żĻĪ󿥿ķż╦Ų░║Ņ═Š═Ąż╦┤žżĘżŲżŌ─┤ż┘ż╦ż»żżĪŻ╗Ņ║ŅØiż╦źĘź▀źÕźņĪ╝źĘźńź¾żŪ│╬Ū¦żĘżŲż¬ż▒żą1övżŪ┘抒ż╦Ų░║Ņż╣żļ▓─ē”└ŁżŽ╣Ōż▐żļĪŻ

ØŖż╦PCI Expressż╬żĶż”ż╩╣ŌÅ]źĘźĻźóźļźżź¾ź┐źšź¦Ī╝ź╣ż└ż╚Ū█└■Ž®ż╬Į¬├╝żŪźčźļź╣āSĘ┴ż¼╚Į╩╠żŪżŁż╩żżż│ż╚żŌżóżļ(┐▐2)ĪŻ│╬Ū¦żŽØŁ┐▄ż└ĪŻż▐ż┐ĪóźßźŌźĻżŪżŌDDR3ż½żķDDR4Ī󿥿ķż╦żĮż╬└Ķż╦żŽHMCĪ╩Hybrid Memory CubeĪ╦żõHBMĪ╩High Bandwidth MemoryĪ╦ż╬żĶż”ż╩3╝ĪĖĄź╣ź┐ź├ź»źßźŌźĻżŪż╬Ų░║Ņ│╬Ū¦ż¼ØŁ═ūż╦ż╩żļĪŻ

▒ķōQē”╬üż╬╣ŌżżźūźĒź╗ź├źĄżõFPGAż╩ż╔żŪżŽ╚∙║┘▓Įż╦żĶżļ─Ń┼┼░Ą▓ĮżŪźėźóż¼╗\▓├ż╣żļż┐żßĪóżĮż╬ŗ╩¼żŪż╬źĻź┐Ī╝ź¾źčź╣ż╦żĶżļ▒ŲūxĪóź▄ź¾źŪźŻź¾ź░ź’źżźõ└▄¶öż╦żĶżļźżź¾ź└ź»ź┐ź¾ź╣ż╬╗\▓├ż╦żĶżļSI/PIż╬ź┴ź¦ź├ź»żŽ’Lż½ż╗ż╩ż»ż╩żļĪŻż│ż╬ż┐żßż╦ĪóSI/PIż╬źĘź▀źÕźņĪ╝źĘźńź¾źŌźŪźļż“╣Į├█ż╣żļż│ż╚żŽ╗■┤ųż¼ż½ż½żĻĪóČ\Įč┼¬ż╦żŌžMżĘżżĪŻżĄżķż╦3D╝┬äóż╬źĘź▀źÕźņĪ╝źĘźńź¾żŌØŁ═ūż╦ż╩żļĪŻ└ņ╠ń┼¬ż╩ź©źŁź╣źčĪ╝ź╚ż“┐¶¾Hż»žQż©ż╩ż▒żņżą╠õ¼öż“▓“»éżŪżŁż╩ż»ż╩żļĪŻ

┐▐3ĪĪLSIż½żķż╬┐«ęÄż¼Į¬├╝ż╦┼┴ż’żļ══╗ęż“┤░µ£źĘź▀źÕźņĪ╝ź╚żŪżŁżļĪĪĮąųZĪ¦Mentor Graphics

HyperLynxżŽĪó╣Ō╗@┼┘ż╬źĘź▀źÕźņĪ╝źĘźńź¾ż“╣ŌÅ]ż╦╝┬╣įżŪżŁżļæųż╦Īó┼²▐kżĘż┐GUIż“╗╚ż├żŲ╗╚żżżõż╣żżż╚żżż”źßźĻź├ź╚ż¼żóżļĪŻ╬Ńż©żąĪó┐▐3ż╬żĶż”ż╩Ū█└■żŪżŽ╚ŠŲ│öüź┴ź├źūż╬źčź├ź╔ż╬Ų■żĻĖ²żŪż╬1Īó0┼┴┴„āSĘ┴(źóźżźčź┐Ī╝ź¾)żõĪó²ŗ├µżŪż╬éāĀCĘ┴ėXĪó¾H┴žźėźóż╬3╝ĪĖĄĘ┴ėXĪ󟣟џčźĘź┐ż“└▀ż▒ż┐ŠņĮĻżŪż╬āSĘ┴ż╬│╬Ū¦Īó║ŪĮ¬├╝żŪż╬źóźżźčź┐Ī╝ź¾Īóż╚żżż├ż┐▐kŽóż╬Ų░║ŅżõĘ┴ėXż“ē¶żļż│ż╚ż¼żŪżŁżļĪŻĘ┴ėXżŽźĖź¬źßź╚źĻź©ź¾źĖź¾ż“┼ļ║▄żĘżŲżżżļż½żķ╔Įż╗żļĪŻĪų─╣żżŪ█└■ż╬IRź╔źĒź├źūżõĪóPIż╬źĘź▀źÕźņĪ╝źĘźńź¾żŽ“£═Ķż╬10~15Ū▄Å]ż½ż├ż┐ż╚żóżļĖ▄Ąęż½żķĖ└ż’żņż┐Īūż╚Mentor Graphics╝ęSystem Design DivisionĪóBusiness Development Managerż╬David WiensĢ■żŽĖņżļĪŻ

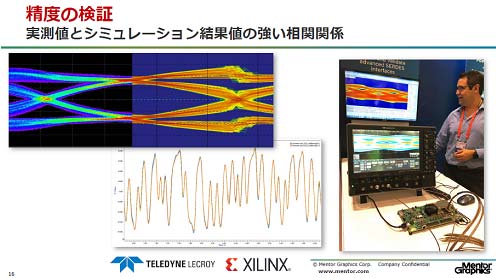

żĘż½żŌ╗@┼┘żŽ╣ŌżżĪŻ▒R─Ļ▀_ż“╗╚ż├ż┐╝┬▒R├═ż╚źĘź▀źÕźņĪ╝źĘźńź¾├═ż╬┴Ļ┤žżŽ╣Ōż»Īóż█ż╚ż¾ż╔▐k├ūżĘżŲżżżļĪŻ┐▐4żŽXilinxż╬FPGAż“╗╚ż├żŲ╣ŌÅ]┼┴┴„żĘż┐╗■ż╬▒R─Ļ├═ż╚HyperLynxźĘź▀źÕźņĪ╝ź┐ż╚ż╬╚µ│ėżŪżóżļĪŻ

┐▐4ĪĪ╝┬▒Rż╚źĘź▀źÕźņĪ╝źĘźńź¾żŽżĶż»▐k├ūżĘżŲżżżļĪĪĮąųZĪ¦Mentor Graphics

ż│ż”żżż├ż┐╣Ō╗@┼┘żŪ╣ŌÅ]▓Įż“╝┬ĖĮżŪżŁż┐ż╬żŽĪó└▀╝ŖźŪĪ╝ź┐ż╚šl╔┘ż╩źĘź▀źÕźņĪ╝źĘźńź¾ź─Ī╝źļż“├ō┴TżĘĪóżĮżņżķż“śOŲ░┼¬ż╦╚Į╩╠ż╣żļż½żķżŪżóżļĪŻDRCżŪŪ█└■ż╬źļĪ╝źļż“ź┴ź¦ź├ź»żĘĪóĘQ¹|övŽ®źĘź▀źÕźņĪ╝ź┐ż“Ęeż├żŲżżżļĪŻSPICEżõIBISż╦▓├ż©Īó3╝ĪĖĄ┼¬ż╩Ę┴ėXż“║ŅżĻĪ”▓“└Žż╣żļż┐żßż╬Ń~Ė┬═ū┴Ū╦ĪĪ╩FEMĪ╦żõ┼┼╝¦─cż╬sźčźķźßĪ╝ź┐źŌźŪźļżŌżóżļĪŻ▓├ż©żŲĪóźėźóż╬▒Ųūxżõź▐źżź»źĒź╣ź╚źĻź├źūźķźżź¾ż╬▓“└Žż╦ØŁ═ūż╩3Dż╬┼┼╝¦─c▓“└Žź─Ī╝źļżŪżŽĪó╝┬żŽ2.5D▓“└ŽĪóż╣ż╩ż’ż┴quasi-staticĪ╩ØŹ¼ś┼¬Ī╦ż╩źĮźļźąż“╗╚ż├żŲĘ┴ėXż“├▒ĮŃ▓Įż╣żļż│ż╚żŪ╣ŌÅ]▓Įż“┐▐ż├żŲżżżļĪŻĮŃ┐Ķż╦3╝ĪĖĄ▓“└Žż└ż╚╗@┼┘żŽ╣Ōżżż¼╝ŖōQ╗■┤ųż¼ż½ż½żĻż╣ż«żļĪŻż│ż│żŪżŽ╗@┼┘ż¼ØŁ═ūż╩ŠņĮĻżŽ3DżŪĪó╗@┼┘ż“żĮżņż█ż╔ØŁ═ūż╚żĘż╩żżŠņĮĻżŽ2╝ĪĖĄżŪ▓“└Žż╣żļĪŻ

HyperLynxż╬ĖŁżżĮĻż└ż¼Īó┼┴┴„Ž®ż╦▐pż├żŲ┐«ęÄż╬╬«żņż“▓“└ŽżĘżŲżżż»Šņ╣ńĪóØó╦ĪżõĘ┴ėXźčź┐Ī╝ź¾ż“Ė½żŲĪóż╔ż╬źĘź▀źÕźņĪ╝źĘźńź¾źŌźŪźļż“╗╚ż”ż┘żŁż½ż“śOŲ░┼¬ż╦╚Įéāż╣żļż╚żĘżŲżżżļĪŻPCB└▀╝ŖźŪĪ╝ź┐żŽMentorż└ż▒żŪżŽż╩ż»Īó┐▐Ė”żõCadence Allegroż╬└▀╝ŖźŪĪ╝ź┐żŌźżź¾ź▌Ī╝ź╚żŪżŁżļż╚żżż”ĪŻ