źČźżźĻź¾ź»ź╣Īó3D-ICĪóSoCĪóFPGAŠ}╦ĪżŪ28nmż½żķ20nmżžöĪ╣į

źČźżźĻź¾ź»ź╣ż¼28nmźūźĒź╗ź╣ż╬ŗī1└ż┬ÕFPGAż½żķĪó20nmźūźĒź╗ź╣ż“ŠW(w©Żng)├ōż╣żļŗī2└ż┬ÕFPGAż“└čČ╦┼¬ż╦┐╩żßżŲżżżļĪŻŗī2╗═╚Š┤³(4~6ĘŅ)ż╦żŽ┴ßż»żŌźŲĪ╝źūźóź”ź╚ż╣żļ╝Ŗ▓Ķż└ĪŻTSMCż“źšźĪź”ź¾ź╔źĻż╚żĘżŲ×æļ]ż“░══ĻżĘĪóżĮż╬└▀╝Ŗź─Ī╝źļż“3ĘŅ├µż╦żŽ├ō┴Tż╣żļĪŻ

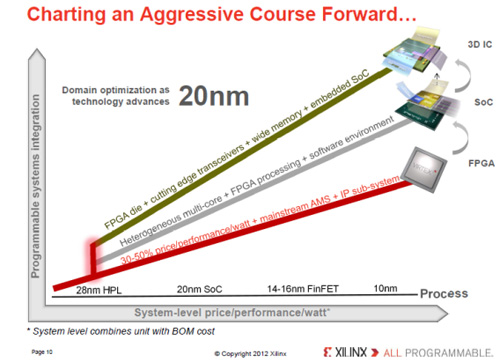

┐▐1ĪĪ28nmż½żķ╗Žż▐ż├ż┐3¹|╬Óż╬ICżŽ20nmżŪżŽŗī2└ż┬Õż╦Ų■żļĪĪĮąųZĪ¦Xilinx

źČźżźĻź¾ź»ź╣żŽ45nm/40nm╗■┬Õżóż┐żĻż½żķTSMCż╚źĄźÓź╣ź¾ż“źšźĪź”ź¾ź╔źĻż╚żĘżŲ╗╚ż├żŲżżż┐ż¼Īó28nmż½żķżŽTSMCż╦ĮĖ├µżĘżŲżżżļĪŻ28nmżŪżŽTSMCż╬HPLźūźĒź╗ź╣ż“╗╚ż├żŲżżż┐ż┐żßĪóÖ┌ŠÅż╦ܦŠŃż“żŁż┐żĄż╩ż½ż├ż┐ĪŻżĘż½żĘ28nmż╬LPźūźĒź╗ź╣ż╬Ö┌ŠÅż¼╬®ż┴æųż¼żķż╩ż»żŲĪ󟻟óźļź│źÓżõnVidiaż╩ż╔ż╬źóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄż“╗ūż”żĶż”ż╦Įą▓┘żŪżŁż╩ż½ż├ż┐ż╚żżż”∙ZżżĘą┘xż¼żóż├ż┐ĪŻ20nmżžżŽ28nmHPLż¼└«Ė∙ż“╝²żßż┐ż┐żßż╦żĮż╬ż▐ż▐ź╣źÓĪ╝ź║ż╦öĪ╣įżŪżŁżļż╚Ė½żŲżżżļĪŻ

ż▐ż┐ĪóźČźżźĻź¾ź»ź╣żŽ28nmż½żķ╗Žż▐ż├ż┐┐ʿʿżFPGAż╬Ę┴▌åż“3¹|╬ÓĘeż─(┐▐1)ĪŻ▐kż─żŽĪó3D-ICĪ╩źĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČż“▓żĘżŲ2.5Dż╚żŌŌ}żųĪ╦ż└ĪŻŲ¾ż─ų`żŽĪóARMż╬źŪźÕźóźļź│źóż╚AMBAźąź╣ż“╗╚żżĪóFPGAövŽ®żŪź½ź╣ź┐ź▐źżź║ż╣żļSoCżŪżóżļĪŻįÆż─ų`żŽź╚źķź¾źĘĪ╝źą├ōż╩ż╔ż╬“£═Ķż╬FPGAĪŻż│żņżķżŽµ£żŲ28nmż“ŗī1└ż┬Õż╚żĘżŲ20nmż╬ŗī2└ż┬Õżžż╚öĪ╣įż╣żļĪŻ

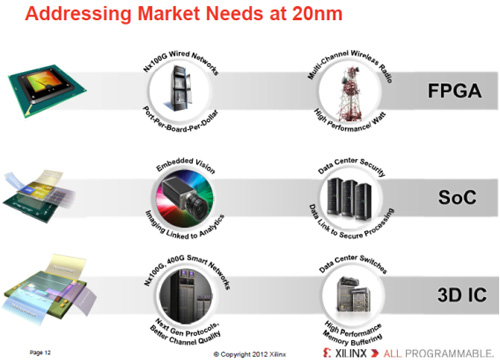

3D-ICżŽĪóźßźŌźĻż“╩┬š`Ų░║ŅżĄż╗żŲ╣ŌÅ]ż╬źąź├źšźĪźĻź¾ź░ż“╣įż”╣Ō└Łē”żŽźĄĪ╝źąĪ╝żõ100G/400Gbpsż╬äō(chu©żng)└■┤├ŽČ╔ź╣źżź├ź┴ż╩ż╔ĪóSoCżŽźėźĖźńź¾źĘź╣źŲźÓżõ▓ĶćĄ▓“└ŽźĘź╣źŲźÓż╩ż╔źŽĪ╝ź╔ź”ź©źóż╚źĮźšź╚ź”ź©źóż╬źūźĒź░źķź▀ź¾ź░ż“╣įż”├ō²ŗż“┴└ż”ĪŻż▐ż┐FPGAżŽĪóLTEż╩ż╔ż╬ź’źżźõźņź╣─╠┐«┤├ŽČ╔ż╦Ė■ż»ż╚Ė½żŲżżżļĪ╩┐▐2Ī╦ĪŻ

┐▐2ĪĪ20nmź┴ź├źūż╬╝ńż╩├ō²ŗĪĪĮąųZĪ¦Xilinx

3D-ICżŽĪóĖĮ║▀ŖW─ĻżĘżŲĮą▓┘żĘżŲżżżļż╚żżż”ĪŻ╩┐ĀCæųż└ż¼ź┴ź├źū┤ųż“źĘźĻź│ź¾ż╬źżź¾ź┐Ī╝ź▌Ī╝źČż“─╠żĘżŲż─ż╩ż░ż┐żßĪóęÆūāż¼Š«żĄż»Īó1└ż┬Õ└Ķż╬Įj(lu©░)═Ų╬╠ż¼įużķżņżļż╚ż╣żļĪŻż│żņż▐żŪżŽŲ▒żĖź┴ź├źūż“╩┬š`ż╦└▄¶öż╣żļż│ż╚ż¼¾Hż½ż├ż┐ż¼Īóż│żņż½żķżŽ░Ńż”¹|╬Óż╬źžźŲźĒź┴ź├źūż“źĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČæųż╦Ę┴└«żĘżŲżżż»ĪŻ┤├ŽČ╔ż╬ź═ź├ź╚ź’Ī╝ź»ż╬ź╣źįĪ╝ź╔ż““£═Ķż╬10Gbpsż½żķ40Gbpsżžż╚┐╩▓ĮżĘĪó║ŻżŽ100GbpsźĘź╣źŲźÓż“│½╚»├µż└ż╚żżż”ĪŻ

║Żż╬ż╚ż│żĒĪó┤░µ£ż╩3╝ĪĖĄICż╚żżż”ŚlżŪżŽż╩żżż¼Īóź│ź╣ź╚ż╚└Łē”ż╬┼└żŪżŽŲ¾ż─ż╬ź┴ź├źūż“─_ż═ż║ż╦źĘźĻź│ź¾źżź¾ź┐Ī╝ź▌Ī╝źČż╬æųż╦ĮĖ└čż╣żļöĄ(sh©┤)ż¼Ń~ŠW(w©Żng)żŪżóżļĪŻź│ź╣ź╚ĀCżõźŲź╣ź╚ż╬żĘżõż╣żĄż╩ż╔ż╬┼└żŪĪó┼÷╩¼ż│ż╬2.5╝ĪĖĄż╬LSIż“┐╩▓ĮżĄż╗żŲżżż»ĪŻ

SoCżŪżŽ┴╚ż▀╣■ż▀źĘź╣źŲźÓ┴└żżż╬ZynqźĘźĻĪ╝ź║×æēäż¼żóżļĪŻż│żņżŽź░źļĪ╝źĒźĖź├ź»ż╚CPUżõźßźŌźĻĪóFPGAż╩ż╔ż“1ź┴ź├źūż╦ĮĖ└čżĘżŲż¬żŁĪóźŽĪ╝ź╔ź”ź©źóż╬źūźĒź░źķźÓż“FPGAżŪ╣įż”ĪŻż┐ż└żĘĪóŲ■Įą╬üż╬╔²ż¼ź▄ź╚źļź═ź├ź»ż╦ż╩żļ▓─ē”└Łż¼żóżĻĪóż│ż╬ŗ╩¼żŽFPGAż¼├┤┼÷ż╣żļĪŻCPU┤žĘĖż“źĮźšź╚ź”ź©źóĪóFPGAż“źŽĪ╝ź╔ź”ź©źóżŪżĮżņżŠżņźūźĒź░źķź▀ź¾ź░żŪżŁżļż┐żßĪóźšźņźŁźĘźųźļż╩ź┴ź├źūż╦Ė■ż»ĪŻ

┤├ŽČ╔äóÅøż╦╗╚ż’żņżļ╣ŌÅ]ż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣żŽżŌżŽżõASSPż╩ż╔źŽĪ╝ź╔ź”ź©źóż└ż▒żŪżŽ╝┬ĖĮżŪżŁż╩żżż╚Ė½żļĪŻźūźĒź╗ź╣ż╬╚∙║┘▓Į┐╩·tż¼Å]ż»ż╩żļż╚Č”ż╦└▀╝Ŗż╦╗■┤ųż¼ż½ż½żĻāįż«żļż½żķż└ĪŻżĘż½żŌLTEżŽĘQ╣±ĘQ├Ž░ĶżŪ╗┼══ż¼░█ż╩żĻĪóźūźĒź░źķźÓżŪ╗┼══ż“╩čż©żļöĄ(sh©┤)ż¼Å]żżĪŻż▐ż┐LTEżŽ╝Īż╬LTE-AżžöĪ╣įż╣żļŠņ╣ńżŪżŌźūźĒź░źķźÓżŪźóź├źūź░źņĪ╝ź╔ż╣żļöĄ(sh©┤)ż¼Å]ż»żŲį~├▒ż└ĪŻ