ź▒źżźŪź¾ź╣ĪóSoC└▀╝Ŗ┤³┤ųż╬ęÆżņż╦żĶżĻĮj╔²ż╩ź│ź╣ź╚╗\ż“╗ž╝~Īó▓“»é║÷ż“─¾░Ų

SoCż╬ź│ź╣ź╚ż“║’žōż╣żļż┐żßĪóź▒źżźŪź¾ź╣Ī”źŪźČźżź¾Ī”źĘź╣źŲźÓź║╝ęż¼╝ń╠¢żĘż┐ĪųDA Show CDNLive! Japan 2009Īūż╦ż¬żżżŲĪóŲ▒╝ęźąźżź╣źūźņźĖźŪź¾ź╚ż╬Steve GlaserĢ■żŽIPż╬║ŲŠW├ōż╚żĮż╬ĖĪŠ┌└ŁĪó╣Ōżż├Ļō■└Łż¼│½╚»┤³┤ųż╬ø]Į╠ż╦Ė·▓╠┼¬ż╚╬ü└ŌżĘż┐ĪŻżĄżķż╦▌xŠņżžż╬┼ĻŲ■ż¼ęÆżņżļż╚ź│ź╣ź╚ż¼æųż¼żļż│ż╚ż“┐āżĘĪó┤³┤ųø]Į╠ż¼żżż½ż╦─_═ūż½ż╦ż─żżżŲĮęż┘ż┐ĪŻ

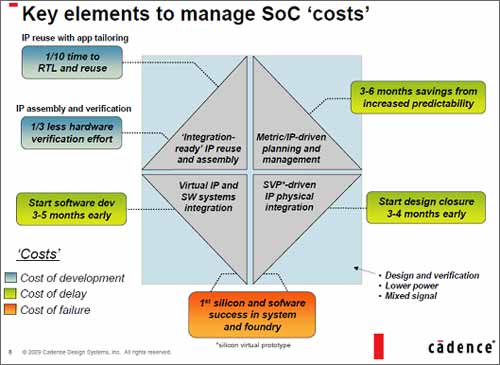

╩Ż╗©ż╩SoCż“└▀╝Ŗż╣żļæųżŪIPż╬ŠW├ōż╚ĪóTLMĪ╩ź╚źķź¾źČź»źĘźńź¾źņź┘źļźŌźŪźĻź¾ź░Ī╦ż╩ż╔ż╬├Ļō■▓ĮżŽ’Lż½ż╗ż╩żżĪŻSoCż╦żŽĪóźµĪ╝źČĪ╝ż╬═ūĄßż╣żļ─Ńżżź│ź╣ź╚ż╚║╣╩╠▓Į└’ŠSż╦╣ńż’ż╗żŲĪó50Ī┴100Ė─żŌż╬żĄż▐żČż▐ż╩IPż“1ź┴ź├źūż╦ĮĖ└čż╣żļĪŻż│ż╬Šņ╣ńĪóźóź╩źĒź░żõźŪźĖź┐źļĪóźĮźšź╚ź”ź©źóż╬IPż“ĮĖ└čż╣żļż╚żŁż╬ź▄ź╚źļź═ź├ź»ż¼ż╔ż│ż╦ż╩żļż╬ż½ż“├ĄżĘĪóźµĪ╝źČĪ╝ż╬═ūĄßż╚IPż╚ż╬┤žĘĖż“░·żŁĮąż╣ĪŻ

┘J┘Tż╬IPż“┐ʿʿż▒■├ōż╦╣ńż’ż╗żŲ─┤┼DżĘ║ŲŠW├ōżŪżŁżļżĶż”ż╦ż╣żļż┐żßż╦żŽĪóVerilogż╩ż╔ż“╗╚ż├żŲRTLż“Į±ż»ż╬żŪżŽż╩ż»Īó╣Ō░╠╣ń└«Ė■ż▒ż╦żŽSystemCĪóźóźļź┤źĻź║źÓż“╝ŖōQż╣żļż┐żßż╬źūźĒź░źķźÓżŽC/C++żŪĮ±ż»Īóż╚żżż”żĶż”ż╩├Ļō■źņź┘źļż╬╣ŌżżESL└▀╝Ŗż“╣įż”ĪŻż│żņż╦żĶż├żŲź│Ī╝ź╔╣į┐¶żŽžōżĻĪóźŪźąź├ź░żŌŠ»ż╩ż»żŪżŁżļż┐żßĪó║ŲŠW├ōżŪżŁżļżĶż”ż╦─┤┼Dż╣żļż┐żßż╬╗■┤ųżŽ1/10ż╦žōżķż╗żļż╚żżż”ĪŻ

▓├ż©żŲĪó┐ʿʿżSoCźóĪ╝źŁźŲź»ź┴źŃĪóIPäh▓┴ĪóIPż╬ĮĖ└č▓Įż╣żļŠņ╣ńż╬ź▀ź╣ż“╦╔ż░ż┐żßĪóżĮż╬╝┬äóėX▌åż“śOŲ░żŪĖ½żļż│ż╚ż╬żŪżŁżļĖĪŠ┌ź─Ī╝źļż“╗╚żżĪó╝┬äóĪ╩ĮĖ└č▓ĮĪ╦ż╣żļ╗■┤ųż““£═Ķż╬1/3ż╬╗■┤ųż╦ø]Į╠ż╣żļĪŻ

SoCµ£öüż╬└▀╝ŖżŽ3Ī┴4ź§ĘŅø]ż»żŪżŁżļĪŻż│ż│żŪSoCż╬Š├õJ┼┼╬üżõĮĖ└č▓Įż╣żļż╚żŁż╬öU╠¾Š“°Pż╩ż╔ż“Ė½└čżŌżĻĪó▓“└Žż╣żļĪŻTLMż╚RTLر═²╣ń└«ż╦żĶż├żŲر═²└▀╝Ŗż“║čż▐ż╗ĪóIPż╬ر═²ĮĖ└čĪóSoCż╬źąź╣żõŠ├õJ┼┼╬üĪ󟻟Ēź├ź»ęÆūāż╩ż╔ż“Ė½└čżŌżĻĪó┴ß┤³ż╦źšźŻĪ╝ź╔źąź├ź»ż“ż½ż▒żļż│ż╚żŪ╝┬║▌ż╬├═ż╚ż╬║╣ż“žōżķżĘżŲżżż»ĪŻFPGAż╩ż╔ż╬źĘźĻź│ź¾źūźĒź╚ź┐źżźįź¾ź░żŌŠW├ōżĘżŲźŽĪ╝ź╔ź”ź©źóż╬ĖĪŠ┌ż“╣įż”ĪŻ

źĮźšź╚ź”ź©źó│½╚»żŽSoCµ£öü└▀╝Ŗż╚ż█ż▄Ų▒╗■ż╦╗Žżßżļż│ż╚żŪźĮźšź╚ź”ź©źó│½╚»┤³┤ųż“3Ī┴5ź½ĘŅø]Į╠żŪżŁżļĪŻż│ż│żŪżŽĪóźūźĒź╗ź├źĄźŌźŪźļżõ▓Š„[┼¬ż╩IPż“║ŅżĻźĮźšź╚ź”ź©źóźĘź╣źŲźÓż“┼ļ║▄ż╣żļż│ż╚ż“„[─ĻżĘżŲ│½╚»ż“┐╩żßżļĪŻż│ż│żŪżŌTLMź┘Ī╝ź╣ż╬Ų╚śOIPż╚ĪóSystemCż“╝┬╣įżŪżŁżļźĘź▀źÕźņĪ╝ź┐ż“īÖ├ōż╣żļĪŻ

║ŪĮķż╬źĘźĻź│ź¾żŪ┤░µ£Ų░║Ņż“╝┬ĖĮż╣żļż┐żßż╦żŽĪó└▀╝Ŗó¬╝┬äóó¬źĘźĻź│ź¾źūźĒź╚ź┐źżźįź¾ź░ó¬äh▓┴Īóż╬Ę½żĻ╩ųżĘż“Ø▓╩¼ż╦╣įżż─Ļ└Ł┼¬ż╩═Į▒Rż“Įą═Ķżļż└ż▒ż─żųżĘżŲżżż»ĪŻ─Ļ╬╠┼¬ż╩äh▓┴ż“╣įż”ż│ż╚żŪ3Ī┴6ź§ĘŅ£I╠¾żŪżŁżļż╚żĘżŲżżżļĪŻ

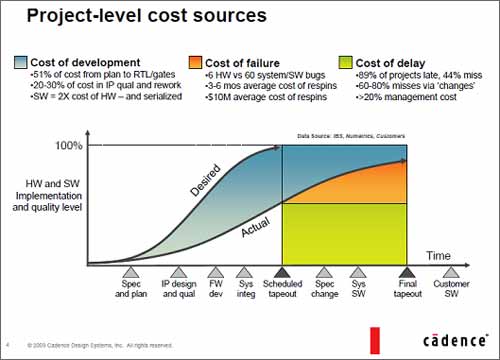

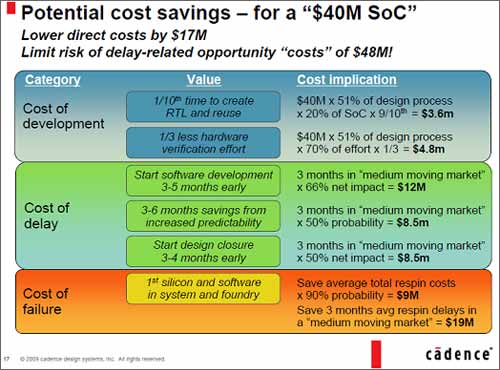

ż│ż”żżż├ż┐Š}╦Īż“╗╚ż”ż│ż╚żŪĪó│½╚»ź│ź╣ź╚ż╬║’žōĪó│½╚»┤³┤ųż╬ø]Į╠Īó1╚»┤░Ų░ż¼▓─ē”ż╦ż╩żļż╚żĘżŲĪó4000╦³ź╔źļż╬SoCż“│½╚»ż╣żļż╬ż╦Īó║ŪĮj6500╦³ź╔źļż╬ź│ź╣ź╚╗\ż¼żóżĻż”żļż╚╗ž╝~żĘż┐ĪŻżĮż╬ŲŌĪó─Š└▄ż╬ź│ź╣ź╚ż╚żĘżŲ1700╦³ź╔źļĪóęÆżņż╦żĶżļź▀ź╣żõ║ŅżĻ─ŠżĘż╩ż╔ż╬źĻź╣ź»żŪÖ┌żĖżļź│ź╣ź╚ż¼4800╦³ź╔źļż╚Ė½└čżŌż├żŲżżżļĪŻ