▒č╣±ØŖĮĖ2009Ī”┴╚ż▀╣■ż▀źĘź╣źŲźÓż“└ĶŲ│ż╣żļ└ņ├ōźūźĒź╗źĄż╬╗■┬Õż╦(2)

┴╚ż▀╣■ż▀źĘź╣źŲźÓ╗■┬Õż╬źūźĒź╗ź├źĄżŽźėźĖź═ź╣Ę┴▌åżŌČ\ĮčżŌĮjżŁż»╩čż’żļĪŻżĮż╬╩č╦Ųż╬══╗ęż“żĄżķż╦┼┴ż©żŲżżż»ĪŻØiövż╬╬ŃżŽź▐źļź┴ź│źóźūźĒź╗ź├źĄż╬│½╚»ż“│┌ż╦ż╣żļż┐żßż╬ź─Ī╝źļżŪżóż├ż┐ż¼Īó║ŻövżŽźóźūźĒĪ╝ź┴ż╬░█ż╩żļźūźĒź╗ź├źĄż╬╬Ńż“Ų¾ż─Šę▓ż╣żļĪŻ▐kż─żŽź©źĖź¾źąźķż½żķĪóżŌż”▐kż─żŽź▒ź¾źųź├źĖż½żķÖ┌ż▐żņż┐źūźĒź╗ź├źĄżŪĪóČ”ż╦źóĪ╝źŁźŲź»ź┴źŃż¼ż│żņż▐żŪ┐╩ż¾żŪżŁż┐öĄ╦Īż╚░Ńż”ĪŻ

ź└źżź╩ź▀ź├ź»ż╦╠┐╬ßż“╩čż©żķżņżļSpiral Gatewayż╬źóĪ╝źŁźŲź»ź┴źŃ

ź©źĖź¾źąźķĮj│žż“ź╣źįź¾ź¬źšżĘżŲ└▀╬®żĘż┐Spiral GatewayżŽĪóĘ╚┬ė┼┼ÅBĄĪż╦┼ļ║▄żĄżņżŲżżżļź½źßźķż╬└Łē”ż“æųż▓żļż┐żßż╬┐«ęÄĮĶ═²ż“Š}²Xż▒żļźĻź│ź¾źšźŻź«źÕźķźųźļż╩źūźĒź╗ź├źĄż“│½╚»żĘż┐ĪŻCĖ└ĖņżŪźūźĒź░źķźÓżŪżŁĪóżĘż½żŌ▓ĶćĄĮĶ═²ż╣żļż╬ż╦Ø▓╩¼ż╩150Gopsż╚żżż”└Łē”ż“Ęeż├żŲżżżļĪŻ

ż│żņż▐żŪĘ╚┬ėź½źßźķż╬┐«ęÄĮĶ═²övŽ®żŽASICżŪż╩ż▒żņżąźĻźóźļź┐źżźÓż╦ĮĶ═²żŪżŁż╩ż½ż├ż┐ĪŻżĘż½żĘĪóźŪĪ╝ź┐źčź╣ż“╩čż©żļż│ż╚żŽżŪżŁż╩żżæųż╦Īóźóźļź┤źĻź║źÓż“»éżßżļż▐żŪż╦╗■┤ųż¼ż½ż½żļĪó┐ʿʿżĄĪē”ż“╝{▓├żŪżŁż╩żżĪóż╩ż╔ż╬╠õ¼öż¼żóż├ż┐ĪŻż│żņż“DSPżŪ╝┬╣įżĘżŲźóźļź┤źĻź║źÓż“śŗ┐Ęż╣żļż╚żżż”Š}żŽżóżļż¼ĪóźĻźóźļź┐źżźÓĮĶ═²żŪżŁż║Īóż▐ż┐źšźņĪ╝źÓźąź├źšźĪźßźŌźĻżŌØŁ═ūż╦ż╩żļĪŻ

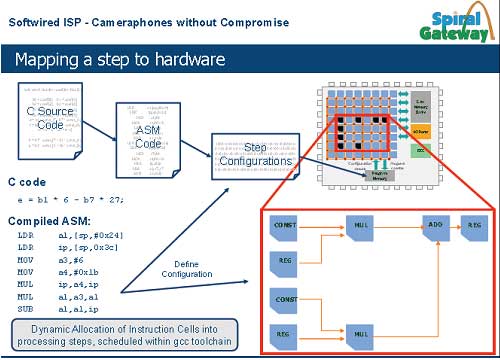

ż│ż╬┐ʿʿżźūźĒź╗ź├źĄRICAĪ╩Reconfigurable Instruction Cell ArrayĪ╦żŽ╠┐╬ßź╗ź├ź╚ż“śOĮyż╦╩čż©żķżņżļ▓ĶćĄĮĶ═²źūźĒź╗ź├źĄISPĪ╩image signal processorĪ╦żŪżóżļĪŻRICAż╬├µ▒¹ż╦żŽ╠┐╬ßź╗ź├ź╚ż╬ź╗źļż¼│╩╗ęėXż╦╩┬ż┘żķżņĪóżĮżņżŠżņż“Ū█└■żŪ±Tż┘żļżĶż”ż╦ż╩ż├żŲżżżļĪŻ╠┐╬ßź╗ź├ź╚ż¼źŽĪ╝ź╔ź”ź©źóż╚żĘżŲ─Š└▄ż─ż╩ż¼żĻ╝┬╣įż╣żļĪŻź│ź¾źčźżźķżŽCź│Ī╝ź╔ż“ź▐ź├źįź¾ź░żĘżŲĪó╝┬╣įżĘż┐żż╠┐╬ßź╗ź├ź╚ż╬ź╗źļż“└▄¶öż╣żļĪųź═ź├ź╚źĻź╣ź╚Īūż“ķWż»ż╚żżż”ż’ż▒ż└ĪŻź═ź├ź╚źĻź╣ź╚Š╩¾ż“źóźūźĻź▒Ī╝źĘźńź¾ż┤ż╚ż╦╝ĪĪ╣ż╚├▀└čżĘżŲż¬żŁĪóźūźĒź░źķźÓż╬╬«żņż╦“£ż├żŲźĻźóźļź┐źżźÓż╦ź│Ī╝ź╔ż“╝┬╣įż╣żļĪŻ1Ė─ż╬ź╗źļż╦żŽ1Ė─ż╬╠┐╬ßż“Ų■żņżŲż¬ż»ĪŻź═ź├ź╚źĻź╣ź╚Š╩¾ż“ż▐ż╚żßżŲźšźķź├źĘźÕźßźŌźĻĪ╝ż╩ż╔źūźĒź░źķźÓźßźŌźĻĪ╝ż╦├▀ż©żŲż¬ż▒żążżżżĪŻ

ż│ż”żżż├ż┐ĪųźĮźšź╚ź’źżźõĪ╝ź╔Īūż╬żĶż”ż╩źūźĒź╗ź├źĄż¼Įą═Ķæųż¼żļĪŻż▐żļżŪASICż╬ź═ź├ź╚źĻź╣ź╚ż¼ź¬ź¾źŪź▐ź¾ź╔żŪ└▄¶öżĄżņżŲżżż»ż╬żŪĪóźĻźóźļź┐źżźÓż╦╣Į└«ż“╩čż©żķżņżļż╚żżż”Ślż└ĪŻźŽĪ╝ź╔ź”ź©źóżžż╬ź▐ź├źįź¾ź░żŽĪó╝Īż╬żĶż”ż╦ż╣żļĪŻż╣ż╩ż’ż┴ĪóCź│Ī╝ź╔ż“źóź╗ź¾źųźĻź│Ī╝ź╔ż╦ź│ź¾źčźżźļżĘĪó╠┐╬ßż╬Įń▀Mż“ź╣ź╚źóżĘżŲżżżļźūźĒź░źķźÓźßźŌźĻĪ╝ż½żķŲDżĻĮąż╣ĪŻż│żņż└ż▒ż└Ī╩┐▐4Ī╦ĪŻ

┐▐4ĪĪRICAż╬┤╦▄╣Į└«ż╚ź▐ź├źįź¾ź░╦Ī

źĻźóźļź┐źżźÓżŪź═ź├ź╚źĻź╣ź╚ż“╩čż©ĪóźŪĪ╝ź┐ż“╣ŌÅ]ĮĶ═²ż╣żļż┐żßż╦Īó╠┐╬ßż╬╬«żņż“źčźżźūźķźżź¾ż╚żĘżŲżĮżņż“3ż─ż╦╩¼ż▒Īóź░źļĪ╝źūż┤ż╚ż╦╩┬š`ĮĶ═²ż╣żļż╚żżż”źóĪ╝źŁźŲź»ź┴źŃż“Īó╬Ńż©żąHDźėźŪź¬ż“„[─ĻżĘżŲ╗╚ż├żŲżżżļĪŻż─ż▐żĻ200╦³▓Ķ┴Ū/źšźņĪ╝źÓż╬▓Ķ楿“1╔├┤ųż╦30źšźņĪ╝źÓĮĶ═²ż╣żļż╚żĘżŲĪó60M▓Ķ┴Ū/╔├ż╬└Łē”ż“„[─ĻżĘżŲżżżļĪŻ╝ŖōQē”╬üż╚żĘżŲżŽ150Gopsżóżļż╚żżż”ĪŻ

źŪźĖź½źßż╦ØŁ═ūż╩ĄĪē”ż“ż╣ż┘żŲĪó╠┐╬ßź╗ź├ź╚ż╚ĪóźūźĒź░źķźÓźßźŌźĻĪ╝ż╦°QżßżŲż¬ż▒żąźĻźóźļź┐źżźÓżŪĄĪē”ż“╝ĪĪ╣ż╚╩čż©żķżņżļĪŻHDźėźŪź¬ż“ż╚żķż©ż┐żĻĪóźėźÕĪ╝źšźĪźżź¾ź└Ī╝ż“ż╬żŠż»źŌĪ╝ź╔ż“ż─ż▒żļż│ż╚żŌżŪżŁżļĪŻźūźĒź░źķźÓźßźŌźĻĪ╝ż“źšźķź├źĘźÕż╦żĘżŲż¬ż▒żąźŪźĖź½źßĄĪē”Ī╩źĮźšź╚ź”ź©źóĪ╦ż╬źóź├źūź░źņĪ╝ź╔żŽż┤ż»į~├▒ż╩ż”ż©ĪóŲ▒żĖźĘźĻź│ź¾æųż╦╩╠ż╬×æēäż“║▄ż╗żļż│ż╚żŌżŪżŁżļĪŻ

RICAźūźĒź╗ź├źĄż╦żŽ║ŪĮj600╠┐╬ßż“Ų▒╗■ż╦ĮĶ═²ż╣żļ«Ć╩┬š`źūźĒź╗ź├źĄż“└čż¾żŪżżżļżĶż”ż╩żŌż╬ż└Īóż╚Ų▒╝ęCEOż╬Graham TownsendĢ■żŽ┼┼ÅBźżź¾ź┐źėźÕĪ╝ż╦ż¬żżżŲż│ż╬żĶż”ż╦Įęż┘ż┐ĪŻż│ż╬źĮźšź╚ź”ź©źóISPżŽź½źßźķźšź®ź¾ż╬ĄĪē”ż“śOĮyż╦╩čż©żŲżżżĒżżżĒż╩źŌĪ╝ź╔ż¼╗╚ż©żļżĶż”ż╦żŪżŁżļĪŻ╬Ńż©żąźėźŪź¬żŪż╬ź╣ź╚źĻĪ╝ź▀ź¾ź░źŌĪ╝ź╔ż“░Ńż”źóźļź┤źĻź║źÓżŪ║▄ż╗ż┐żĻĪóżóżļżżżŽźšźņĪ╝źÓźņĪ╝ź╚ż“╩čż©ż┐żĻż╣żļż│ż╚ż¼żŪżŁżļĪŻ│░¤²ż▒ż╬źßźŌźĻĪ╝żŽ512Mźėź├ź╚ż╬DDRżóżļżżżŽDDR2ż¼żóżņżąØ▓╩¼ż╩ż╬żŪź│ź╣ź╚żŽŖWż»żŲ║čżÓĪŻżŌż┴żĒż¾Ī󿥿▐żČż▐ż╩ĄĪē”ż“│╚─źżĘżŲĪóźßźŌźĻĪ╝źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“¤²ż▒ż┐żĻĪóźėźŪź¬ź│Ī╝źŪź├ź»ż“┼ļ║▄żĘż┐żĻĪó─╠┐«źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“¤²ż▒ż┐żĻĪóż╣żļż│ż╚żŌżŪżŁżļĪŻ

ź’źżźõźņź╣▒■├ōż“┴└ż├ż┐«Ć─ŃŠ├õJ┼┼╬üż╬źūźĒź╗ź├źĄ

╚ŠŲ│öüČ\Įčż½żķź’źżźõźņź╣─╠┐«Īóź╗ź¾źĄĪ╝ĪóöUĖµČ\Įčż“└▀╝Ŗż╣żļźšźĪźųźņź╣ż╬Cambridge Consultants╝꿎«Ć─ŃŠ├õJ┼┼╬üżŪ─╠┐«ż“╣įż”ĪóNFCżõZigBeeĪóBluetoothż╩ż╔ż╬▒■├ōż“┴└ż├ż┐16źėź├ź╚XAP5źūźĒź╗ź├źĄź│źóż“│½╚»żĘż┐ĪŻż│żņżŽĪó▒č╣±ż╬ź©źņź»ź╚źĒź╦ź»ź╣ŠÅČ╚ż╬┐═╠«║ŅżĻż╦╣ūĖźż╣żļKTNĪ╩Knowledge Transfer NetworkĪ╦ż¼╝ń╠¢żĘż┐ĪóPower Downź╗ź▀ź╩Ī╝ż╦ż¬żżżŲ╚»╔ĮżĘż┐żŌż╬ĪŻ║Żövż╬┼²▐kźŲĪ╝ź▐żŽĪóNew trends, technology & start-up opportunities in low power silicon & system designĪ╩─ŃŠ├õJ┼┼╬ü╚ŠŲ│öüż╚źĘź╣źŲźÓ└▀╝Ŗż╦ż¬ż▒żļ┐ʿʿżź╚źņź¾ź╔ż╚Č\ĮčĪóź┘ź¾ź┴źŃĪ╝ż╬ż┐żßż╬ź╗ź▀ź╩Ī╝Ī╦żŪżóżļĪŻ

Cambridge╝ęż╬źūźĒź╗ź├źĄż╬▒■├ōż╦żŽ╝Īż╬żĶż”ż╩żŌż╬ż¼żóżļĪŻ╬Ńż©żąLiź▄ź┐ź¾┼┼├ėżŪ10ŃQ┤ųŲ»żŁ¶öż▒żļ▒■├ōżŪżŽ╩┐Čč┼┼╬«żŽ1”╠AĪó├▒3ė|┼┼├ėżŪ15ŃQ┤ųŲ»żŁ¶öż▒żļ▒■├ōżŪżŽ╩┐Čč┼┼╬«żŽ15”╠Aż¼żĮżņżŠżņ║ŪĮjż╚Ė½żļ└▀╝Ŗż“żĘż╩ż▒żņżąż╩żķż╩żżĪŻż│ż│żŪżŽżĮż╬żĶż”ż╩╚∙╝Õż╩┼┼╬«żŪŲ░║Ņż╣żļź╗ź¾źĄĪ╝ź═ź├ź╚ź’Ī╝ź»żõźóź»ź┴źÕź©Ī╝ź┐ż“Ņ~Ų░ż╣żļSoCżõSiPż╦┴╚ż▀╣■żÓź│źóż╦╗╚ż”ĪŻ┐▐5żŽSoCżŪ╗╚ż”╬ŃżŪżóżļĪŻ

┐▐5ĪĪXAP5ź│źóż“SoCż╦ĮĖ└čżĘż┐╬Ń

┼┼╬üżõź¼ź╣ż╬źßĪ╝ź┐Ī╝ĖĪ┐╦ż“śOŲ░┼¬ż╦╣įż”▒■├ō╬ŃżŪżŽĪóźŪĪ╝ź┐┴„┐«żŽ24╗■┤ųż╦▐kövżŪĪóżĮżņ░╩│░żŽĪó─ŃżżźŪźÕĪ╝źŲźŻźņźĘź¬żŪźŪĪ╝ź┐ż“╩ß┬¬żĘ├▀└čżĘżŲż¬ż»ĪŻż│ż╬Šņ╣ńĪóĮjŗ╩¼ż╬╗■┤ųżŽź¬źšėX▌åż╦żóżĻĪóźŪĪ╝ź┐ż“╩ß┬¬ż╣żļż╚żŁż└ż▒100”╠Aµć┼┘╬«żĘĪó1Ų³▐kövż╬źŪĪ╝ź┐┴„┐«ż╦żŽ20mAż“╬«ż╣ĪŻ╗■┤ų┼¬ż╦ź¬źšėX▌åż¼░Ą┼▌┼¬ż╦─╣żżżĶż”ż╦żĘżŲż¬ż»ż┐żß╩┐Čč┼┼╬«ż¼1~10”╠Aż╚─ŃżżŲ░║Ņż¼▓─ē”ż╦ż╩żļĪŻ┼┼░ĄżŽ1.2VżóżļżżżŽ1.8Vż╦ż╣żļĪŻźßźŌźĻĪ╝żŽ▒■├ōż╦żŌżĶżļż¼64KB(źąźżź╚)ż╬RAMĪó1KBż╬ROMż╩ż╔ż“├ō┴Tż╣żļĪŻźŪĪ╝ź┐ż“╩▌Ęeż╣żļRAMż╚żĘżŲżŽ╔įĦ╚»└ŁRAMżŪżŌżĶżżżĘĪóżóżļżżżŽRAMźŪĪ╝ź┐ż“╩▌┘Tż╣żļźšźķź├źĘźÕż“╝{▓├żĘżŲżŌżĶżżĪŻż┐ż└żĘĪ󟔟¦Ī╝ź»źóź├źūėX▌åż½żķ┴Ū┴ßż»╬®ż┴æųż¼żņżļżĶż”ż╦źņźżźŲź¾źĘĪ╝ż╬ø]żż╣Į└«ż╦ż╣żļĪŻ

ż│ż”żżż├ż┐▒■├ōż╦═ūĄßżĄżņżļźūźĒź╗ź├źĄż╚żĘżŲżŽĪ󊻿╩żżźĮźšź╚ź”ź©źóżŪż╣żÓżĶż”ż╦ź│Ī╝ź╔Ė·╬©ż“╣Ōż»ż╣żļż│ż╚ż¼ØŁ═ūż╚ż╩żļĪŻź│Ī╝ź╔/źŪĪ╝ź┐żŽźµĪ╝źČĪ╝├ōż╚═ź└Ķ├ōż╚ż“╩¼ż▒żŲż¬ż»ĪŻżĘż½żŌOSżõ─╠┐«źūźĒź╚ź│źļź╣ź┐ź├ź»ĪóźĮźšź╚ź”ź©źóż╬źóź├źūź░źņĪ╝ź╔ż╩ż╔żŌźĄź▌Ī╝ź╚ż╣żļØŁ═ūż¼żóżļĪŻ

║Żöv│½╚»żĘż┐XAP5źūźĒź╗ź├źĄź│źóżŽĪóźßźŌźĻĪ╝źóź╔źņź╣ȧ┤ųż╬ż▀24źėź├ź╚żŪ║ŪĮj16MBż▐żŪż╬źßźŌźĻĪ╝ż“╗╚ż©żļżĶż”ż╦żĘżŲżżżļ┼└░╩│░żŽĪóźŪĪ╝ź┐╔²ĪóźņźĖź╣ź┐╔²ż╩ż╔żŽ16źėź├ź╚ż╦ż╣żļĪŻ130nmźūźĒź╗ź╣żŪ║Ņ×æżĘż┐ź│źóż╬ĀC└迎0.09 mm2░╩▓╝Īó1╦³8000ź▓Ī╝ź╚┴Ļ┼÷ż└ż╚żżż”ĪŻź└źżź╩ź▀ź├ź»ż╩Š├õJ┼┼╬üżŽ27”╠W/MHzżŪĪóŠ├õJ┼┼╬ü┼÷ż┐żĻż╬└Łē”żŽ25,000MIPS/WĪŻ

źūźĒź╗źĄIPżŽVerilog RTLż╚żĘżŲźĮźšź╚ź│źóżŪźķźżź╗ź¾ź╣ż╣żļĪŻBluetoothżŪ║ŪĮjż╬▌xŠņźĘź¦źóż“É█żļCSR╝꿎ż│ż╬XAPźóĪ╝źŁźŲź»ź┴źŃż“ż╚żļĪŻŲ▒╝꿎Cambridge Consultantsż½żķź╣źįź¾ź¬źšżĘżŲ└▀╬®żĄżņż┐ĪŻźĮźšź╚ź”ź©źóż╬│½╚»┤─ČŁż╚źŪźąź├ź░┤─ČŁżŌź─Ī╝źļż“├ō┴TżĘżŲż¬żĻxIDEż╚żżż”ć@Š╬żŪ╚╬Ūõż╣żļĪŻŠ▄║┘żŽĪóŲ▒╝ęź█Ī╝źÓź┌Ī╝źĖż╬XAPźūźĒź╗ź├źĄż“╗▓Š╚ĪŻ