ŠåÅ]ż╦╣Łż¼ż├żŲżżżļź¬Ī╝źūź¾ź╣ź┐ź¾ź└Ī╝ź╔ż╬RISC-Vź│źó

RISC-VĪ╩źĻź╣ź»źšźĪźżźųż╚╚»▓╗Ī╦ż¼ŠåÅ]ż╦╣Łż▐ż├żŲżŁż┐ĪŻźŪĪ╝ź┐ź╗ź¾ź┐Ī╝Ė■ż▒ż╬źóź»ź╗źķźņĪ╝ź┐żõAIź┴ź├źūĪóź╗źŁźÕźĻźŲźŻäė▓ĮĘ┐ż╬źóĪ╝źŁźŲź»ź┴źŃĪ󟻟ļź▐├ōź│ź¾źįźÕĪ╝ź┐ż╬źūźķź├ź╚źšź®Ī╝źÓĪóżóżļżżżŽź▐źżź│ź¾ż╩ż╔żĄż▐żČż▐ż╩ź│ź¾źįźÕĪ╝ź┐ż╬źūźķź├ź╚źšź®Ī╝źÓż╚żĘżŲ╣Łż¼żĻż“Ė½ż╗żŲżżżļĪŻź¬Ī╝źūź¾ź╣ź┐ź¾ź└Ī╝ź╔żŽ║¼öfż╦żóżļż½żķż└ĪŻ

ź│ź¾źįźÕĪ╝ź┐żŽĪó┤╦▄┼¬ż╦▐kż─ż╬źŽĪ╝ź╔ź”ź©źóźūźķź├ź╚źšź®Ī╝źÓż“║ŅżĻĪóżĮż╬æųżŪźĮźšź╚ź”ź©źóżŪ║╣╩╠▓Įż“┐▐żļź▐źĘź¾żŪżóżļĪŻĪųź¬Ī╝źūź¾ź╣ź┐ź¾ź└Ī╝ź╔ż╬æä│╩ż“Č”ż╦║Ņżļ┐═ż┐ż┴ż╬╗@┐└ż¼RISC-Vż╦żŽżóżļĪūĪŻż│ż”Ėņżļż╬żŽRISC-V Internationalż╬Ų³╦▄┬Õ╔ĮżŪżóżļąQ║ĻĮė╩┐Ģ■ĪŻŲ▒Ģ■żŽż½ż─żŲŲ³╬®×æ║ŅĮĻżŪSHź▐źżź│ź¾ż“│½╚»żĘżŲżżż┐ź╚ź├źūź©ź¾źĖź╦źóż└ĪŻ

RISC-VźóĪ╝źŁźŲź»ź┴źŃżŪźŪĪ╝ź┐ź╗ź¾ź┐Ī╝Ė■ż▒ż╬ź│ź¾źįźÕĪ╝ź┐ź┴ź├źūż“│½╚»żĘżŲżżżļEsperantożõTenstorrentż╬┴└żżżŽĪóNvidiaż╬GPUż╬1/10Ī┴1/4ż╚żżż”─ŃżżŠ├õJ┼┼╬üż╬AIź┴ź├źūż╬│½╚»ż“ų`╗žż╣ż┐żßż└ĪŻĪų║Ū└Ķ├╝ż╬GPUżŪżóżļH100ź┴ź├źūż“żŌżĘ100╦³Ė─╗╚ż├ż┐żķÖ┌└«AIźĘź╣źŲźÓż╬Š├õJ┼┼╬üżŽż┘żķż▄ż”ż╦ĮjżŁż»ż╩żĻĪóĖČ╚»1┤żõ2┤żŪżŽ×┤▒■żŪżŁż╩ż»ż╩żļĪūż╚ąQ║ĻĢ■żŽĖ└ż”ĪŻż│żņżŽ2Ī┴3ŃQ└Ķż╦żŽĖĮ╝┬┼¬ż╦ż╩ż├żŲż»żļĪŻ

żŌż╚żŌż╚RISC-VżŽĪóź½źĻźšź®źļź╦źóĮj│žźąĪ╝ź»źņźżē“ż╬David PattersonČĄĶbż╚Krste AsanovichČĄĶbż½żķ│½╚»żĘż┐źšźĻĪ╝ż╬CPUź│źóżŪżóżĻĪóGitHubż╦żŌ┼ąŹ{żĄżņż┐ź¬Ī╝źūź¾ż╩CPUźóĪ╝źŁźŲź»ź┴źŃżŪżóżļĪŻżĘż½żŌ╠┐╬ßź╗ź├ź╚żŽ╦▄═Ķż╬RISCźóĪ╝źŁźŲź»ź┴źŃż╬żĶż”ż╦47╠┐╬߿ʿ½ż╩żżĪŻż│żņż╦ź½ź╣ź┐źÓ╠┐╬ßż“╝{▓├ż╣żļż╬żŪżóżļĪŻż│ż╬ż┐żßĪóź½ź╣ź┐źÓCPUż“└▀╝ŖżĘżõż╣żżĪŻż╣żŪż╦źļź═źĄź╣żŽŲ╚śO└▀╝Ŗż╬RISC-V CPUź│źóż“│½╚»żĘĪóSoCż“└▀╝ŖżĘżŲżżż»źņź┘źļż╦├ŻżĘżŲżżżļĪŻ

2024ŃQ1ĘŅ├µ║óĪó┼ņ»BĮj│žżŪ│½╠¢żĄżņż┐RISC-V DayżŪżŽĪóRISC-Vż“Š}²Xż▒żŲżżżļżĄż▐żČż▐ż╩┤ļČ╚ż¼┼ąŠņżĘż┐ĪŻźŪĪ╝ź┐ź╗ź¾ź┐Ī╝Ė■ż▒ż╬źóź»ź╗źķźņĪ╝ź┐ż“│½╚»żĘżŲżżżļVentana Micro Systems╝꿎ĪóRISC-Vż╬CPUź│źóż└ż▒żŪżŽż╩ż»ź┴ź├źūźņź├ź╚żõSoCżŌ│½╚»żĘżŲżżżļĪŻ2018ŃQż╦└▀╬®żĄżņĪóźĘźĻź│ź¾źąźņĪ╝ż╦Ą“┼└ż“Åøż»Ų▒╝ęż╬├µ│╦źßź¾źąĪ╝żŽArmż╬64źėź├ź╚źóĪ╝źŁźŲź»ź┴źŃż“│½╚»żĘżŲżŁż┐ź©ź¾źĖź╦źóĮĖ├─ż└ĪŻ

ź┴ź├źūźņź├ź╚ż“Ū░Ų¼ż╦Åøż»ź╣ź┐Ī╝ź╚źóź├źūżŪżóżļż½żķż│żĮĪóź└źż2ź└źżĪ╩D2DĪ╦ż╚żżż├ż┐3D-ICż╬źżź¾ź┐Ī╝źšź¦Ī╝ź╣ż“║ŅżĻĪóź┴ź├źūźņź├ź╚ż╬║YØŹæä│╩ż“ų`╗žż╣UCIeż╦ØŹĄ“ż╣żļź┴ź├źūźņź├ź╚ż“─¾ČĪżŪżŁżļżĶż”ż╦ż╣żļĪŻ┴└żżżŽżõżŽżĻAIżŪĪóÖ┌└«AIż½żķź©ź├źĖAIż▐żŪż“ź½źąĪ╝ż╣żļĪŻĖĮ║▀4nmźūźĒź╗ź╣żŪ└▀╝Ŗż╣żļCPUź│źóĪųVeyron 2Īūż“│½╚»├µż└ĪŻ AMDż╬EPYCźĘźĻĪ╝ź║żõIntelż╬XeonĪóArm 64żĶżĻżŌŠ├õJ┼┼╬ü┼÷ż┐żĻż╬└Łē”ż“æųż▓żļ└▀╝Ŗż╚ż╩ż├żŲżżżļĪŻGPUżŌ┼ļ║▄żŪżŁżļżĶż”ż╦Č”Ń~źŁźŃź├źĘźÕż╬ź│źęĪ╝źņź¾źĘĪ╝Ī╩CPUżŌGPUżŌŲ▒żĖźßźŌźĻż“źóź»ź╗ź╣żŪżŁżļż│ż╚Ī╦ż“╣ŌżßĪóź│źęĪ╝źņź¾ź╚ż╩NoCĪ╩Network on ChipĪ╦źąź╣żŪ192ź│źóż“Ų░║ŅżŪżŁżļĪŻ

ÜW║═CPUźŪźČźżź╩Ī╝ż╬Jim Keller╬©żżżļTenstorrentżŽĪóJimż╚Ų▒══AppleżŪSoCĪųAźĘźĻĪ╝ź║Īūż“└▀╝ŖżĘżŲżżż┐Wei-han LienĢ■ż¼ź┴Ī╝źšCPUźóĪ╝źŁźŲź»ź╚Ę¾źĘź╦źóźšź¦źĒĪ╝ż╚żĘżŲ╣ų▒ķżĘż┐ĪŻĪųż╩ż╝RISC-Vż½Īūż╚żżż”╠õżżż╦×┤żĘżŲ░╩▓╝ż╬żĶż”ż╦Ėņż├żŲżżżļĪŻĪųĘQ╣±ż╬└ņ╠ń▓╚ż╚ÅBż“żĘżŲżŁżŲ╚ŠŲ│öüżŽČ╦żßżŲ─_═ūż╩ŗēäżŪżóżļż╚żżż”Ū¦╝▒żŪ▐k├ūżĘż┐ĪŻCPUżŽ┐Õżõ┼┼Ążż╚Ų▒żĖżĶż”ż╩źżź¾źšźķż╦ż╩ż├ż┐ĪŻżĘż½żŌAIżŽ║ŻĖÕżĄż▐żČż▐ż╩ż╚ż│żĒż╦╣Łż¼żļ─_═ūż╩Č\ĮčżŪżóżļż½żķĪóAI+CPUż╬╚ŠŲ│öüź┴ź├źūż“║Ņżļż│ż╚ż“ų`╗žżĘżŲżżżļĪŻżĮżņżŌ├▒▓┴10ź╔źļż╚Č╦żßżŲŖWżżź┴ź├źūż“ų`╗žż╣ĪŻżĮżĘżŲĪóAI+CPUź┴ź├źūżŽź©ź├źĖż½żķźŽźżź©ź¾ź╔ż▐żŪź½źąĪ╝ż╣żļż┐żßRISC-Vż¼║Ū┼¼ż└ĪūĪŻ

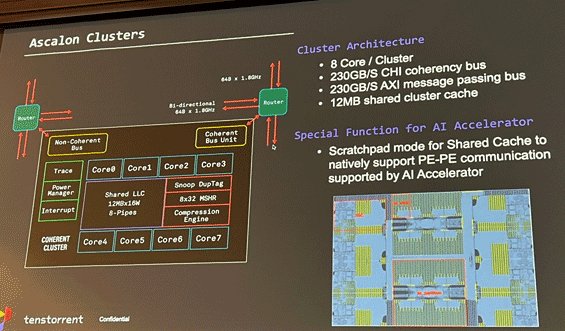

┐▐1ĪĪTenstorrentż╬╣Ō└Łē”ż╩RISC-Vź│źóAscalon

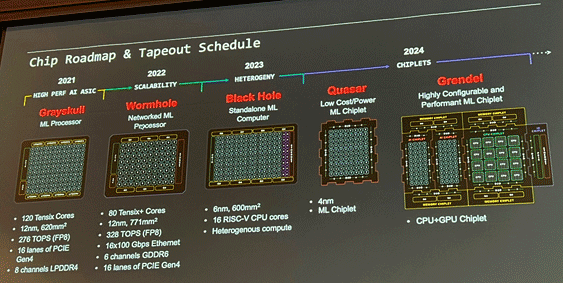

ĖĮ║▀Īó╣Ō└Łē”ż╩RISC-Vź│źóż╚żĘżŲAscalonż“└▀╝ŖĪ╩┐▐1Ī╦Ī󿥿ķż╦─ŃŠ├õJ┼┼╬üż╬4nmź┴ź├źūźņź├ź╚Quasarż╚ĪóCPU+GPUż╬ź╣ź▒Ī╝źķźųźļż╩ź┴ź├źūźņź├ź╚ż╚żĘżŲGrendelż“│½╚»├µżŪĪ╩┐▐2Ī╦Īó║ŻŃQ┼┘¼Źż╦źŲĪ╝źūźóź”ź╚ż╣żļ═Į─Ļż└ĪŻ¾H┐¶ż╬IPź│źóż“└▄¶öżŪżŁżļżĶż”ż╦ż╣żļż┐żßNoCź▐ź═Ī╝źĖźŃĪ╝ż“└▀╝ŖĪóTexsixź│źó1Ė─ż½żķ┐¶╗hź┴ź├źūż▐żŪ│╚─źżŪżŁżļżĶż”ż╦Ų■Įą╬üż“└▀╝ŖżĘżŲżżżļĪŻLienĢ■ż╦źėźĖź═ź╣źŌźŪźļż╦ż─żżżŲä®╠õż╣żļż╚Īó┼÷╩¼żŽCPU+AIź┴ź├źūźņź├ź╚ż“ź┴ź├źūźņź├ź╚żõź┴ź├źūźėźĖź═ź╣ż╬│╦ż╚ż╣żļż¼ĪóĮø═ĶżŽĪ╩żŌż├ż╚AIźŌźŪźļż╬│žØ{ż“ø]Į╠żŪżŁżļĪ╦ź│ź¾źŪźŻźĘźńź╩źļź│ź¾źįźÕĪ╝źŲźŻź¾ź░Ī╩ź═ź├ź╚ź’Ī╝ź»ż╬▐kŗż└ż▒ż“┬ō┘IżĘżŲŲ░║ŅżĄż╗żļź│ź¾źįźÕĪ╝źŲźŻź¾ź░Š}╦ĪĪ╦ż╦┐╩żÓż└żĒż”ż╚┼·ż©ż┐ĪŻ

┐▐2ĪĪTenstorrentż╬CPU+GPUź│źóż╬Grendel

EDAż╬ź╚ź├źūź┘ź¾ź└Ī╝żŪżóżļSynopsysżŽ║ŪŖZĪóImperasż“āA╝²ĪóRISC-VČ\Įčż“Š}ż╦Ų■żņż┐ĪŻ░╩Øiż╦āA╝²żĘż┐ARC International╝ęż╬CPUź│źóż╦▓├ż©ĪóARC╠┐╬ßż“│╚─ź╠┐╬ßż╦▓├ż©ż┐RISC-VźąĪ╝źĖźńź¾żŌ─¾ČĪżĘ╗Žżßż┐ĪŻ

├µ╣±ż╬źšźĪźųźņź╣GagaDevice╝꿎ż│żņż▐żŪArmź┘Ī╝ź╣ż╬ź▐źżź│ź¾ż“└▀╝ŖżĘżŲżŁż┐ż¼Īóż│ż│ż╦RISC-Vź│źóżŌ×æēäź▌Ī╝ź╚źšź®źĻź¬ż╦▓├ż©ż┐ĪŻRISC-Vź▐źżź│ź¾żŽĪóķ]ŠĮź│ź¾ź╚źĒĪ╝źķżõź│Ī╝źęĪ╝ź▐źĘź¾Īó┼┼╗ęź┐źąź│ż╩ż╔░cÖ┌Ė■ż▒ż╬×æēäż¼¾Hżżż¼Īó║ŪŖZżŽśOŲ░┘Z┤žĘĖż╬Ė▄Ąęż¼╗\ż©żŲżŁż┐ż╚żĘżŲżżżļĪŻ

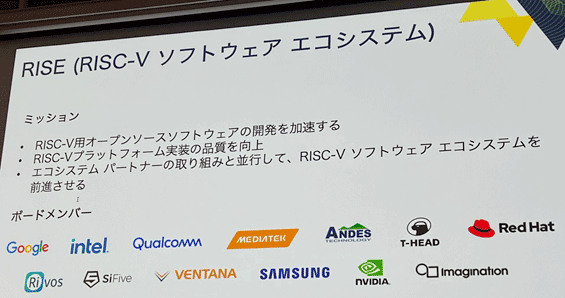

┐▐3ĪĪRISC-VĖ■ż▒źĮźšź╚ź”ź©źóż“│½╚»ż╣żļź©ź│źĘź╣źŲźÓRISEĪ╩RISC-V Software EcosystemĪ╦ĪĪLINUXźšźĪź¾źŪĪ╝źĘźńź¾ż╬źūźĒźĖź¦ź»ź╚ż╬▐kż─

Īųż│żņż½żķżŽRISC-Vż╬ź©ź│źĘź╣źŲźÓż“ż╔ż”╣Łż▓żŲżżż»ż½ż¼╠õż’żņżŲżżżļĪŻźĮźšź╚▓±╝ęĪ╩┐▐3Ī╦żõźšźĪź”ź¾ź╔źĻż╩ż╔ż╣żĮ╠Ņż“╣Łż▓żŲżżż»ż│ż╚ż¼╔ߥ┌ż╦ż─ż╩ż¼żļĪūĪóż╚┼ņĮjĮj│ž▒Ī╣®│žĖ”ē|▓╩źĘź╣źŲźÓźŪźČźżź¾Ė”ē|ź╗ź¾ź┐Ī╝Ę¾┼┼ĄĪÅU╣®│ž└ņŲłż╬├ė┼─öłČĄĶbżŽ─∙żßż»ż»ż├ż┐ĪŻ