źūźĒź░źķź▐źųźļż╩ź▀ź»ź╣ź╚źĘź░ź╩źļICż“Silegoż¼20▓»Ė─Įą▓┘

Š«żĄż╩źūźĒź░źķź▐źųźļźŪźąźżź╣ż╚żŌĖ└ż”ż┘żŁźóź╩źĒź░Ī”źŪźĖź┐źļ║«║▀ICĪ╩CMICĪ╦ż“źėźĖź═ź╣ż╚żĘżŲżżżļSilegoĪ╩źĘźņź┤ż╚╚»▓╗Ī╦Technology╝ęż¼ż│ż╬ż█ż╔ICĮą▓┘╩Å╝ŖżŪ20▓»Ė─░╩æųż“├Ż└«żĘż┐ĪŻCMICżŽźŪźŻź╣ź»źĻĪ╝ź╚ŗēäżõŠ«żĄż╩źóź╩źĒź░ŗēäż“1ź┴ź├źūż╦ż▐ż╚żßżŲĪóź▄Ī╝ź╔ĀC└čż“╣Łż▓ż┐żżĪóż╚żżż”ź╣ź▐Ī╝ź╚źšź®ź¾żõź”ź¦źóźķźųźļźŪźąźżź╣ż╬└▀╝ŖŪvż╦Ė■ż»ĪŻ

SilegożŽĪóźūźĻź¾ź╚övŽ®┤łæųż╦źŪźŻź╣ź»źĻĪ╝ź╚żõż┴żńż├ż╚żĘż┐źóź╩źĒź░ICż╩ż╔ż“1ź┴ź├źūż╦ż▐ż╚żßżļż╚żżż”×æēäż“ØŖ─╣ż╚żĘżŲż¬żĻĪóż│ż╬żĶż”ż╩×æēäż“CMICĪ╩Configurable Mixed signal ICĪ╦ż╚Ō}ż¾żŪżżżļĪŻ×æēäż╬░╠Åøż┼ż▒ż╚żĘżŲżŽĪóXilinxżõAlteraż╩ż╔ż╬Įjæä╠ŽFPGAż╚żŽ░ŃżżĪóLattice Semiconductorż╬Š«æä╠ŽFPGAż╚żŌ░Ńż”ĪŻFPGAżŽźŪźĖź┐źļźĒźĖź├ź»övŽ®ż“├µ┐┤ż╚żĘż┐źūźĒź░źķźÓ▓─ē”ż╩ICżŪżóżļż¼ĪóSilegoż╬ICżŽĪóźóź╩źĒź░żŌ┤▐żÓĪŻ

żĄżķż╦Īóźóź╩źĒź░övŽ®ż“źūźĒź░źķźÓżŪżŁżļCypress Semiconductorż╬pSoCĪ╩programmable SoCĪ╦ż╚żŌ░Ńż”ĪŻpSoCżŽ8źėź├ź╚░╩æųż╬ź▐źżź│ź¾ż╦źūźĒź░źķźÓżŪżŁżļ║YØŹźóź╩źĒź░övŽ®ż“ĮĖ└čżĘż┐ź┴ź├źūżŪżóżļż¼ĪóSilegoż╬CMICżŽź▐źżź»źĒźūźĒź╗ź├źĄż“╗╚ż’ż║ż╦ź╣źŲĪ╝ź╚ź▐źĘź¾żŪövŽ®ėX▌åż“╔ĮĖĮż╣żļĪŻźóź¾źūżõź│ź¾źčźņĪ╝ź┐Īó┤ØŹ┼┼░Ą╚»Ö┌▀_ĪóźĻź╗ź├ź╚ĪóADC/DACż╩ż╔║YØŹźóź╩źĒź░ż“ĮĖ└čżĘżŲżżżļż¼ĪóNVMĪ╩╔įĦ╚»└ŁźßźŌźĻĪ╦żŪövŽ®ż“źūźĒź░źķźÓż╣żļĪŻż─ż▐żĻĪó║YØŹźĒźĖź├ź»żŌ║YØŹźĻź╦źóĪó£pŲ░ŗēäżŌµ£żŲż│ż╬1ź┴ź├źūżŪź½źąĪ╝żŪżŁżļż│ż╚ż¼ØŖ─╣ż└ĪŻźŪźŻź╣ź»źĻĪ╝ź╚×æēä50~60Ė─ż“1ź┴ź├źūż╦ĮĖ└čżĘżŲżżżļż┐żßĪóźµĪ╝źČĪ╝ż╬źĘź╣źŲźÓBOMż“ź│ź╣ź╚ź└ź”ź¾żŪżŁżļĪŻ

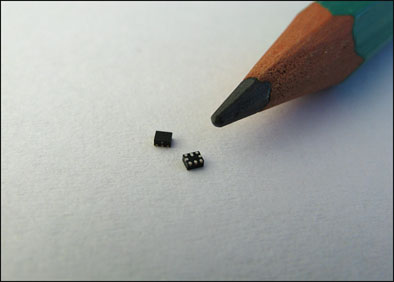

CMICż╬║Ū┐Ęż╬×æē俎GPAK5Ī╩ź░źĻĪ╝ź¾źčź├ź»5Ī╦źĘźĻĪ╝ź║ż╬×æēäż└(┐▐1)ĪŻżżż’żµżļŗī5└ż┬Õż╬źūźĒź░źķź▐źųźļGPAK×æēäżŪżóżĻĪóźŪźČźżź¾ź─Ī╝źļżŌ5└ż┬Õ╩¼ż╬└▀╝Ŗź─Ī╝źļż“źóź├źūźŪĪ╝ź╚żĘżŲżŁżŲżżżļĪŻż│ż╬┤ųĪó1300źŪźČźżź¾ż¼╬╠ŠÅżĄżņżŲżżżļż╚żżż”ĪŻ

┐▐1ĪĪ║ŪŖZż╬GPAK5źĘźĻĪ╝ź║ż╬ĪųSLG46108VĪū

GAPK5ż╬║ŪŖZż╬×æēä╬ŃżŪżóżļSLG46108V(┐▐1)żŽĪó1.0mmĪ▀1.2mmĪ▀0.55mmż╬6źįź¾Ī╩GPIOĪ╦ż╬STQFNż╬źčź├ź▒Ī╝źĖż╦░╩▓╝ż╬żĶż”ż╩ĄĪē”ż“ĮĖ└čżĘżŲżżżļĪ©

- 4Ė─ż╬LUT(źļź├ź»źóź├źūźŲĪ╝źųźļ)

- ┴╚ż▀╣ńż’ż╗ĄĪē”ż╬ź▐ź»źĒź╗źļ7Ė─Ī¦╬Ńż©żą┬ō┘I▓─ē”ż╩D-FF2Ė─/źķź├ź┴żóżļżżżŽ2źėź├ź╚ż╬LUTżõĪó┬ō┘I▓─ē”ż╩ź½ź”ź¾ź┐/źŪźŻźņźż1Ė─ż▐ż┐żŽ4źėź├ź╚LUTż╩ż╔

- │░ŗź»źĒź├ź»/źĻź╗ź├ź╚ż“×óż©ż┐8źėź├ź╚ż╬ź½ź”ź¾ź┐/źŪźŻźņźż3Ė─

- RC╚»┐Č▀_(25kHz/2MHz)

- źčź’Ī╝ź¬ź¾źĻź╗ź├ź╚

ż│ż”żżż├ż┐Š«æä╠Žż╬źūźĒź░źķź▐źųźļźŪźąźżź╣żŽĪó╝ńöüż╬ź▐źżź»źĒźūźĒź╗ź├źĄżõźóźūźĻź▒Ī╝źĘźńź¾źūźĒź╗ź├źĄĪóOSż╩ż╔ż“╩čż©ż║ż╦╝■╩šövŽ®ż“ź░źņĪ╝ź╔źóź├źūżĘż┐żĻĄĪē”ż“╝{▓├żĘż┐żĻż╣żļż┐żßż╦╗╚ż”ĪŻ╬Ńż©żąĪóź╣ź▐ź█ż╬żĶż”ż╦┐¶ź½ĘŅż┤ż╚ż╦ĄĪ¹|ż“źĻźĻĪ╝ź╣ż╣żļ×æēäżŪżŽĪóAPUżŌOSżŌżĮż╬ż▐ż▐żŪ╝{▓├ĄĪē”ż“ż│ż”żżż├ż┐źūźĒź░źķź▐źųźļźŪźąźżź╣żŪ╝┬ĖĮż╣żļĪŻż│ż╬ż┐żßĪóź╣ź▐ź█ż╩ż╔ż╬ź╗ź├ź╚źßĪ╝ź½Ī╝żŽźĒĪ╝ź╔ź▐ź├źūż“╬®żŲżŲ╝┬ĖĮżĘżõż╣żżĪŻ

SilegożŽĪóGPAKż╦▓├ż©Īóźčź’Ī╝MOSFETżŪżóżļGFETźĘźĻĪ╝ź║żõĪ󟻟Ēź├ź»╝■āS┐¶ż“╚»Ö┌ż╣żļGCLKźĘźĻĪ╝ź║ĪóQualcommż╬QC2.0ż“żŽżĖżßż╚ż╣żļŠåÅ]Į╝┼┼ź┴ź├źūż╩ż╔żŌ┬Ęż©żŲżżżļĪŻż▐ż┐ĪóGPAK6żŽ│½╚»├µżŪżóżļĪŻ