SamsungżŽ48┴ž256Gźėź├ź╚3╝ĪĖĄNANDż“╬╠ŠÅ│½╗Ž

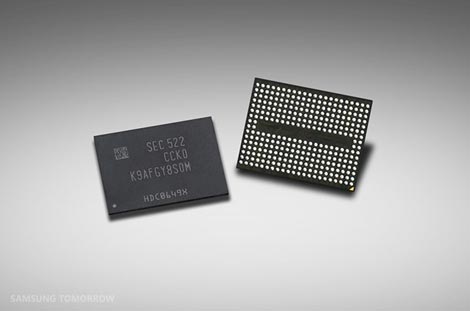

8ĘŅ4Ų³ż╦┼ņėøż¼48┴ž└č┴žż╬256Gźėź├ź╚3D NANDźšźķź├źĘźÕż╬│½╚»ż“źóź╩ź”ź¾ź╣żĘż┐╠└ĶĪóSamsungżŽŲ▒żĖżĶż”ż╦48┴žż╬256Gźėź├ź╚3D NANDźšźķź├źĘźÕż╬╬╠ŠÅż“╗Žżßż┐ż╚żżż”ź╦źÕĪ╝ź╣ż¼╚¶żė╣■ż¾żŪżŁż┐ĪŻä▌╣±źĄź¾ź┐ź»źķźķżŪ│½ż½żņż┐Flash Memory Summit 2015żŪ£½żķż½ż╦żĘż┐żŌż╬ĪŻ

┐▐1ĪĪSamsungż¼╚»╔ĮżĘż┐48┴ž3╝ĪĖĄNANDźšźķź├źĘźÕ×æēäĪĪĮąųZĪ¦Samsung Tomorrow

Samsungż╬ź┴ź├źūżŌ┼ņėøż╚Ų▒══Īó3źėź├ź╚/ź╗źļż╬48┴ž256Gźėź├ź╚(32Gźąźżź╚)NANDźšźķź├źĘźÕź┴ź├źūż└ż¼Īó┼ņėøż╬ź┴ź├źūżŽ9ĘŅż½żķźĄź¾źūźļĮą▓┘żŪżóż├ż┐(╗▓╣═½@╬┴1)ĪŻż│żņż╦×┤żĘżŲSamsungż╬ź┴ź├źūżŽ╬╠ŠÅ│½╗Žż╚ż╩ż├żŲż¬żĻĪó▐k╩Ō└Ķż¾żĖżŲżżżļĪŻ║“ŃQż╬8ĘŅĪóSamsungżŽ32┴žż╬3źėź├ź╚/ź╗źļ╣Įļ]ż╬128Gźėź├ź╚3╝ĪĖĄNANDźšźķź├źĘźÕż“╬╠ŠÅżĘ╗Žżßż┐ż¼Īó1ŃQĖÕż╦2Ū▄ż╬═Ų╬╠ż╬NANDźšźķź├źĘźÕż“×æēä▓ĮżĘż┐ż│ż╚ż╦ż╩żļĪŻź╗źļ╣Įļ]żŽĪó“£═Ķż╚Ų▒══Īó3D CTF (Charge Trap Flash)╣Įļ]ż“ŠW├ōĪŻ

Samsungż╦żĶżļż╚Īó“£═Ķż╬128Gźėź├ź╚ēäż╚╚µż┘ĪóŲ▒żĖźŪĪ╝ź┐╬╠ż“ź╣ź╚źóż╣żļż╬ż╦Š├õJ┼┼╬üżŽ30%║’žōżĄżņĪóÖ┌ŠÅ└ŁżŽ40%░╩æų╣Ōżżż╚żĘżŲżżżļĪŻż│ż╬±T▓╠ĪóSSDĪ╩╔wöüźŪźŻź╣ź»äóÅøĪ╦▌xŠņżŪż╬ź│ź╣ź╚Ēö┴Ķ╬üżŽĪó“£═ĶēäżĶżĻżŌ╣Ōż▐żļż╚żĘżŲżżżļĪŻ

SamsungżŽ“£═Ķż╬128Gźėź├ź╚×æēäżŪ2Tźąźżź╚SSDż“░cÖ┌├ōż╦Įą▓┘żĘżŲżżżļż¼Īóż│ż╬256Gźėź├ź╚ż╬┐Ę×æēäż“╗╚ż├ż┐SSDżŽĪó┤ļČ╚Ė■ż▒żõźŪĪ╝ź┐ź╗ź¾ź┐Ī╝ź╣ź╚źņĪ╝źĖĖ■ż▒ż╦Įj═Ų╬╠ż╬SSDż“╚╬Ūõż╣żļ═Į─Ļż└ĪŻż│ż│żŪżŽĪóPCIeĪóNVMeĪóSASźżź¾ź┐źšź¦Ī╝ź╣ż“┼ļ║▄ż╣żļ═Į─ĻżŪżóżļĪŻ

╗▓╣═½@╬┴

1. 48┴ž└č┴žźūźĒź╗ź╣ż“├ōżżż┐└ż─cĮķż╬256ź«ź¼źėź├ź╚3╝ĪĖĄźšźķź├źĘźÕźßźŌźĻĪųBiCS FLASHĪūż╬×æēä▓Įż╦ż─żżżŲ (2015/08/04)