╝Ī└ż┬ÕTFETĪóČ”╠─TFETĪófinFET×┤FDSOIż╩ż╔┐ĘźŪźąźżź╣ż¼ĮĖż▐ż├ż┐IEDM2013

IEEE IEDMĪ╩International Electron Device MeetingĪ╦żŪżŽĪóź╚ź¾ź═źļFETĪ╩TFETĪ╦ż“żŽżĖżßż╚ż╣żļ╝Ī└ż┬Õ╚ŠŲ│öüż╬╚»╔Įż¼żĄż▐żČż▐ż╩Ė”ē|ĮĻĪóĮj│žĪó┤ļČ╚ż½żķżóż├ż┐ĪŻTFETż╦żŽźĄźųź╣źņź├źĘźńźļź╔┼┼╬«ż╬’łŖAż“ŠåĮįż╦żŪżŁżļż╚żżż”źßźĻź├ź╚ż¼żóżļż┐żßĪóĘQ╝꿎ż│żņż“Ö┌ż½żĘĪó5nmź╬Ī╝ź╔ż“┴└żżĪó0.5V░╩▓╝ż╬┼┼Ė╗┼┼░Ąż“┴└ż”ĪŻ

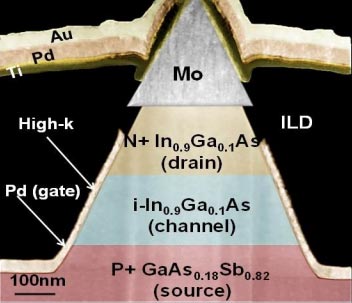

ä▌Pennsylvania State Universityż╚ä▌NISTĪ╩µ£ä▌║YØŹČ\ĮčĖ”ē|ĮĻĪ╦Īó▒čIQEżŽĪóź©ź═źļź«Ī╝ź«źŃź├źūż“╩°ż╣żĶż”ż╩TFETż╦ż─żżżŲĮęż┘ż┐ĪŻż│ż╬ź╚źķź¾źĖź╣ź┐żŽĪó┐═öüż╦ļmżß╣■żÓż│ż╚ż╬żŪżŁżļ░Õ┬äźŪźąźżź╣├ōż╦│½╚»żĄżņż┐ĪŻź©ź═źļź«Ī╝ź«źŃź├źūżŽĪóż█ż▄ź╝źĒżóżļżżżŽźųźĒĪ╝ź»ź¾ź«źŃź├źūż╦ŖZżżż╚żĘżŲżżżļĪŻ┼┼╗ęż¼źąźĻźóż“Ų═żŁģsż▒ź╚ź¾ź═źĻź¾ź░żĘżõż╣ż»ż╣żļż┐żßż└ĪŻż│ż╬TFETżŽāeöĄĖ■ż╦┼┼╬«ż“╬«ż╣╣Įļ]ż└ż¼Īó├╝╗꿎µ£żŲ╔ĮĀCż½żķŲDżĻĮąż╗żļżĶż”ż╦żĘżŲżżżļ(┐▐1)ĪŻInGaAs/GaAsSbÅUż╬III-V╠öź╚źķź¾źĖź╣ź┐ż“ź┘Ī╝ź╣ż╚żĘżŲżżżļĪŻź┴źŃź═źļ─╣200nmż╬źųźĒĪ╝ź»ź¾ź«źŃź├źūTFETżŽĪó740µA/µmż╚╣ŌżżŅ~Ų░┼┼╬«ż“įużŲżżżļĪŻRF┴ĻĖ▀ź│ź¾ź└ź»ź┐ź¾ź╣żŽ700µS/cmż╚╣Ōż»Īó╝ūéā╝■āS┐¶żŽVDSĪß0.5VżŪ19GHzżŪżóżļĪŻ

┐▐1ĪĪāeĘ┐TFETż╬TEMĪ╩Ų®āįĘ┐┼┼╗ęĖ▓╚∙¬ÜĪ╦└^┐┐ĪĪĮąųZĪ¦ Suman DattaĢ■ĪóPennsylvania State University

Īųż│ż╬ź╚źķź¾źĖź╣ź┐żŽ┼÷Ė”ē|ĮĻżŪ│½╚»żĘż┐ĪŻźĒźĖź├ź»LSI├ōż╬MOSFETż“ÅøżŁ┤╣ż©ĪóŠ├õJ┼┼╬üż╬╠õ¼öż“▓“»éżĘżĶż”ż╚żżż”┴└żżżŪżóżļĪŻ║Żövż╬╗Ņ║ŅżŪ╣Ō╝■āS▒■├ōż╬▓─ē”└Łż¼▐k╩Ō┐╩ż¾ż└ż╚Ė½żŲżżżļĪŻ┐═öüż╦ļmżß╣■żÓ├ō²ŗżŪźŪĪ╝ź┐ż“ĮĶ═²żĘ┴„┐«ż╣żļż╚żżż├ż┐─ŃŠ├õJ┼┼╬üż╬▒■├ōż╦╗╚żżżõż╣ż»ż╩żļĪūż╚PennsylvaniaĮjż╬Įj│ž▒ĪÖ┌ż╬Bijesh RajamohananĢ■żŽŲ▒Įjż╬ź”ź¦źųźĄźżź╚żŪĮęż┘żŲżżżļĪŻ

żŌż”1°PĪóIEDMżŪż╬ų`Č╠żŽĪóIntelż¼Č”╠─ź╚ź¾ź═źļFETĪ╩R-TFETĪ╦ż“╚»╔ĮżĘż┐ż│ż╚ż└ĪŻż│ż╬źŪźąźżź╣ż╬źĄźųź╣źņź├źĘźńźļź╔┼┼╬«ż╬’łżŁżŽĪó3ĘÕż╬┼┼╬«šJ░Žż╦┼Žż├żŲ25mV/ĘÕż╚ŠåĮįżŪżóżļĪŻż│żņż╦żĶż├żŲź▓Ī╝ź╚─╣ż¼9nmż“└┌żļTFETż╦ź╣ź▒Ī╝źĻź¾ź░żŪżŁżļż╚ż╣żļĪŻ

ż│ż╬R-TFETżŽĪóIntelż╬ź└źųźļź▓Ī╝ź╚źžźŲźĒ└▄╣ńTFETż╚Ų▒══ż╬║Ó╬┴ż╬┴╚ż▀╣ńż’ż╗ż“╗╚ż”ĪŻĪųnź┴źŃź¾ź═źļTFETż╬źĮĪ╝ź╣ōļ░Ķż╦┼┴Ų│┬ėż╬─Ńżżź©ź├źĖż“Ęeż─║Ó╬┴ż¼żóżļĪŻż│ż╬źąź¾ź╔ż╬Ū█š`ż╦żĶż├żŲĪóČ╣żżįÆ│čź▌źŲź¾źĘźŃźļ░µĖ═ż¼źžźŲźĒ└▄╣ńż╬źĮĪ╝ź╣ź©ź├źĖż╦Įą═ĶżļĪŻż│ż╬░µĖ═Ę┐ź▌źŲź¾źĘźŃźļżŽ▀`Üg┼¬ż╩Č”╠─ź©ź═źļź«Ī╝ØŹ░╠ż“Ęeż─ĪŻ╚ŠĖ┼ųZ┼¬ż╩Ė½öĄż“ż╣żļż╩żķĪóż│ż╬└▀╝ŖżŽź╚ź¾ź═źĻź¾ź░ż╣żļż┐żßż╬╝┬Ė·┼¬ż╩źąź¾ź╔ź«źŃź├źūż¼╗\ż©żļż╬żŪĪóTFETż╬Ņ~Ų░┼┼╬«ż“▓╝ż▓żļż│ż╚ż╦ż╩żļĪūż╚Intelż╬Ė”ē|ŪvżŪżóżļUygar AvciĢ■ż╚Ian YoungĢ■żŽĖ└ż”ĪŻ

Īųż│ż╬Č”╠─ź©ź═źļź«Ī╝ØŹ░╠ż¼źĮĪ╝ź╣ż╬▓┴┼┼╗ę┬ėźņź┘źļż╦▐k├ūżĘż┐ż╚żŁż└ż▒ĪóźŪźąźżź╣żŽź¬ź¾ż╣żļĪŻż│ż╬ż┐żßĪ󟬟¾ż╚ź¬źšż╬ōļ░Ķ┤ųż“ź╚ź¾ź═źļż╣żļ│õ╣ńż¼╣ŌÅ]ż╦╩č▓Įż╣żļĪŻż│ż╬±T▓╠ĪóR-TFETżŽĪóźžźŲźĒ└▄╣ńTFETżĶżĻżŌŠåĮįż╩źĄźųź╣źņź├źĘźńźļź╔┼┼╬«ż¼įużķżņżļż╚żżż”Ślż└Īūż╚Įęż┘żŲżżżļĪŻ

śOĖ╩┴╚“E▓ĮReRAM

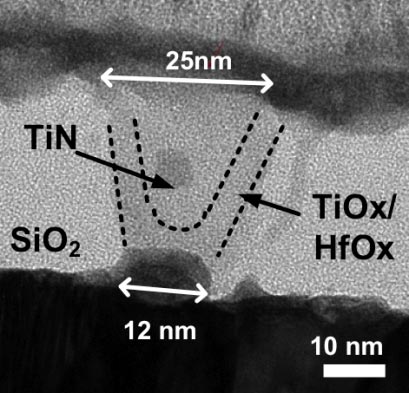

°BŃ^╩č▓ĮźßźŌźĻReRAMżŽźšźķź├źĘźÕźßźŌźĻż“ÅøżŁ┤╣ż©żĶż”ż╚żĘżŲ│½╚»ż¼īÖ╚»ż└ĪŻNANDźšźķź├źĘźÕż╚╚µż┘Į±żŁ┤╣ż©╗■┤ųż¼ø]ż»ĪóĮ±żŁ┤╣ż©öv┐¶żŌ¾Hżżż╚Ė└ż’żņżŲżżżļĪŻIEDMżŪżŽĪó¾Hż»ż╬ReRAMż╬╚»╔Įż¼żóż├ż┐ĪŻ├µżŪżŌStanfordĮj│žżŽźßź┐źļ-¤©▓Į╦ņReRAMźŪźąźżź╣ż╦ż─żżżŲ╚»╔ĮżĘż┐ĪŻż│ż╬źßźŌźĻżŽĪóźĖźųźĒź├ź»Č”─_╣ńöüż╦żĶżļśOĖ╩┴╚“E▓ĮźūźĒź╗ź╣ż“╗╚ż├żŲ×æļ]żĄżņżŲżżżļĪŻż│ż╬źčź┐Ī╝ź╦ź¾ź░Č\Įčż“╗╚ż©żąĪóż│ż╬źßźŌźĻźŪźąźżź╣ż“12nm░╩▓╝ż╦╚µ╬ŃĮ╠Š«żŪżŁżļĪŻ2┴žż╬TiOx/HfOxźŪźąźżź╣(┐▐2)ż“╗Ņ║ŅżĘĪó2.5VżŪĮ±żŁ╣■ż▀ĪóżŌż├ż╚─Ńżż┼┼░ĄżŪź╣źżź├ź┴ź¾ź░Ų░║ŅżĄż╗Īó10ż╬7ŠĶövż╬Į±żŁ┤╣ż©öv┐¶ż“įużŲżżżļĪŻź╣źżź├ź┴ź¾ź░Å]┼┘żŽ50nsż╚żĘżŲżżżļĪŻ

┐▐2ĪĪDSAźūźĒź╗ź╣żŪ║Ņ×æżĄżņż┐ReRAMźŪźąźżź╣ĪĪĮąųZĪ¦Stranford University

StanfordĮjż╬śOĖ╩┴╚“E▓ĮźūźĒź╗ź╣żŪżŽĪóźĖźųźĒź├ź»Č”─_╣ńöüż╬PS-b-PMMAżŽĪóźūźĒźįźņź¾ź░źĻź│Ī╝źļźßź┴źļź©Ī╝źŲźļźóź╗źŲĪ╝ź╚ż╦═Žż▒żļĪŻ╗Ņ╬┴ż“├Ō┴Ū╩Ę░ŽĄż├µĪó185ĪŅżŪ12╗■┤ųźóź╦Ī╝źļż╣żļż╚śOĖ╩┴╚“E▓ĮżĘżõż»ż╩żļĪóż╚Ų▒ĮjżŽĮęż┘żŲżżżļĪŻż│ż╬ĖÕĪó╗Ņ╬┴ż“DUVĪ╩▒¾╚Ø│░Ė„Ī╦żŪ10╩¼┤ųŽ¬Ė„żĘĪóĢ±┐▌¤©ż╦20╩¼┤ų┐╗ż╣ĪŻPMMA└«╩¼ż“┬ō┘I┼¬ż╦Į³ĄŅż╣żļż│ż╚żŪĪó─ŠĘ┬20nmż╬ĘĻż¼╩┬ż¾ż└ż│ż╬PSźŲź¾źūźņĪ╝ź╚ż¼įużķżņżļĪŻż│ż╬PSźŲź¾źūźņĪ╝ź╚żŽź©ź├ź┴ź¾ź░├ōż╬ź▐ź╣ź»ż╦ż╩żļż╚żżż”ĪŻĪųźĖźųźĒź├ź»Č”─_╣ńöüż╦żĶżļśOĖ╩┴╚“E▓ĮźūźĒź╗ź╣żŽĪó“£═Ķż╬źĻźĮź░źķźšźŻČ\ĮčżĶżĻżŌżŌż├ż╚Ė·╬©żĶż»ĪóŖW▓┴ż╦ź╩ź╬ź╣ź▒Ī╝źļż╬ź┴ź├źūż“×æļ]żŪżŁżļż└żĒż”Īūż╚StanfordĮj│ž┼┼Ąż╣®│ž▓╩ż╬H.-S. Philip WongČĄĶbżŽŲ▒Įjż╬ź”ź¦źųźĄźżź╚żŪĮęż┘żŲżżżļĪŻ

FinFET×┤FD-SOI

Intel░╩│░ż╬ĮjŠ}╚ŠŲ│öüźßĪ╝ź½Ī╝żŽĪó20nm░╩æTż╬źĒźĖź├ź»ź╬Ī╝ź╔żŪżŽżĄż▐żČż▐ż╩ź¬źūźĘźńź¾ż“─┤ż┘żŲżżżļĪŻ16nm/14nmź╬Ī╝ź╔żŪżŽĪ󊻿╩ż»ż╚żŌŲ¾ż─ż╬ĮjżŁż╩┬ō┘I╗Ķż¼żóżļĪŻfinFETż½ĪóFD-SOIĪ╩Fully depleted silicon on insulatorĪ╦źūźņĪ╝ź╩MOSFETż½Īóżżż║żņż½ż└ĪŻIEDMżŪżŽĪóTSMCż¼16nmż╬finFETźūźĒź╗ź╣ż╦ż─żżżŲĮķżßżŲĮęż┘ż┐ĪŻSTMicroelectronicsż╚CEA-LetiĪóźļź═źĄź╣ĪóGlobalFoundriesĪóSoitecżŽFD-SOIż╦┤žż╣żļ╚»╔Įż“╣įż├ż┐ĪŻż│żņżŽ14nmź╬Ī╝ź╔░╩æTż╦Ė■ż▒ż┐ź▓Ī╝ź╚─╣20nmż╬źŪźąźżź╣żŪżóżļĪŻ

żĮż╬▐kŗż╚żĘżŲĪóTSMCż╬16nm finFETČ\ĮčżŪżŽĪó0.07╩┐öĄź▀ź»źĒź¾ż╬SRAMż╚Cu/low-kŪ█└■Īóhigh-kźßź┐źļź▓Ī╝ź╚ż╩ż╔ĪóźŌźąźżźļSoCżžż╬▒■├ōż“£å╠Ņż╦Ų■żņżŲżżżļĪŻTSMCż╦żĶżļż╚Īóż│ż╬ź╚źķź¾źĖź╣ź┐żŽĪó30mV/V╠ż╦■ż╬DIBLżŪø]ź┴źŃź¾ź═źļĖ·▓╠ż“═▐ż©ĪónMOS/pMOSż╚żŌĪó0.75VżŪ520/525µA/µmż╬ź╔źņźżź¾┼┼╬«Idsatż“Ęeż┴Ī󟬟š┼┼╬«IoffżŽ30pA/µmż╚żżż”ØŖ└Łż“Ęeż─ĪŻ

Finż╬źčź┐Ī╝ź╦ź¾ź░ż╚48nm finźįź├ź┴ż╬źąźļź»CMOSżŽĪóźįź├ź┴Ī”ź╣źūźĻź├źŲźŻź¾ź░ż╚żżż”źĻźĮź░źķźšźŻČ\Įčż“╗╚ż├żŲ×æļ]żĘż┐ż╚żżż”ĪŻż│ż╬źčź┐Ī╝ź╦ź¾ź░Č\ĮčżŪ64nmż╬źßź┐źļźįź├ź┴ż“▓─ē”ż╦żĘż┐ĪŻ

FD-SOIż╦┤žżĘżŲżŽĪóSTMicroelectronicsż╩ż╔ż¼20nmź▓Ī╝ź╚ż╚25nmĖ³ż╬BOX¤©▓Į╦ņż“╗╚ż├ż┐UTBBĪ╩ultra-thin body and boxĪ╦źŪźąźżź╣ż“╚»╔ĮżĘż┐ĪŻż│ż╬Č\Į迎Īónź┴źŃź¾ź═źļMOSż╦żŽźĘźĻź│ź¾Īópź┴źŃź¾ź═źļMOSż╦żŽSiGeź┴źŃź¾ź═źļż“ŠW├ōż╣żļźŪźÕźóźļź┴źŃź¾ź═źļFETż¼ØŖ─╣ż└ż╚żĘżŲżżżļĪŻ╝┬Ė·┼┼╬«IeffżŽnMOS/pMOSżŪżĮżņżŠżņ630/670µA/µmĪ󟬟š┼┼╬«IoffżŽVdd0.9VżŪ100nA/µmĪŻĪųź┴źŃź¾ź═źļż╦Ž─ż▀ż“Ų│Ų■żĘĪóRDSź©źįź┐źŁźĘĪ╝ż╚└▄╣ń┐╝żĄż“║Ū┼¼▓Įż╣żļż│ż╚żŪĪó╣Ō└Łē”ż╩ŗī2└ż┬Õż╬UTBBźŪźąźżź╣ż“│½╚»żŪżŁż┐ĪŻż│żņż╦żĶżĻ14nmżžź╣ź▒Ī╝źĻź¾ź░żŪżŁżļĪūż╚STMicroelectronicsż╬Qing LiuźĘź╦źóź╣ź┐ź├źšź©ź¾źĖź╦źóżŽĖņż├żŲżżżļĪŻ

Mark LaPedus,ĪĪSemiconductor Engineering (http://semiengineering.com/)